Just for fun, one of the examples is simulating a 6502 processor (written in verilog) which is running a "Hello World" program.

0%

0%

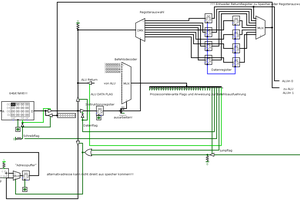

DigSim - Interactive Digital Logic Simulator

An interactive python based simulator for digital designs (including verilog)

Fredrik Andersson

Fredrik Andersson

John Duffy

John Duffy

Kara Abdelaziz

Kara Abdelaziz