-

1st fix for badge Verilog

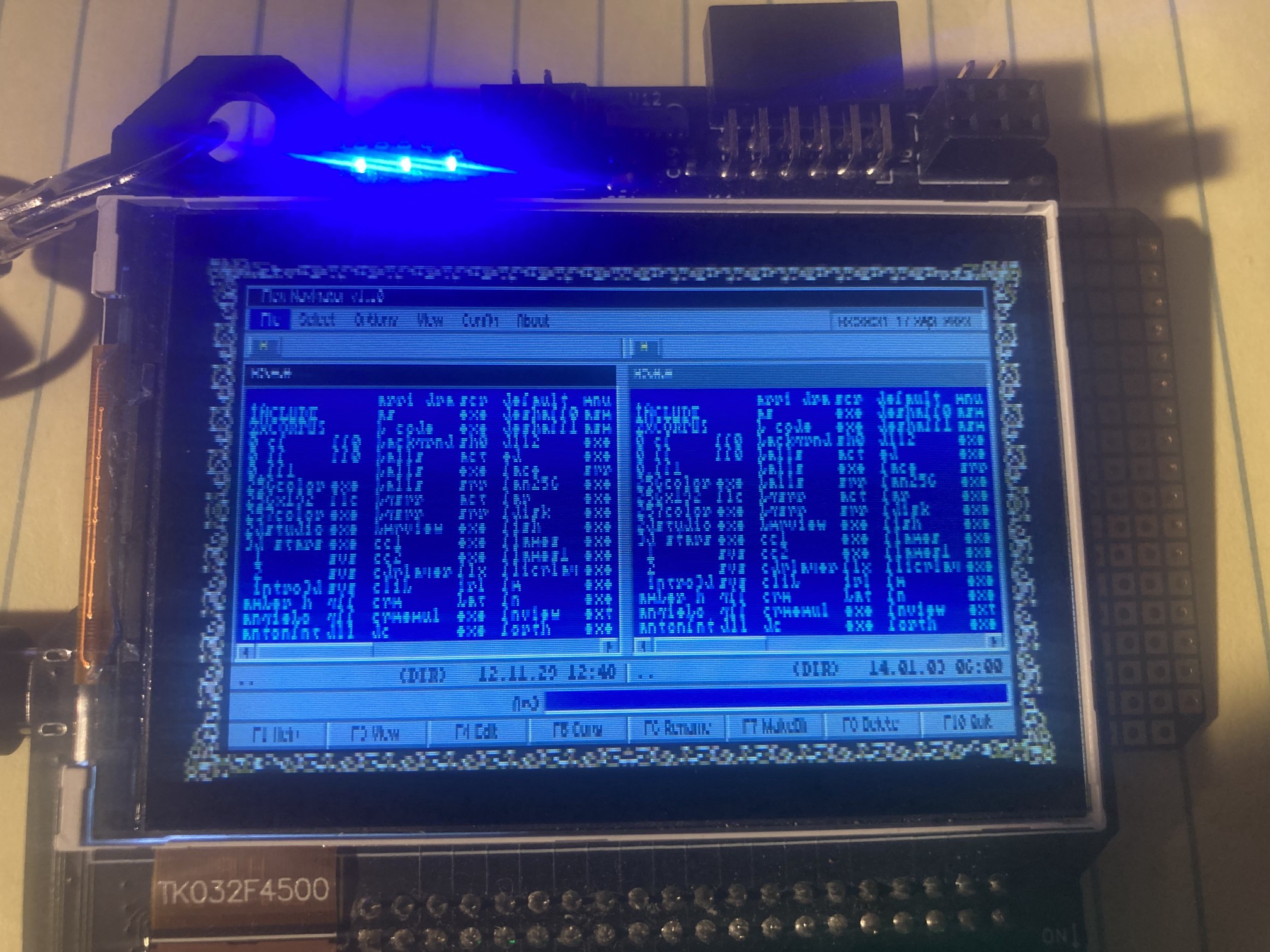

10/06/2023 at 05:58 • 1 commentExisting SOC verilog has an issue with framebuffer graphics - it's showing only EVEN lines (twice each) and ignoring ODD lines:

![]()

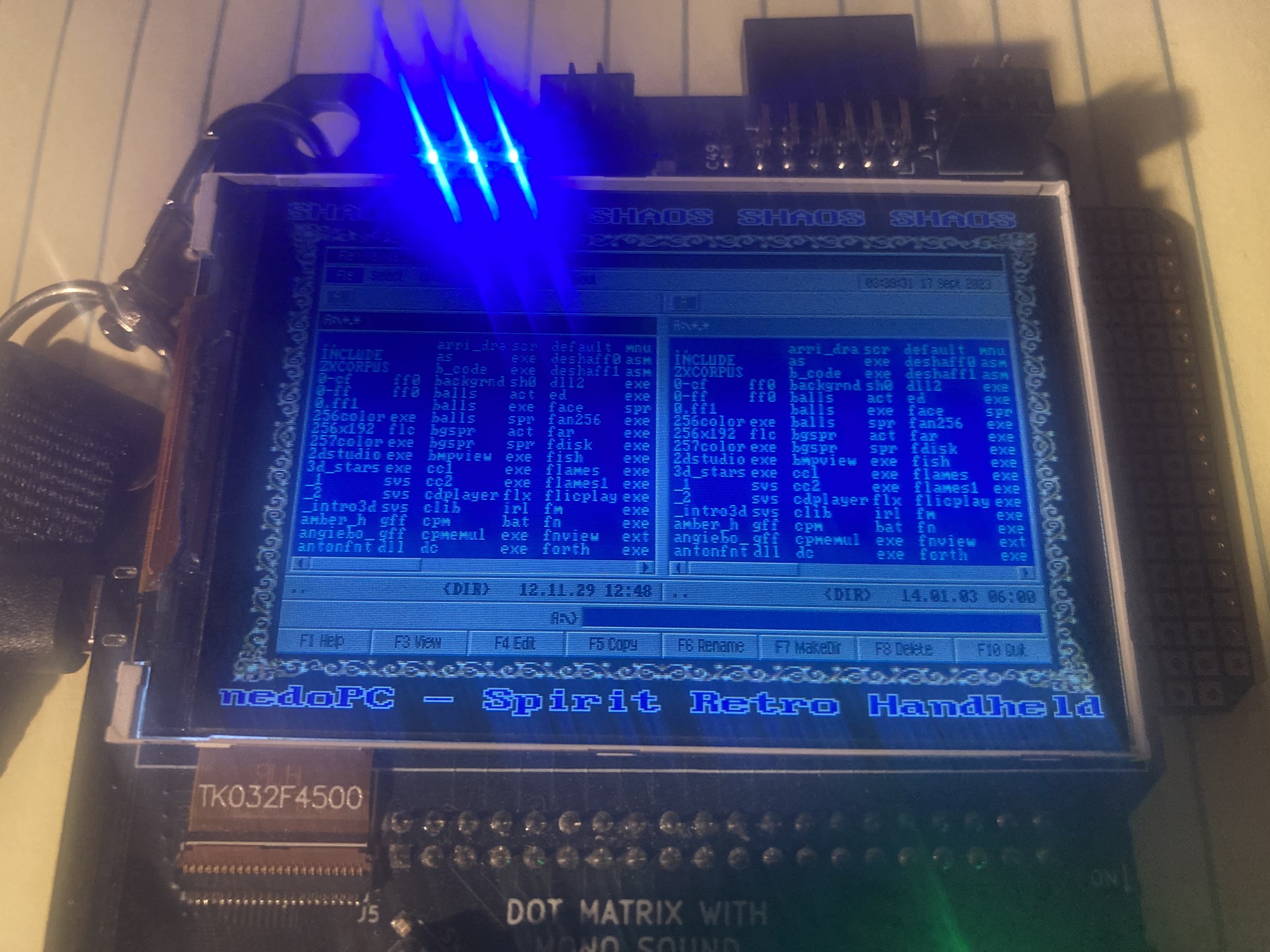

Fixed SOC shows it like this:

![]()

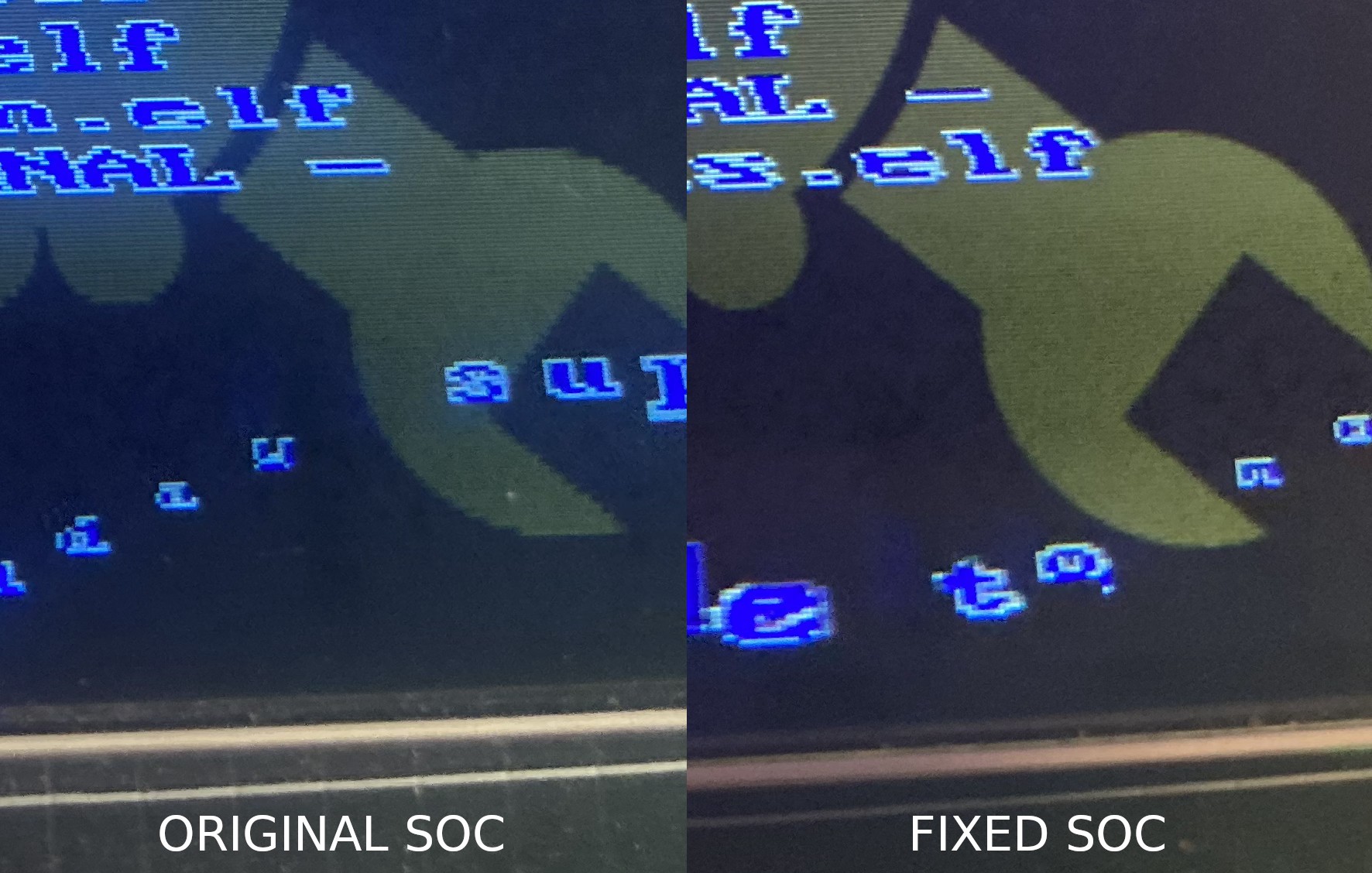

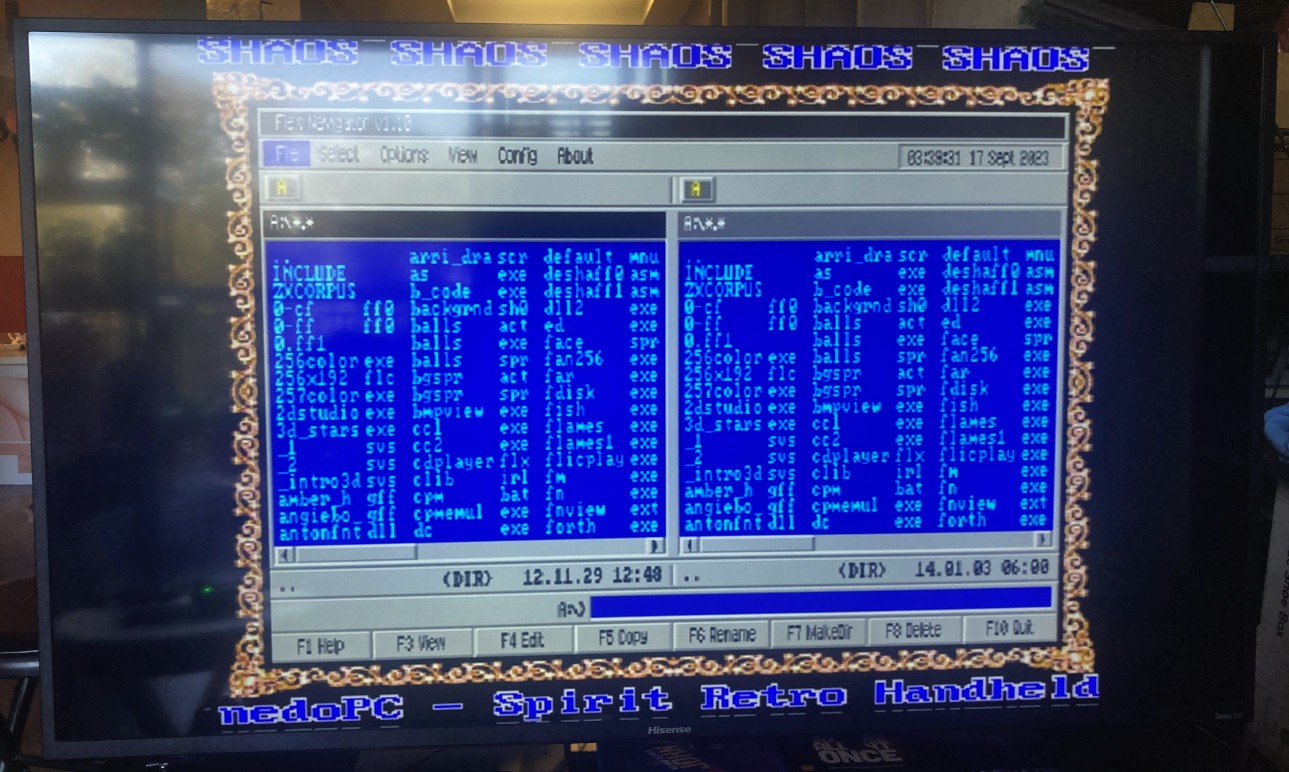

Before and after on existing program:

![]()

This is a PR: https://github.com/Spritetm/hadbadge2019_fpgasoc/pull/155

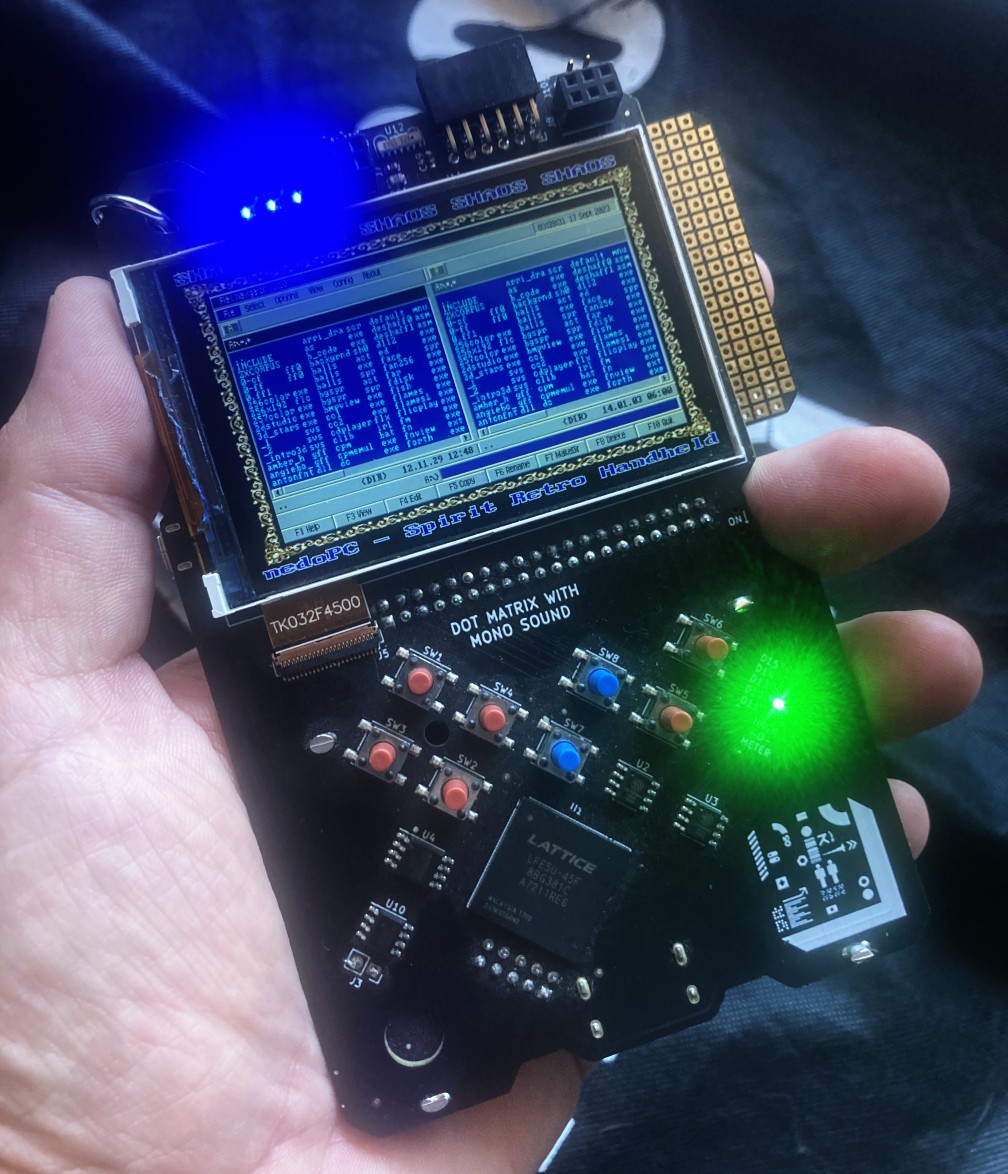

Pull request also has a program that showing this image:

![]()

Image itself is 16-color 736x288 and program takes 720x288 part of it and "squeezes" it into screen 480-pixel width using generated 256-color palette, that helps to represent THREE 16-color pixels as TWO 256-color pixels using this formula for every color channel NEWCOLOR = (C1 + 0.5 * C2)/1.5 (in more sophisticated way for speed).

And this also fixes HDMI output (that looks a little worse than screen on the badge because of upscaling):

![]()

Spirit Retro Handheld

Attempt to add even more Retro Spirit to Hackaday Supercon'19 badge :)

SHAOS

SHAOS