The format is now set to 20-bit frames that contain 16 bits. The overhead is 25% like 100BaseT but with increased error detection and wander reduction.

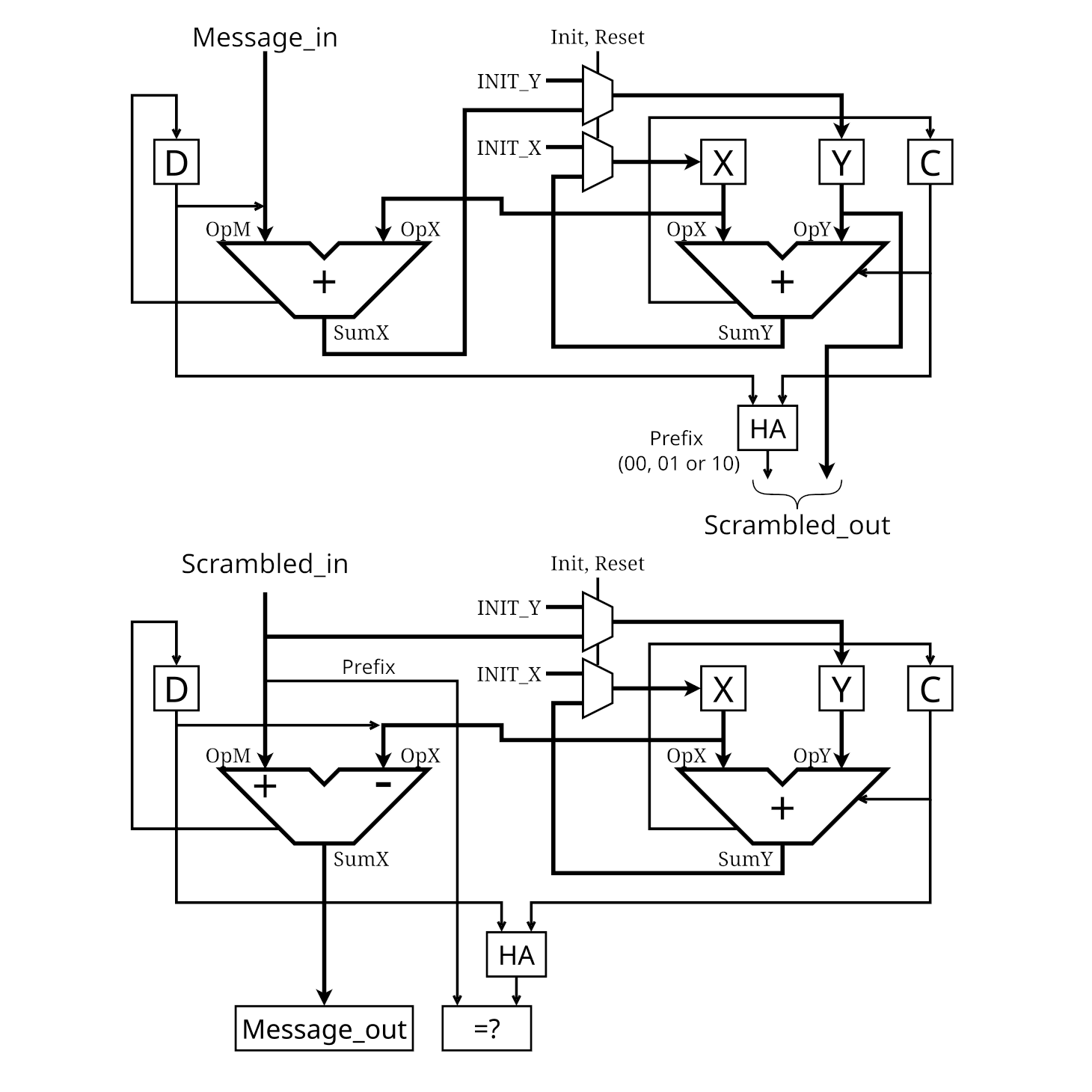

The 16 bits are processed with PEAC16, as per the diagram below

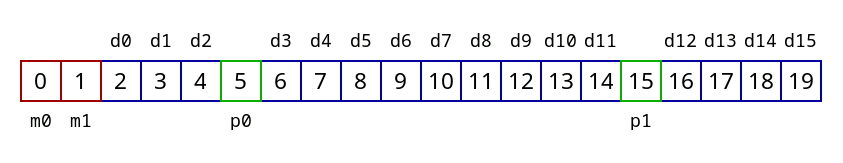

A different PEAC flavour is under consideration but the principle remains the same : the 16 bits (d0..d15) are extended to 18, with the extra 2 bits as markers (m0, m1).

2 more bits (p0, p1) are added as even parities : that's a total of 20 bits.

The key property of PEAC is that the whole message can never be all-0 or all-1.

In any case, m+d always have at least 1 bit set and 1 bit cleared.

The parity bits ensure that the whole frame has a "Return To Neutral" behaviour, though it does not remove all wander.

There are 2 parity bits, so 2 choices depending on the m+d parity:

- 00 or 11 if the packet is even

- 10 or 01 if the packet is odd.

One approach to reduce wander is to "break" long strings of identical values when they are +1 or -1. The parities are placed at 1/4th and 3/4th of the frame for maximum reach, as well as overlap with the previous and next words. It is important to provide a strong, strict bound on the maximum run length of 0s.

The parity bits are checked by the receiver but the actual parity pattern is a degree of freedom chosen by the encoder to reduce wander. It is there to provide a garantee that at least 2 transitions will occur in each frame.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.