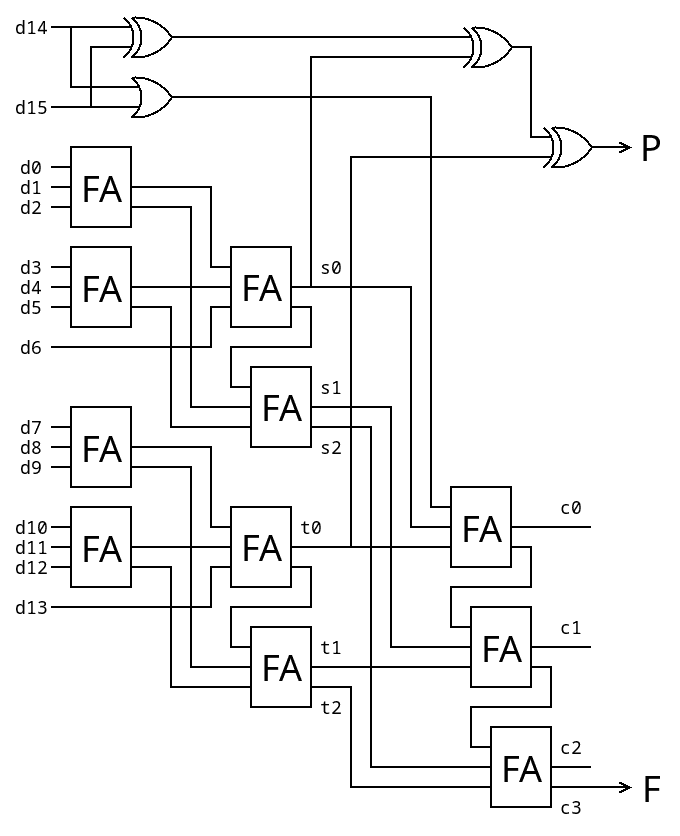

Since the last log mentioned that the exact number of set bits is not critical, the popcount circuit can be simplified: only three layers of adders are required!

The trick: input bits d14 and d15 are ORed to provide the carry-in of the last layer, which only provides 4 bits.

It does not really matter if the number of set bits is 15 or 16, but 16 requires 5 bits, which would add an extra layer of adders for nothing.

Intermediary results c0, c1 and c2 are discarded. C1 could be used to estimate the "phase" (state of the MLT3 at the end of the frame) but it's incomplete. And since c0/c1/c2 are not used, the FA block can be replaced by a "MAJ3" gate.

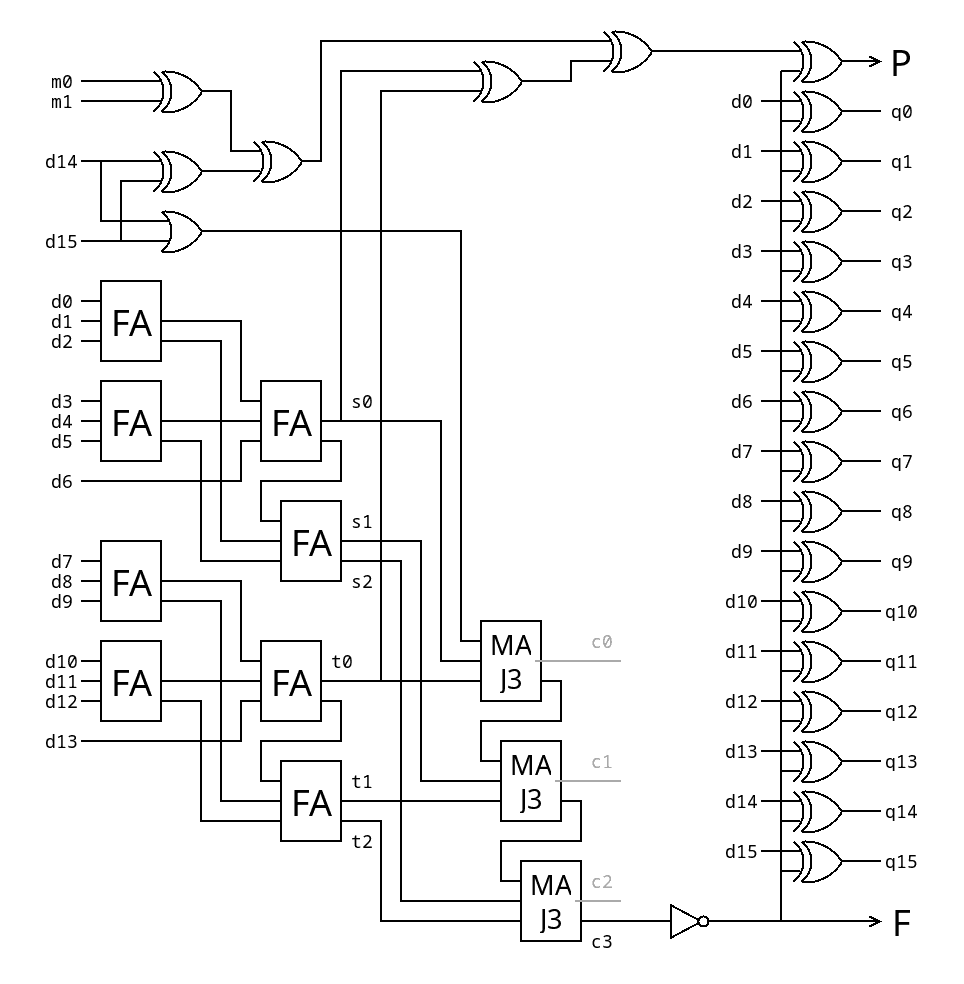

Not represented here : the parity circuit for marker bits m0 and m1, here is a more complete version:

Not trivial but still reasonable. That's fewer Full Adders than usual, see for example http://www.righto.com/2016/01/counting-bits-in-hardware-reverse.html.

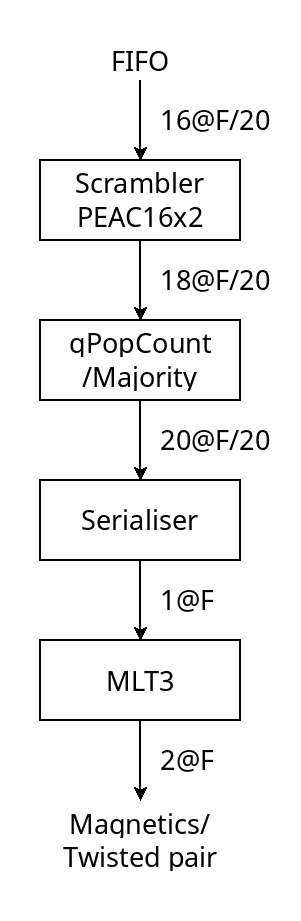

The whole pipeline looks good too:

Note how the first two stages work at quite low speed, then speed up at the serialiser.

PEAC16×2 could work at 2× speed and implement byte-wide sub-computations but the gains (speed, surface) are not compelling, as complexity increases. And slower circuits consume less.

The pipeline could be reused, without the MLT3, for inter-chip or inter-board communications, over a balanced pair maybe. Resynchronisation is a whole different subject though.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.