If the Parpop and PEAC units can be bidirectional then they can be shared between the sender and receiver channel, if the speed allows it.

For a 50MHz PEAC unit (a pretty conservative speed in FPGA), the unit pumps one word per 20ns, then the multiplexing halves the speed down to 25MHz but that's still 25×20=500Mbps in both directions. And there is some margin !

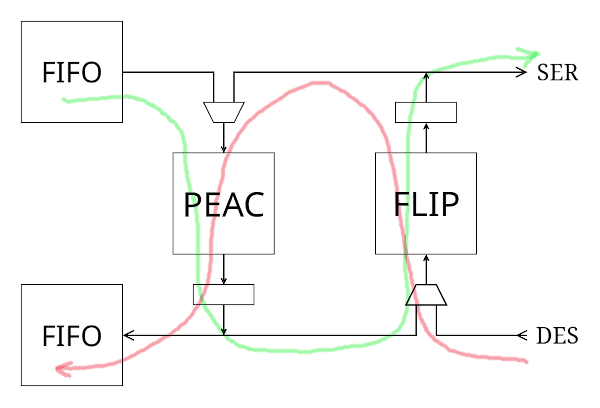

What does it look like ?

Both units have their output pipelined, and inputs have a single multiplexer. This is a reasonable overhead though the PEAC unit needs 2 sets of work registers, to alternate the functions. It's still less than a full register set...

Scheduling is rather simple, at least with the simple version of PEAC :

- First phase, PEAC scrambles data for the transmitter and the ParPop flips the received data

- Second phase, PEAC descrambles the received data while ParPop encodes the data to send.

Both units are working all the time, on different data, it's far from a complex FSM.

Yet, using a specialised unit for each function is simpler, so multiplexing is beneficial when resources are really constrained, and when DFF are not expensive (as in a small FPGA). A full custom chip will need some prototyping and comparisons, since the extra MUX and control logic can easily compensate the surface reduction of using only 2 units instead of 4.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.