Now we're speaking. Simulate by yourself with CircuitJS :

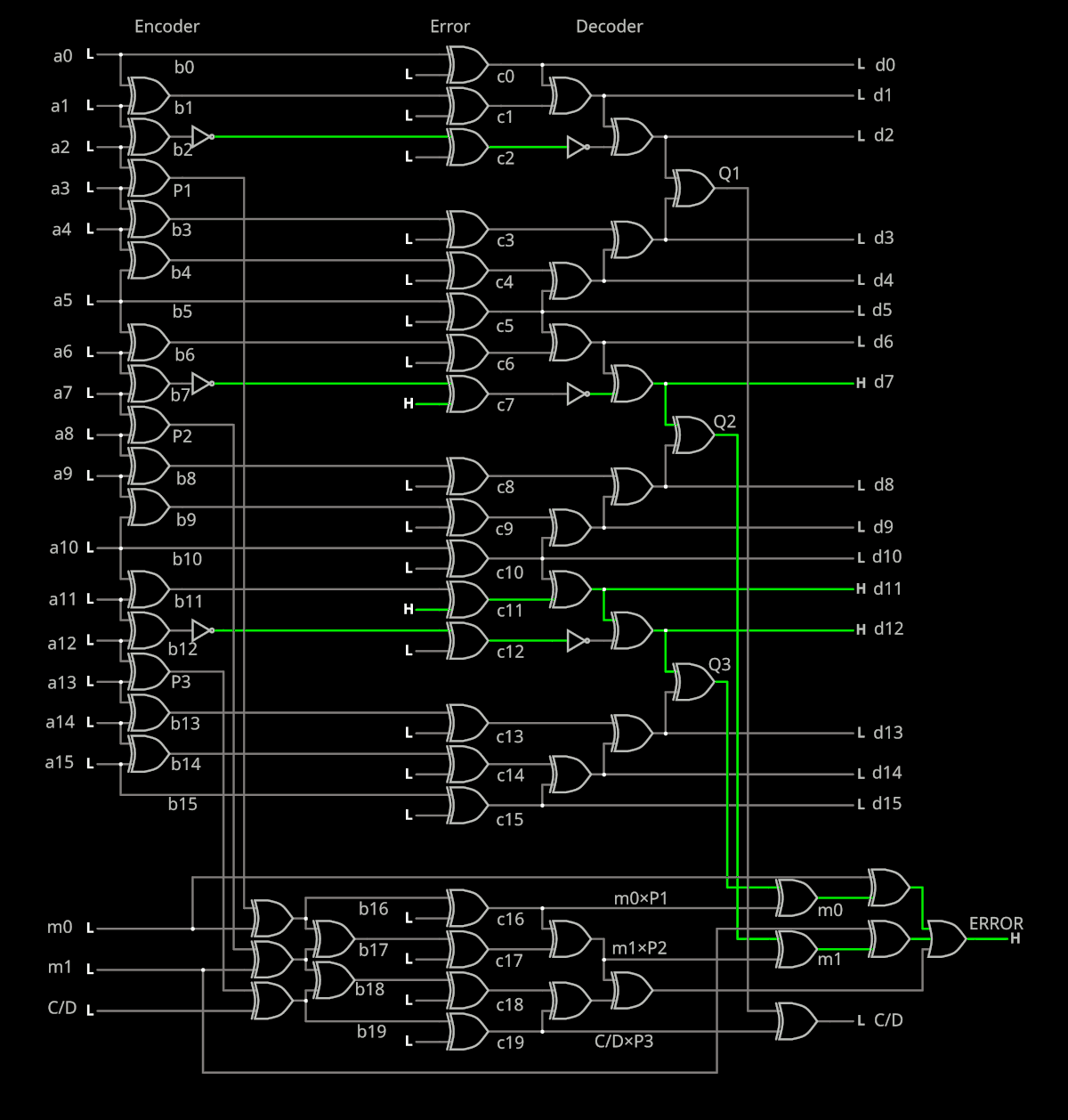

The main ideas of the previous log are there, but an extra trick is pulled: there are 3× 6-bit parity blocks, but they are merged! This makes a5 and a10 having effect on 3 pins and 2 separate parities each. The word can take some combinations of even numbers of bits without difficulty. And in case of missed error, PEAC does the rest, benefitting from the shuffled and amplified errors.

Note : Control words need specific values so P1/Q1 is cleared. In return control words can use m0 and m1 for extra data.

The gates count and the critical datapath are very efficient:

- Encoder: 20gates, depth=3 gates depth

- Decoder: 24 gates, max depth=6 gates. Actually, it depends on when m0/m1 are available.

It's going to run fast and there is no need of a reversed version.

Next, the shuffling of the bits inside the 20-bit word.

.....

Addendum : I should have inverted b17 or b18.

.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.