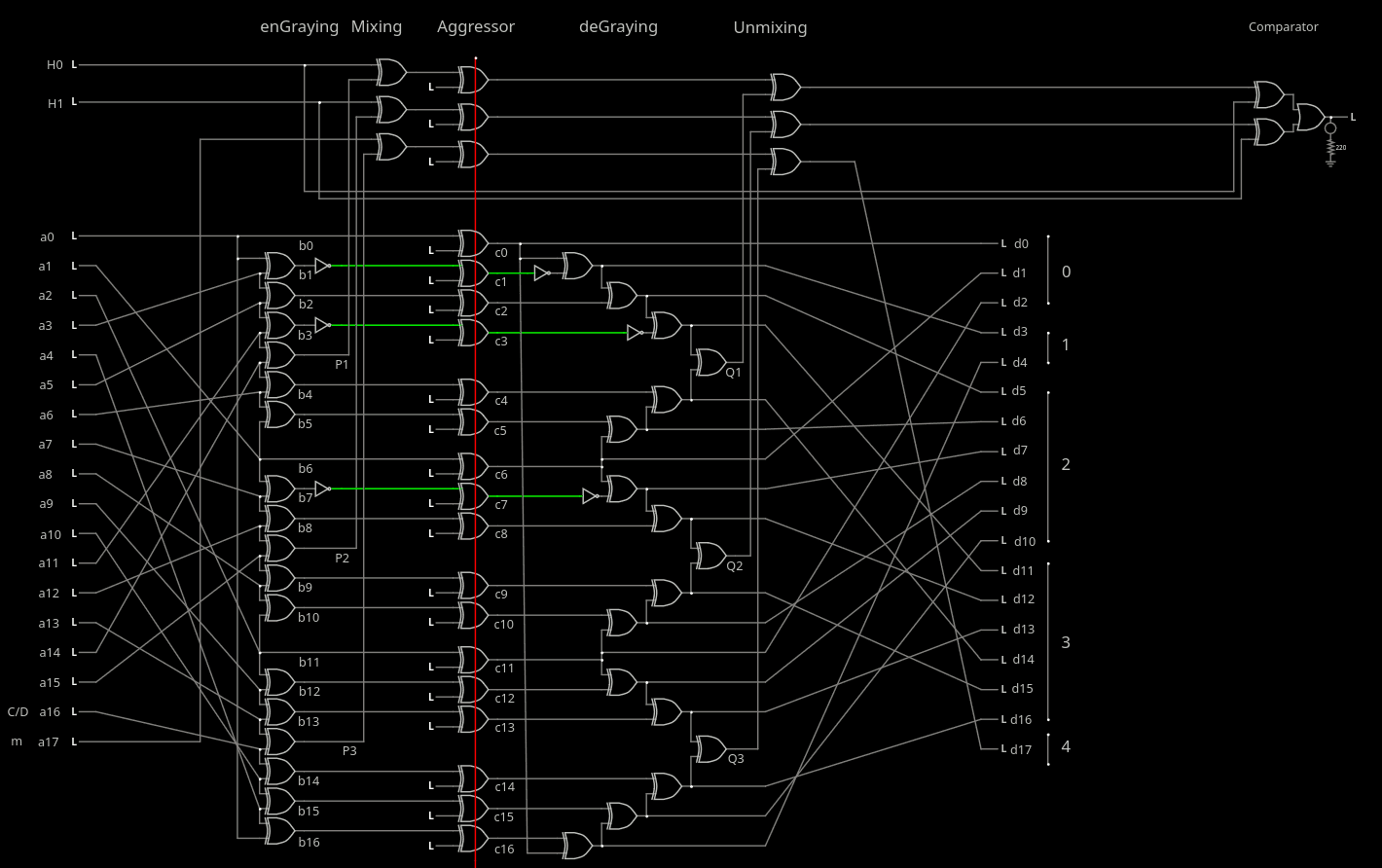

Following the log 82. Unit swap (2), here is the new version of GrayPar18.

- The good: the V are merged with the adder thanks to bit shuffling, proportional to the logic depth, which is compatible with a segmented Carry Lookahead Adder. So no need of a dedicated clock cycle.

- The less good: it appears that the parity is reduced from 3 to 2 bits. The 3rd bit is still somehow there but not explicitly and actual measurements will confirm its presence. The gPEAC must verify that the data are valid during modulo, to recover some of the error detection capacity.

Not shown: the parity circuits.

Note that the data is "doubly" protected:

- the parity of the original 16+1=17-bit word is spread over H0 and H1

- the word is then processed by gPEAC and then GrayPar18, ensuring maximal avalanche for most errors and strong decoupling between the original data and the encoded data, removing concerns about error cancellations.

The worst cases for the odds of missed error:

- 1/1000 : 5 words

- 1/1M : 10 words

- 1/1B : 15 words.

Overall, the latency/cost of the GrayPar has been almost reduced to 0, with the integration of the Vs in the adder's carry chain, and it adds valuable extra protection and resilience.

The 4B3T encoding and shuffling further increases the confusion-diffusion, ensuring that no error can be ignored.

.......................................

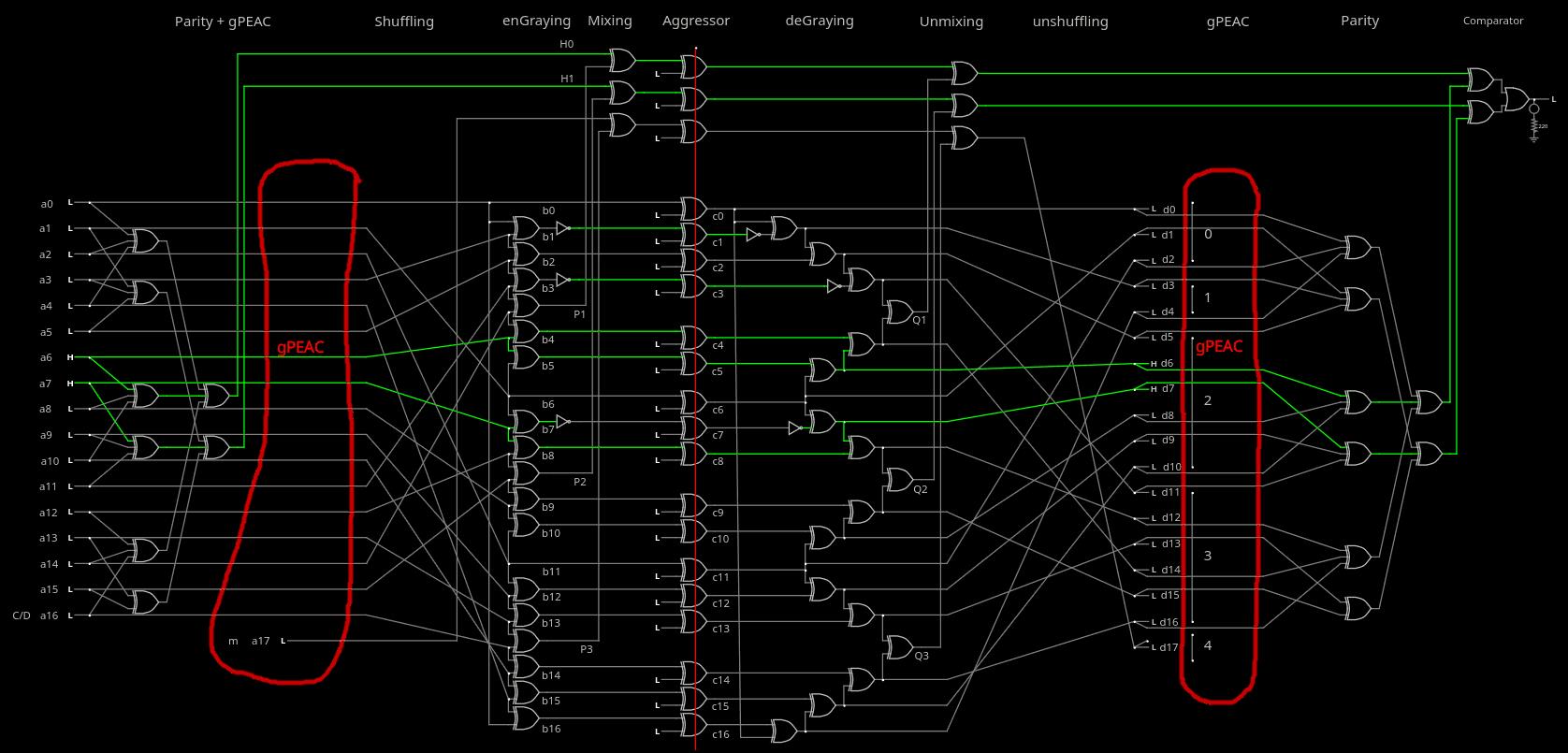

Update : this diagram is more complete.

Here the gPEAC (red blobox) is pass-through for simplicity.

Parity is computed in parallel/simultaneously with gPEAC during encoding, but after gPEAC descrambling, so it's another critical circuit (latency-wise).

Thus now parity is reduced only to the input and output of data/payload because it's mixed with X & Y by gPEAC, no need to overdo it.

This might increase the detection latency slightly (possibly by one word in average) but general circuit speed and size is more important, at this level.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.