The last log 101. gPEAC: the circuit has a little flaw...

Test.

Test early.

Test often.

Some tests have reminded the importance of the carry and the updated algorithm is

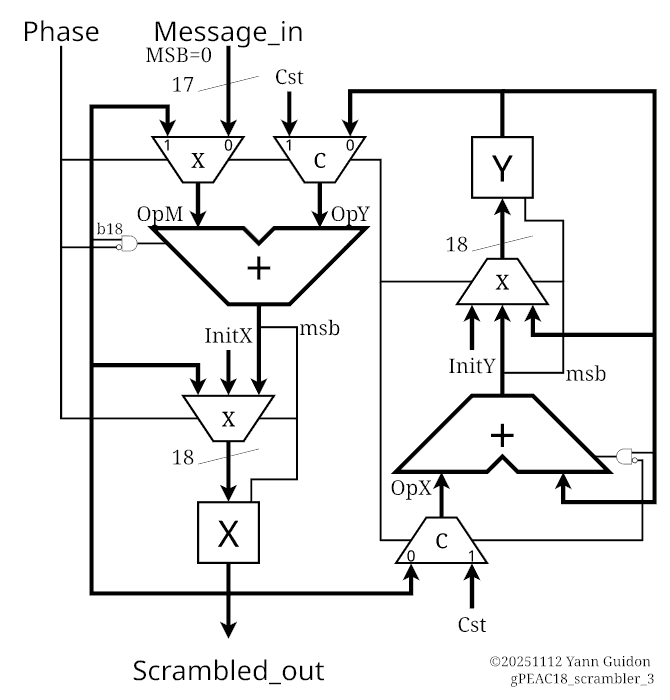

Phase0: accumulation X[18:0] := Msg[17:0] + Y[17:0] + X[18] Y[18:0] := X[17:0] + Y[17:0] + Y[18] Phase1: modulo t[18:0] := X[18:0] + Cst u[18:0] := Y[18:0] + Cst X[18]:=t[18] if t[18]==1, X[17:0]=t[17:0] Y[18]:=u[18] if u[18]==1, Y[17:0]=u[17:0]

so the carry still exists as the MSB of X and Y, which is always written and selectively used, depending on the phase.

Thus the requirement/format for the adder is : 19 bits with carry input (still no carry out, it's the MSB).

The diagram is updated:

Fortunately, the implementation has only been in high level so far, indeed to verify the long-term behaviour. Without this carry, the cycles are very short.

.

Another big problem :

The system loops after 32.315.302.423 iterations only !

The modulus is maximal but not perfect !

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.