For this project I want to use the 12.5MHz 4-channel HD63450 DMA Controller.

MC68450/HD68450

The original MC68450L is a large, complex and expensive chip that is severely pin-constrained in the original DIP64 package. Significant external logic is required to demultiplex and control the bus, which had been avoided in the 68000 using the same package.

The 68450 is more space-efficient in the 68pin PGA package which uses up about 1/3 the board space (but still needs the support logic) :

12.5MHz versions of the NMOS 68450 may or may not have existed. They are listed as "under development" in the 1985 Hitachi Microcomputer Data Book, and are mentionned in Section 7 "Ordering Information" of the 1986 Motorola Datasheet, but no data is present in the timing section. 10MHz is probably as fast as the NMOS versions were made.

HD63450

I don't know for certain when the CMOS HD63450 was released. It is not present in the 1985 Data Book, but is listed with full details in the August, 1987 Data Book, including mention of the -12 speed grade and cheaper plastic DIP64, Shrink-Dip 64 and PLCC68 packages. No timing info for the -12 however in that datasheet.

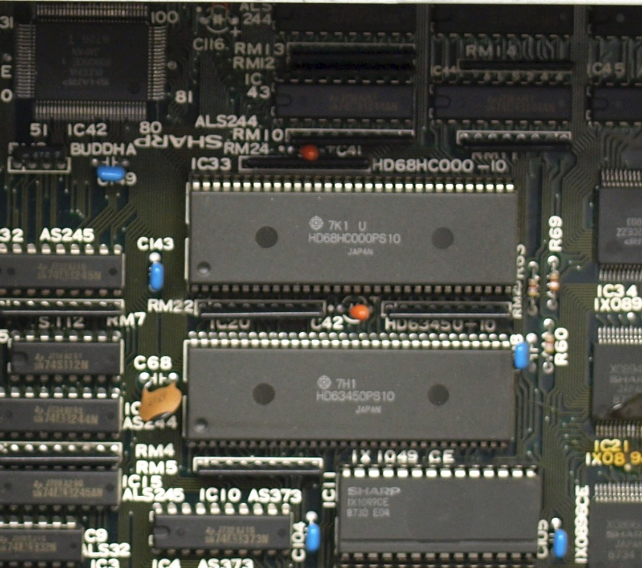

A 10MHz, shrink-DIP version was used in the Sharp X68000, first released March 28, 1987. That machine also used the CMOS HD68HC000 CPU in the same package and speed. The design of the X68000 made cooling difficult, it made a lot of sense to take advantage of the greatly reduced power dissipation of CMOS.

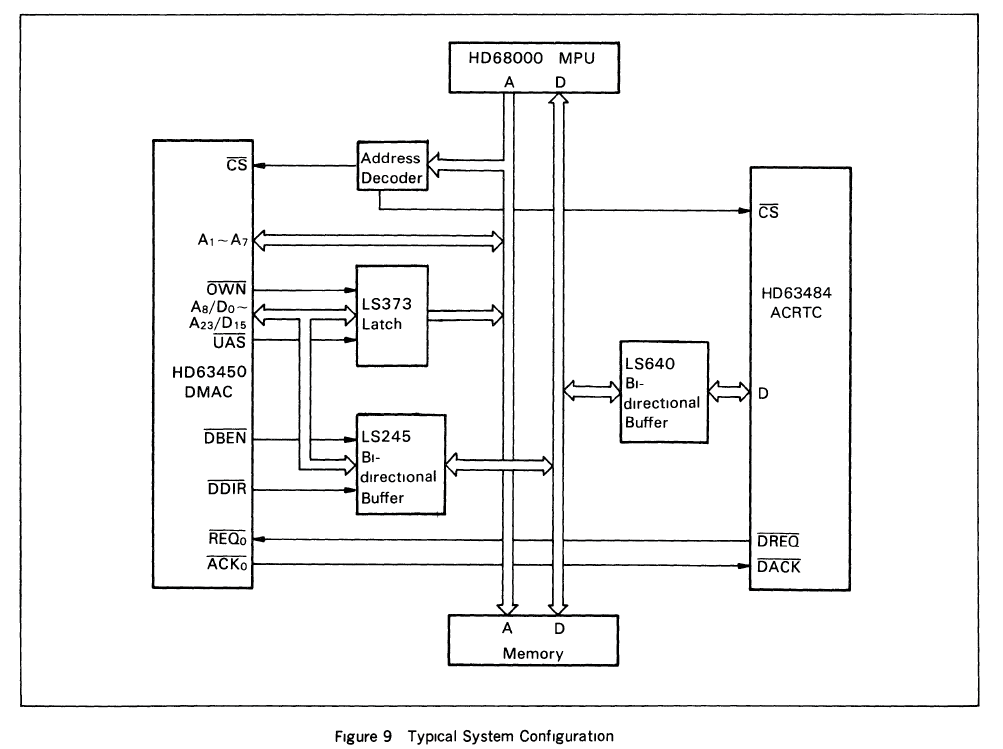

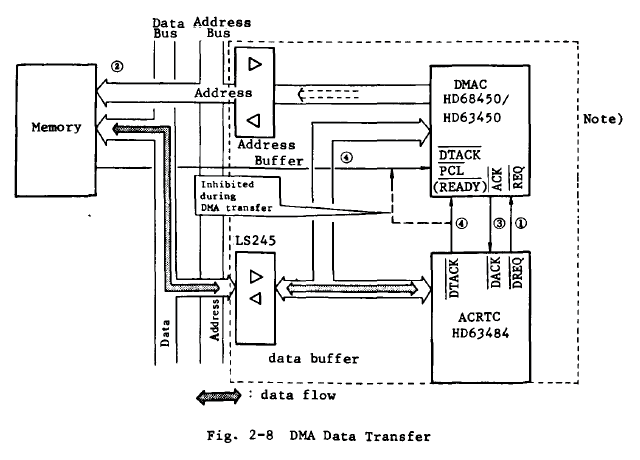

Hitachi did put some emphasis on the combined use of the HD63450 and the HD63484 graphics controller, as evidenced by this figure from the 1987 datasheet :

A similar figure is also shown in the HD63484 manual. I can't explain why they show LS640 INVERTING buffers between the '484 and the data bus, the data lines on the '484 are not inverted. A similar figure in the ACRTC Application Note 1986 shows '245 in that position.

A similar figure is also shown in the HD63484 manual. I can't explain why they show LS640 INVERTING buffers between the '484 and the data bus, the data lines on the '484 are not inverted. A similar figure in the ACRTC Application Note 1986 shows '245 in that position.

Conclusion

Since I cannot demonstrate that the HD63450Y12 or CP12 was available by the end of 1986, I will add a jumper to the board to select between the CPU clock (12.5MHz) and the ADPCM chip clock (8MHz) for the DMAC. This way original NMOS chips and lower speed -8 and -10 can also be used.

photondreams

photondreams

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.