We start with a 32-bit long integer we will denote by N. Explorations of Goldbach's conjecture (by Sylvain) and the twin prime conjecture (by Yann) lead us to find out an intricated dented wheel structure underlying the integers, where each wheel has a prime number of teeth. This is more abstractly defined as a "configuration" of a given integer, as the finite sequence of N modulo the first prime numbers. This polycyclic structure serves as a basis of a sieve to filter out the right potential primality radii of N, defined as non negative integers r such that N-r and N+r are simultaneously prime. In this framework those primes make a Goldbach decomposition of 2N=(N-r)+(N+r), and the twin prime conjecture boils down to saying that infinitely many integers admit 1 as a primality radius.

As a proof of concept, we restrict ourselves to the smallest primality radius of N, denoted by r0(N), which conjecturally (this is the content of Cramer's conjecture) and numerically is O((log N)^2) or so.

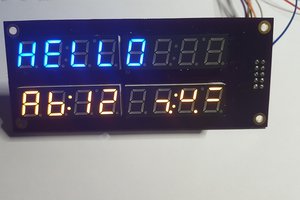

That way we end up with an upper bound for r0(N) less than 1.000, which allows us to use 5 blocks of 3 seven-segment LED displays: the 4 first ones to display N and the last (but not the least!) to display r0(N).

DISCLAIMER: I'm a complete beginner in the electronic field, so for this first project, I invited my talented friend Yann GUIDON to work as both my mentor and collaborator.

As for the hardware, we chose a Smartfusion 2 cardboard to run the sieve and subsequent primality testing algorithm (as N is prime if and only if r0(N)=0). We construct a table of primes through the use of Eratosthenes' sieve (that we code in Javascript), before loading this table in memory while starting the device. Then we use an improved double binary GCD algorithm to sieve out the potential candidates as primality radius.

Sylvain JULIEN

Sylvain JULIEN

Andrew Tudoroi

Andrew Tudoroi

David L Norris

David L Norris

Matt Stock

Matt Stock