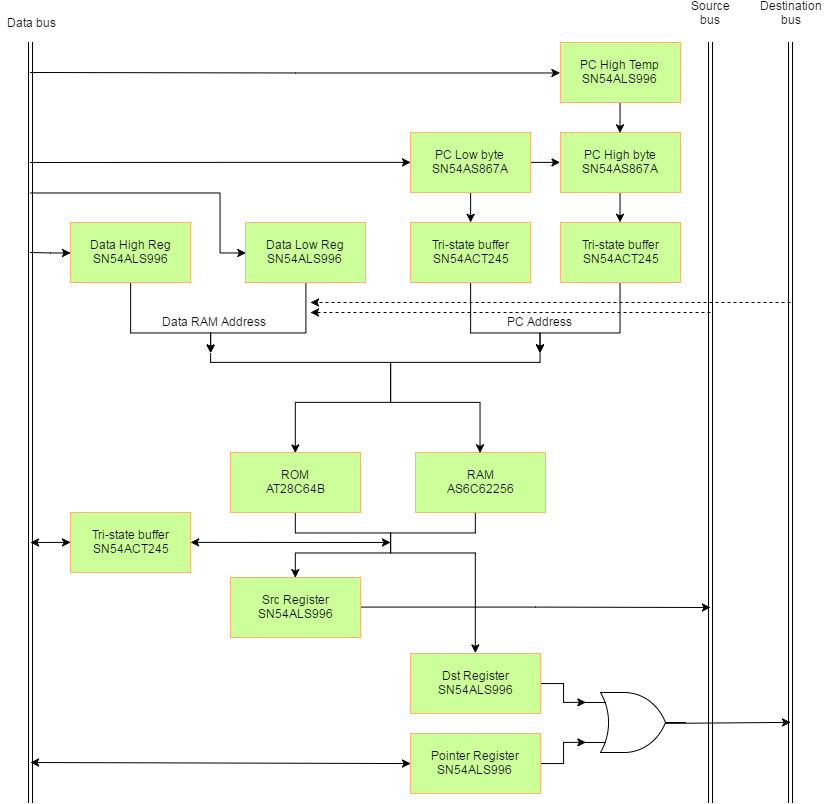

I've modified my design to use one RAM instead of two. The control state machine has been expanded to three repeating states: fetch source, fetch destination, execute. Seems to be clicking along no problems in simulation. It saves me 3 chips by doing this. I'm not sure why I would ever need to, but I could pass the source and destination registers to the databus through the tri-state buffer used to write/read the RAM. It might be worthwhile mapping these to addresses. I don't think it would cost me any chips, so I get it for free. Who knows what tricks those clever software engineers can come up with.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.