-

Schematic updates

10/19/2014 at 20:25 • 0 commentsI finally have time to work on my project! I've updated the schematics a bit and am probably about 50% finished.

The ADC I picked out can only do 4Mbps with two channels instead of the 8Mbps that I was aiming for. I may still go with it since 4 is decent but we'll see.

There were also a number of improvements that I was looking at, but I want to try and limit the risk involved in these so we'll see what I come up with. One thing that would be awesome is something like the antenna analyzer from the PortableSDR (https://hackaday.io/project/1538-PortableSDR) since the circuit for that is particularly simple. Not 100% sure how to fit it in there as I don't have a Tx path and mux, but it shouldn't be too hard to add one. My major concern is all the frontend loss since there are quite a few muxes. May even try to look at a RF relay, one that's normally closed for the Rx path.

-

ADC

08/21/2014 at 00:35 • 0 commentsOhhhh ADCs, it's always annoying looking through all the specs to find the perfect one.

I've spent quite a bit of time digging through websites to find an ADC that's not bad. Something that's good at what it does but not over-the-top. What I've come up with is the THS12082, a 12bit dual-channel 8MSPS ADC with a FIFO and a parallel interface. For a TSOP part it's almost $19, so it's not exactly cheap, but I think aside from the BBB the total part cost won't be outrageous. Not that the BBB's price is outrageous, but you know what I mean.

This ADC seems quite good. It will be able to sample both the I and Q signals at a very reasonable rate with a good amount of precision. The FIFO relaxes the requirements for needing a perfect PRU implementation (however I'm not too worried about that). The parallel interface eases signal integrity issues going through the BBB headers. So yeah, I think it will do an admirable job.

Now I just have to worry about the op-amps and the amplifier circuit.

-

Design Decisions

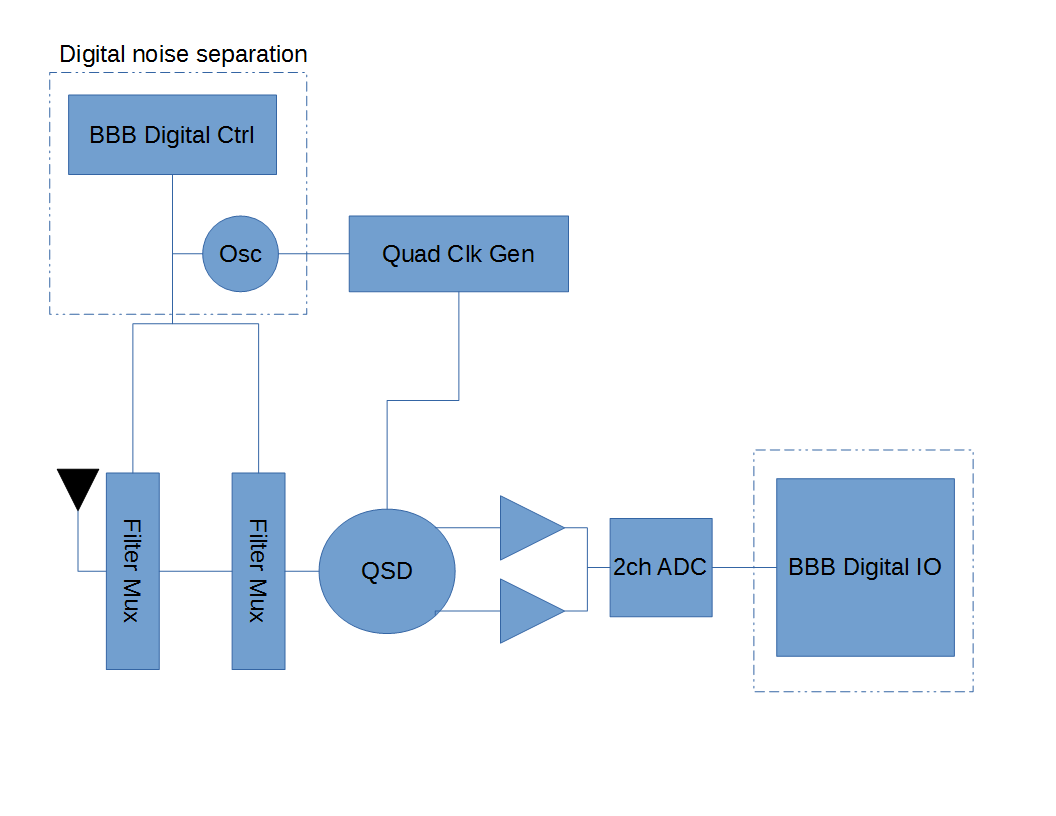

08/21/2014 at 00:23 • 0 commentsSo from the system design doc you can see a few important details:

First off the stand-alone circuitry for the quadrature clock generation remains from the softrock. I had thought about using the BBB to do it however there were multiple people online that have complained about doing it that way. I think one of the issues is that the BBB digital IOs were designed nicely to interface with digital logic, however the quad-clk-gen is clocking what is essentially an analog circuit. Things like noise and uniform phase are important here. So since it's a fairly proven design and there are not too many complaints about it I think it will be fine to keep it.

The other point to make is with the devices used for the muxing and QSD; the FST3253. Doing a fairly large search through all of the muxes I could find was unproductive; it seems that there aren't too many devices out there that do a better job than this part. I dislike that it's 5V only, but that's not a big deal. M0RZF noted that there may be a better alternative in the TS3A5017 so I'll have to compare and make a choice between the two. Otherwise they are both pretty similar.

Along this vein there is a whole lot of research here:

http://martein.home.xs4all.nl/pa3ake/hmode/index.html

But to be honest it's a lot to look through so I think I'll just design in an I/Q 'squarer' as recommended by M0RZF. In this case it's just a buffer that will minimize phase disturbances in the QSD. That is, it will cause the QSD to switch in the same points in the rising edge of the clock every time. Makes sense conceptually, but I'm not a pro at this stuff :)

-

System Design Document Up!

08/20/2014 at 23:24 • 0 commentsI made this block diagram a while ago but it was pretty terrible, so I redrew it tonight and finally got it up.

n the diagram you see that it's very similar to the softrock Rx II (diagram here). Essentially the beaglebone black (BBB) controls the local oscillator frequency, 'superband' filter selection, and reads the raw I/Q values from the ADC. It replaces the requirement for a separate uctrler and soundcard, and should be pretty easy to use through the use of the PRU on the TI chip in the BBB.

![]()

-

Updates (read: slowly stop being lazy)

08/11/2014 at 02:28 • 0 commentsOk, got the first bit of project files on github. I'm a big fan of git but I really dislike windows for development. Git on windows command prompt is very annoying...

Anyways, the general idea is use some of the beaglebone experience from Jim Kleiner and his PRJ123 ADC board he made here:

http://kd2boa.blogspot.ca/2013/12/normal-0-false-false-false-en-us-x-none.html

And generally base the SDR bits on the softrock, found here:

http://www.wb5rvz.org/ensemble_rx_ii/index

I would like to make some improvements to the softrock based on some of what Jim has done and what Robert Brown (M0RZF) has done with his unity SDR project (http://www.m0rzf.co.uk/softrock7/index.html). However the deadlines are tight and I don't want to mess something/everything up so I'm going to play this one conservatively.

Ideally once I get the Rx board working I'll either make a separate board for Tx or I will try to cram the Tx onto an upgraded Rx/Tx board. But that's way down the road. For now, it's all about the Rx. Sweet sweet HF Rx.

BlackRock SDR: BeagleBone SDR cape

HF Rx SDR cape for the BeagleBoneBlack based on the SoftRock RXII

eresonance

eresonance