Looking for components in PLCC package.

XC9500 is dead and for new project you'd better go to XC9500XL but, since it's for hobby, I'd like to have both if possible.

The datasheet reports that new XL are Pin-compatible with 5V-core, e.g. the XC9572 device in the 44-pin PLCC package has the same pinout as the XC9572XL

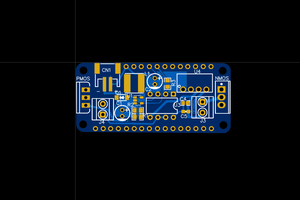

This, because I need to design the components on gEDA as well as on EagleCAD ("Xilinx.lib" doesn't happen to have a lot of CPLD components )

Main differences between XC9500 and XC9500XL

- on XL, the voltage for internal logic and input buffers is 3.3V, instead of 5V, but on the same pin

- on XL, the supply voltage for output drivers is 3.3V, instead of 5V, but on the same pin

- on XL, the high-level input voltage on user-pins can accept 5V

- For XILINX, XL is still supported, XC9500 is dead

- XL is more optimized and efficient

I can't find XC9500XL chips in PLCC package, Farnel and RS offer only the smd version.

-------------------------------------------------------------------------------------------------------------

I am looking for

- XC9536XL, and old XC9536 (if possible), 44-Pin PLCC

- XC9572XL, and old XC9572 (if possible), 44-Pin PLCC

- XC95108XL, and old XC95108 (if possible), 84-Pin PLCC

Contact me in private if you happen to have some chip for sale.

-------------------------------------------------------------------------------------------------------------

Once designed the PCB, I was ready to send the file to a service but surfing on internet I found this warning message by Xilinx:

Avoid pull-down resistors. Always use external pull-up resistors if external termination is required. This is because the CPLD, which includes some I/O driving circuits beyond the input and output buffers, may have contention with external pull-down resistors, and, consequently, the I/O will not switch as expected.

and elsewhere they recommend:

Avoid pull-down resistors on pins. All Xilinx CPLDs include additional circuitry on an I/O pin beyond just the I/O buffer. This includes ESD as well as circuits that manage power up behavior. For example: XC9500 has High-Z during power on XC9500XL/XV has High-Z during power on, then a keeper latch XPLA3 has High-Z during power on, then a keeper “half latch” CoolRunner-II has High-Z during power on, then a keeper latch Pull-down resistors “fight” the internal pin electronics, which may misbehave due to the external pull-down. For the most predictable behavior, avoid pin pull-down resistors.

Thus, it seems to me that manufacturers's warning is referred to pull-downs which might conflict with *external* pull-ups.

Pull-downs has the positive logic

Button Opened -> "0"

Button Closed -> "1"

Pull-ups has the negative logic

Button Opened -> "1"

Button Closed -> "0"

From the point of view of the CPLD logic it's not tricky to modify the VHDL code, and even the PCB is simple to be modified. I just wonder if I had better modify it or not. But I wonder:

- what would happen if I disregard the manufacturers' warning?

- and what if I use an extremely weak pull-down?

~ ~ ~ ~ ~ OK ~ ~ ~ ~

Reasons to use pull-ups rather than pull-downs:

- XC9500 has TTL input logic thresholds (0.8V low and 2.4V high) so pull-ups have higher noise immunity than pull-downs.

- Short to ground won't won't blow the output drivers.

- XC9500 has internal pull-ups which are active during power up, configuration, in-system programming and test. External pull-downs may put pins into invalid states during these times.

legacy

legacy

Nick Sayer

Nick Sayer

Christoph

Christoph

utsourceproduct

utsourceproduct

Dr.Stone

Dr.Stone

CAPS LOCK strategy

At the office I work at, I am genuinely amazed by how many people use Caps Lock on and off to get a capital letter instead of the Shift key...

It is mind blowing. It takes longer and it is more error-prone, especially when you use crappy keyboards and can't tacitly sure whether the key has activated or not.

Mumble ...