I decided to re-test the incrementer with a version that is mapped to ProASIC3. I added my custom library to the latest archive YGREC8_VHDL.20181017.tgz

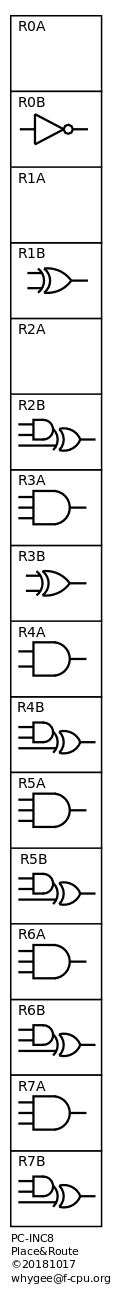

The INC8 unit now looks like this :

-- YGREC8/INC8.vhdl

Library ieee;

use ieee.std_logic_1164.all;

Library work;

use work.all;

use work.ygrec8_def.all;

Library proasic3;

use proasic3.all;

entity INC8 is

port(

A : in SLV8;

Y : out SLV8;

V : out SL);

end INC8;

architecture tiles of INC8 is

Signal A012, A34, A345, A3456 : SL;

begin

-- Row 0

e_R0B: entity INV port map(A=> A(0), Y=>Y(0)); -- Y(0) <= not A(0) ;

-- Row 1

e_R1B: entity XOR2 port map(A=> A(0), B=>A(1), Y=>Y(1)); -- Y(1) <= A(1) xor A(0) ;

-- Row 2

e_R2B: entity AX1 port map(A=> A(0), B=>A(1), C=>A(2), Y=>Y(2)); -- Y(2) <= A(2) xor (A(1) and A(0));

-- Row 3

e_R3A: entity AND3 port map(A=> A(0), B=>A(1), C=>A(2), Y=>A012); -- A012 <= A(2) and A(1) and A(0) ; -- FO7

e_R3B: entity XOR2 port map(A=> A(3), B=>A012, Y=>Y(3)); -- Y(3) <= A(3) xor A012;

-- Row 4

e_R4A: entity AND2 port map(A=> A(3), B=>A(4), Y=> A34); -- A34 <= A(3) and A(4); -- F02

e_R4B: entity AX1 port map(A=> A012, B=>A(3), C=>A(4), Y=>Y(4)); -- Y(4) <= A(4) xor (A(3) and A012);

-- Row 5

e_R5A: entity AND3 port map(A=> A(3), B=>A(4), C=>A(5), Y=>A345); -- A345 <= A(3) and A(4) and A(5); -- FO1

e_R5B: entity AX1 port map(A=> A012, B=>A34, C=>A(5), Y=>Y(5)); -- Y(5) <= A(5) xor (A012 and A34);

-- Row 6

e_R6A: entity AND3 port map(A=> A34, B=>A(5), C=>A(6), Y=>A3456); -- A3456 <= A34 and A(5) and A(6); -- FO2

e_R6B: entity AX1 port map(A=> A012, B=>A345, C=>A(6), Y=>Y(6)); -- Y(6) <= A(6) xor (A012 and A345);

-- Row 7

e_R7A: entity AND3 port map(A=>A012, B=>A3456, C=>A(7), Y=> V); -- V <= A(7) and A012 and A3456;

e_R7B: entity AX1 port map(A=>A012, B=>A3456, C=>A(7), Y=>Y(7)); -- Y(7) <= A(7) xor (A012 and A3456);

end tiles;

The gates are organised in a single column, on the right of the register set block:

Several intermediate versions are also available of course, for other platforms. But I stick to ProASIC3 because it is the best way to design for ASIC later : I can see which gates are used, tune the layout, estimate the surface...

It seems to work well and this leads to the design of more bitslices. I also have to test with Libero and I must explore the explicit cell placement directives...

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.