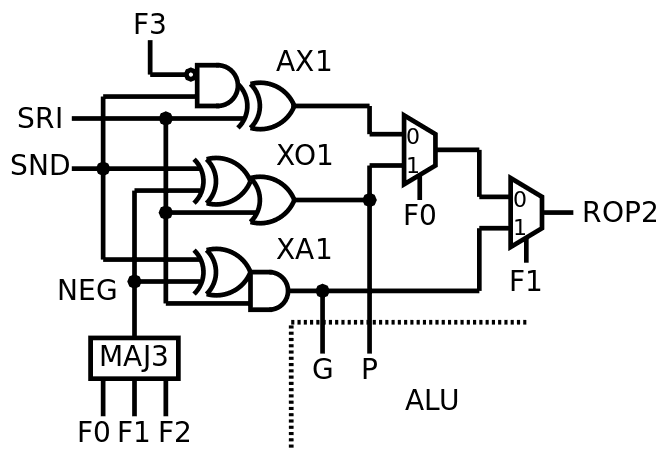

The log Improved ROP2 explained how the SET/pass function was merged with ROP2. It's a significant improvement but a tiny detail lets us go even further!

Indeed: with YGREC8, there is no XNOR opcode so the source of the XOR gate is not required to go through the inverting XOR of SND. The XOR gate can get its operands directly from SRI and SND, and SND is anded with /F3.

The inverting XOR (for NEG) has now only 2 outputs so this function can be merged with the P&G (OR and AND) gates for the A3P version (at the cost of a higher fanout of NEG, which can be managed through gate duplication). And since the NEG signal has one new "don't care" value, its calculation can be relaxed a bit.

The ROP2 part is now only 5 gates with 3 inputs: 2×MUX2, AX1, XO1, XA1 (of course, this is specific to ProASIC3). This shaves 32 tiles from the FPGA implementation, it's not insignificant...

There is enough room left for fitting one MUX2 (after the G/AND) but there is no instruction that could use it, since it's too early in the datapath.

Correction : NEG is defined by (F0.F1) xor F2, so it's not MAJ3, but AX1C...

| F3 | F2 | F1 | F0 | NEG | |

| XOR | 0 | 0 | 0 | 0 | x |

| OR | 0 | 0 | 0 | 1 | 0 |

| AND | 0 | 0 | 1 | 0 | 0 |

| ANDN | 0 | 0 | 1 | 1 | 1 |

| CMPU | 0 | 1 | 0 | 0 | 1 |

| CMPS | 0 | 1 | 0 | 1 | 1 |

| SUB | 0 | 1 | 1 | 0 | 1 |

| ADD | 0 | 1 | 1 | 1 | 0 |

| SET | 1 | 0 | 0 | 0 | x |

It should work better, now.

AAaaaaaannnnnd.... 57. ROP2 reloaded

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.