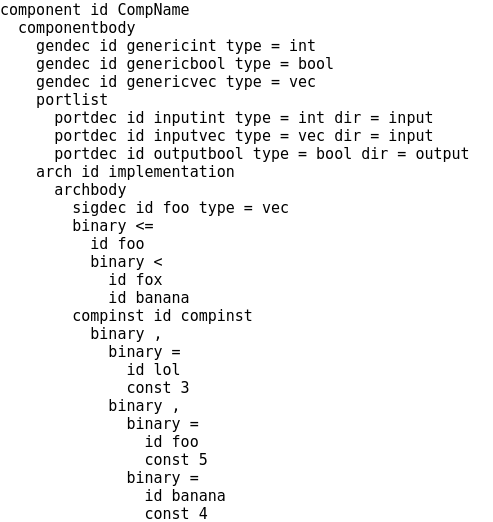

I'm pretty familiar with VHDL (I've implemented a synthesizable 8-bit CPU with it, and am currently working on an sdram controller), but there's certainly a decent amount of the language I have yet to explore, such as usage of procedures and functions.

Presently, my limited language specification will dump most of VHDL's useful features. In fact, right now, it wouldn't be useful as an HDL because it doesn't support subcomponents, but I intend to add support for those, as well as procedural generation and process statements after I get the code generation for the first revision of the language working.

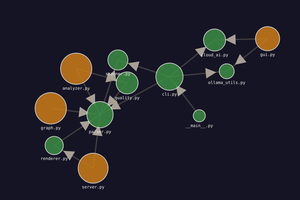

The compiler (written in python) would take my language as the source code input and output synthesizable VHDL. Depending on the progress of the project, I may look into adding constructs for some of VHDL's verification features.

This project doesn't address any major flaws with VHDL. It's just the verbosity issue that my language aims to address. My intent with this project is not to do away with VHDL, but to provide an alternative. Ultimately, the compiler is just a tool to generate VHDL that must later be handed to a synthesis tool to generate a netlist.

Reed Foster

Reed Foster

Edward Li

Edward Li

Brandon

Brandon

Ethan Zhang

Ethan Zhang

Dylan Brophy

Dylan Brophy

Have you seen SKIDL? https://xesscorp.github.io/skidl/docs/_site/index.html