The Zilog ZS180 seems to be the last member of the 64180 family in active production.

For 33MHz clock max:

3 clocks per memory cycle = 11 MHz cycle rate.

3 clocks per instruction = 11 MHz instruction rate (one opcode).

6 clocks per instruction = 5.5 MHz instruction rate (one opcode, one data byte).

32 MHz would be more convenient , as the STEbus needs a 16 MHz system clock.

I recently bought eight Z180 chips for £5. Rated at 8 MHz so only twice as fast as a 4 MHz Z80, but will be okay for most work.

The Z180 would be useful for applications that would benefit from 1 megabyte of memory space, such as CP/M. However, I would use my PC for development work and Z80 systems as targets to run small applications. Therefore it might be more useful to develop a faster Z80 system than a larger Z180 system.

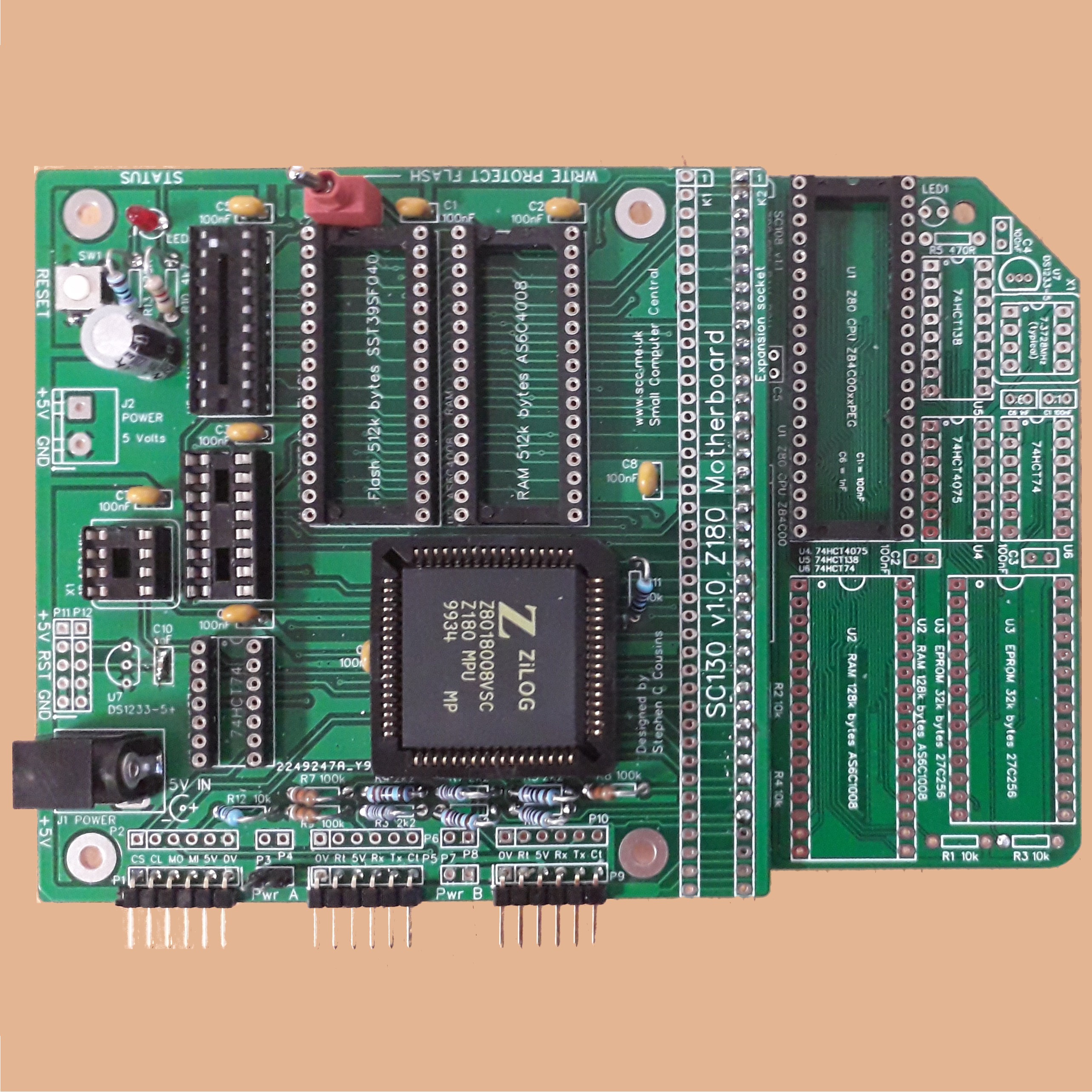

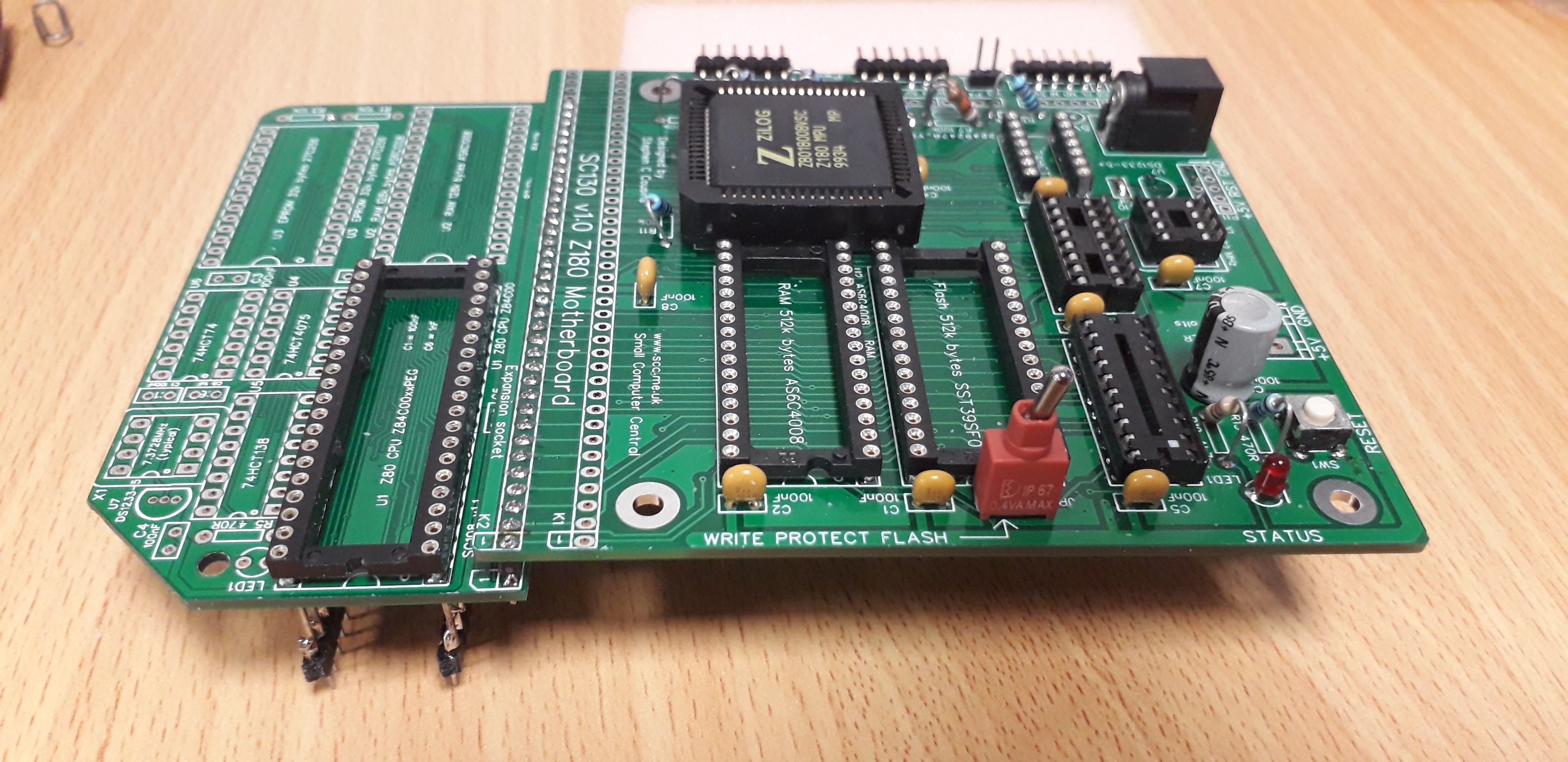

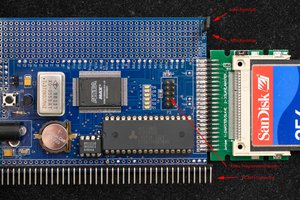

I considered using the existing SC130 board to avoid a lot of hand-wiring address, data and control buses. There is not much complicated going on there. The firmware is working with an overclocked CPU.

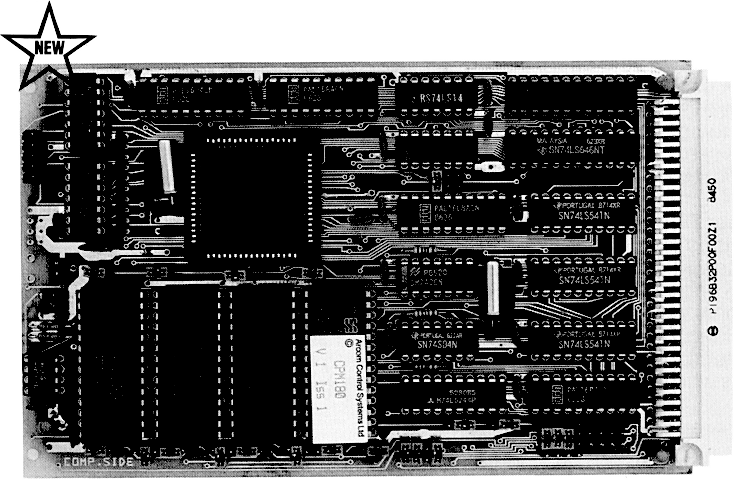

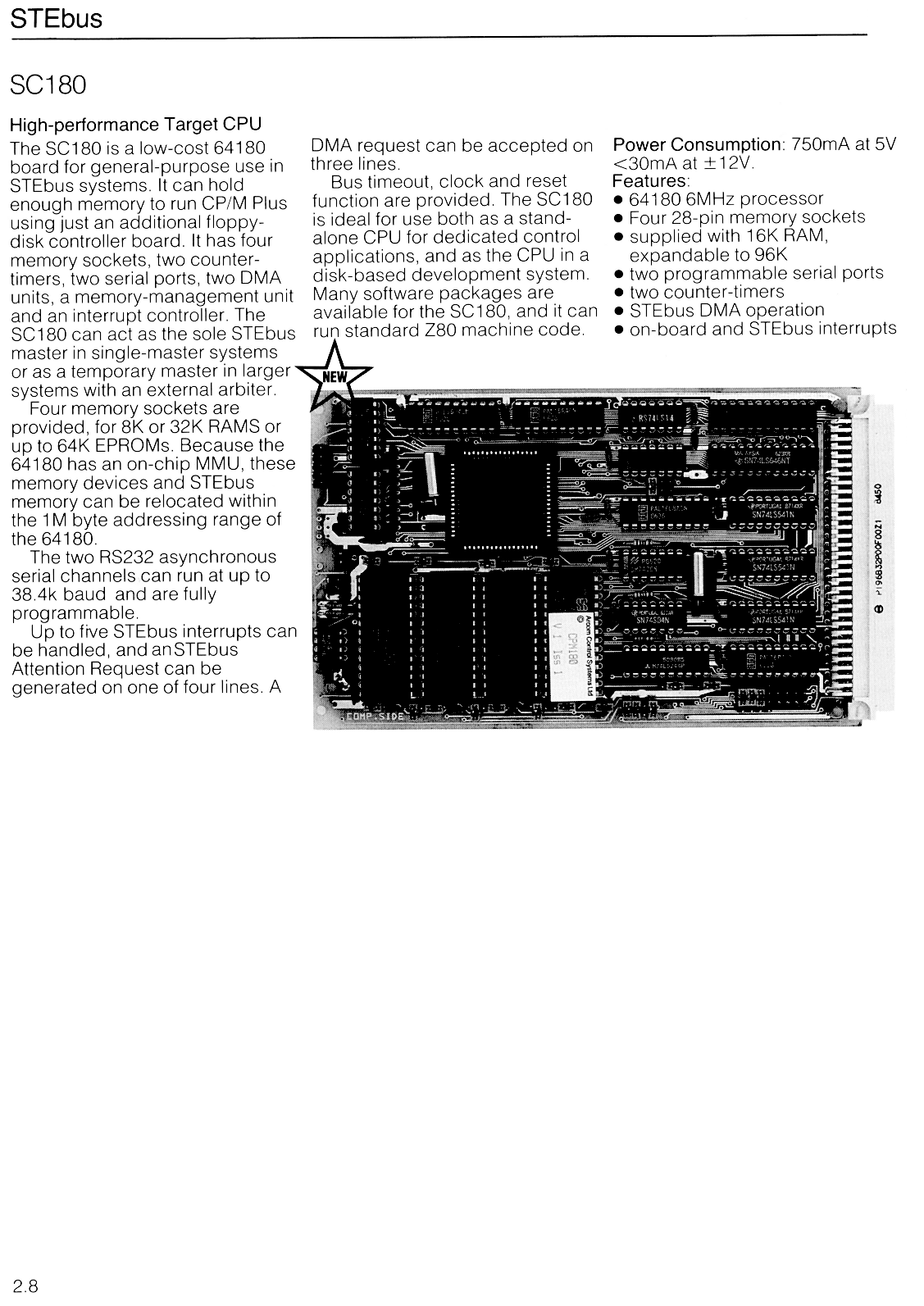

Ideally I would have liked an Arcom board because their PALs are not read-protected.

Keith

Keith Really inelegant and I suspect it would have added unreliability even if the idea was sound.

Really inelegant and I suspect it would have added unreliability even if the idea was sound.

Plasmode

Plasmode

Just4Fun

Just4Fun

Trevor Johansen Aase

Trevor Johansen Aase