sdramThing was recently featured on the Hackaday Blog! Thanks Al Williams!

SDRAM Logic Analyzer Uses An AVR And A Dirty Trick | Hackaday

Note that sdramThing4.5 (this project) has pretty much reached an end. The next phase is more of a peripheral--using these same "dirty tricks"--which can be connected to any uC, SBC, or even a PC's slow parallel port. Check it out at #sdramThingZero - 133MS/s 32-bit Logic Analyzer

(which was also recently-featured on the blog! Thanks Benchoff!)

For an electrically much-simpler circuit to drive an old laptop LCD display using just an AVR and two TTL chips, see: avr-lvds-lcd (it can even be done with an 8-pin ATtiny85 with only 512B of RAM!).

I should also give some credit to this project: http://tinyvga.com/avr-sdram-vga for introducing me to SDRAM's Burst-Mode which sdramThing relies on *heavily*.

This description is quite a bit outdated... I'm at sdramThing4.5, and many of these notes are from 3.0... Beware ;)

What is sdramThing?

This project (sdramThing3.5, now) implements a logic-analyzer interface for an analog oscilloscope.

It works by sampling data at high-speed, then repeating that same data quickly-enough that it can be seen as a bright steady trace on an analog oscilloscope.

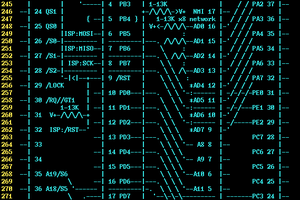

Currently, it samples and repeats at 20MS/s. 64MB of a 128MB SDRAM DIMM is dedicated to storing these samples, and it has the ability to sample/repeat 32 bits simultaneously (2MSamples per input). Two of these channels are output as Red and Green on an old laptop display.Cursors are used to select and repeat only the interesting portion of the sample, triggering the oscilloscope at the beginning of the selected-data, then repeating the selected samples several times. This back-to-back repeating of short-duration samples allows for bright traces on a 'scope, even at high "zoom".

This sample/repeat process is made-possible by sdramThing's "Free-Running" mode. This mode takes advantage of the SDRAM's synchronous nature to allow it to control itself. (See below, for more details).

In Progress:

The particular project that inspired this project has requirements outside sdramThing3.0's ability. My data-source appears to have a clock-rate of 25MHz, while sdramThing3.0 has a sample-rate limited to the AVR's clock-speed of 20MHz.

Thus, I've revisited looking into making use of the SDRAM's ability to run at speeds much faster than my AVR (thus: sdramThing3.5).

It's entirely plausible, with a bit of work, to get sampling up to (and exceeding) the SDRAM's rated clock-speed of 133MHz (133MS/s). But currently, I'll be happy to get it working at 40MS/s, as my attempts at decoupling the SDRAM clock from the AVR clock have been slow-in-progress.

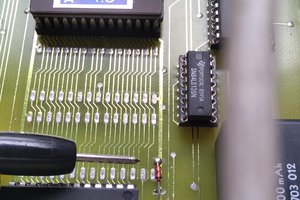

The current status, as has been for a while: I have designed and soldered-up the "one-shot" circuitry necessary for decoupling the clocks, but, ironically, it's not even working with that circuitry in "bypass" mode. I've been fighting this for a while, now. Finally, I've reimplemented the ability for the AVR to read-back the data it wrote to the SDRAM, so maybe I'll get somewhere soon :)

Details (a tiny bit outdated):

For more info on Free-Running SDRAM and sdramThing3.0, click here.

As I'm refreshing my memory on how it works, so as to fix some bugs and improve functionality, I'll probably throw some relevant notes here, both for you and for me ;)

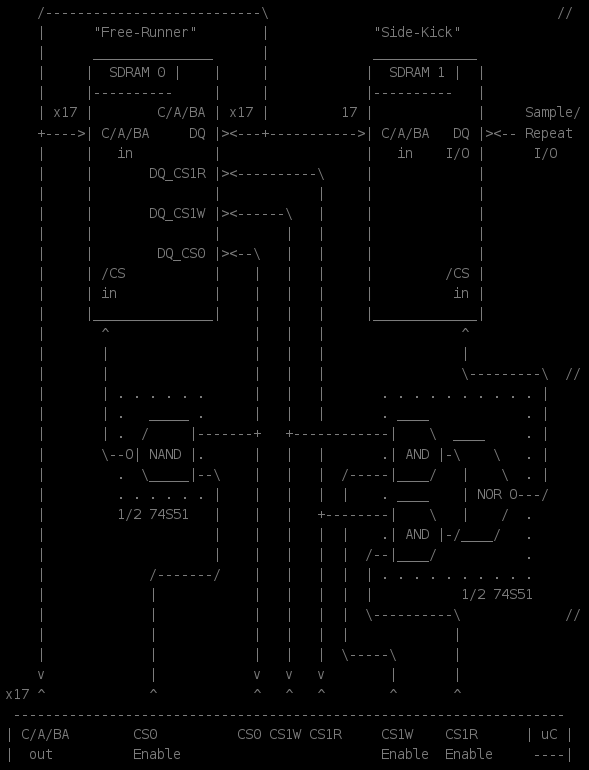

sdramThing3.0 makes use of two groups of memory on a typical DIMM. The "Free-Runner's" memory is loaded with all the commands which are fed back to both devices' command/address-inputs. Thus, the SDRAM actually sends commands to itself, and runs "free" from (independent of) external control (like the AVR).

The "Side-Kick" has two modes: Write and Read, which correspond to the "logic analyzer's" Sample and Repeat.

Multiplexing-logic allows for selecting the mode... The Free-Runner is loaded with commands for both Read and Write for the Side-Kick. Both commands are always output. The logic enables the read commands for repeat-mode, and enables the write commands for...

Read more » Eric Hertz

Eric Hertz

Jason Nelson

Jason Nelson

AWESOME state machine! and found a use for it!

so, question, is the data your loading in 512 words repeated a LOT of times? if so, have you thought it might be interesting to have the two memories operate back and forth to replicate it themselvs? I didn't think it out, just asking.