This will be one of ready made ready to use configurations and demo designs for Soft Propeller: USB Analyzer - Full Speed (maybe also LS). There is no extra hardware needed (except maybe ESD protection!).

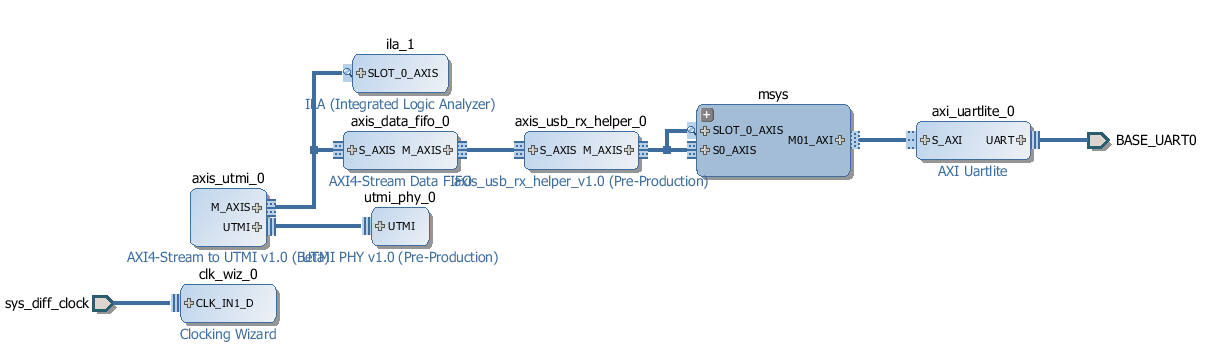

This is how it looks if you have created the USB Analyzer application, utmi_phy, axis_utmi, axis_usb_rx_helper are IP Cores that I have not had time to make public yet. They will be available under free license (MIT most likely). The remaining blocks are free IP Cores from Vivado IP Core repository. This design uses 2 FPGA pins as USB receive only PHY and converts the USB traffic into single byte stream.

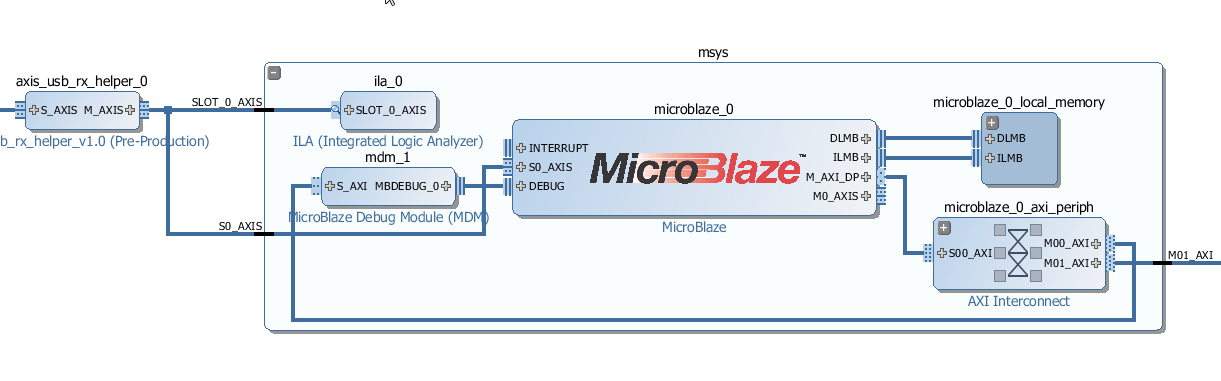

USB log data stream is connected directly to MicroBlaze AXI4-Stream port, and USB log data is read using MicroBlaze custom special instruction.

Note that the 2 onchip logic analyzer IP Cores (ILA) are not requried for the design, I use them only during testing. With Softpropeller the same stream can be read and processed by one of the ARM Cores, MicroBlaze is not needed (but could be used as pre filter processing enginge). Note that MicroBlaze is COMPLETLY free for Xilinx 7 series (for pre 7 series MicroBlaze required a paid license).

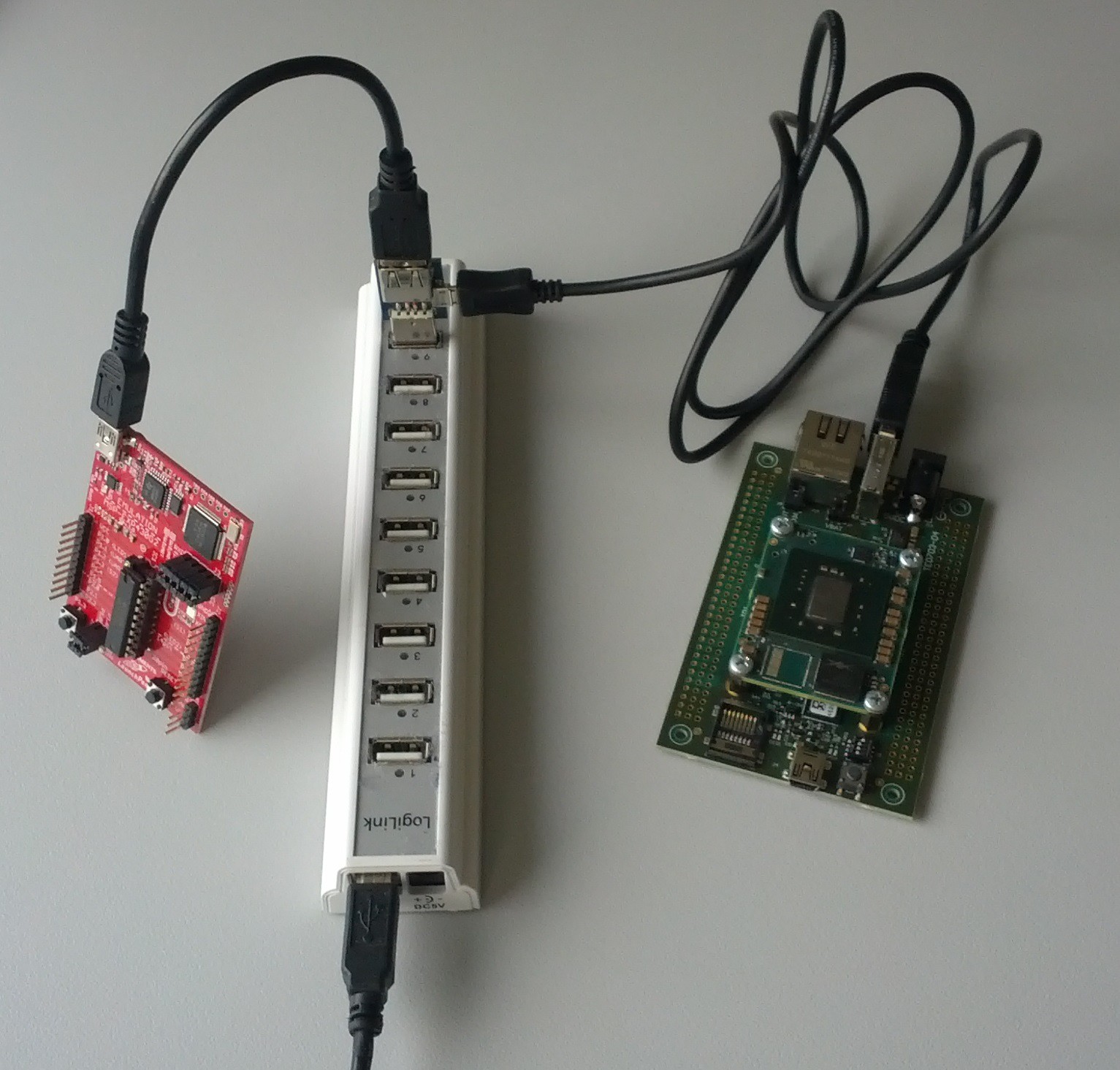

This is workint setup for the Development of the USB Analyzer system. Inserted into the hub is usb-usb-usb break-out board (a design of mine made many years ago). The RED board is usb device whos comms are to be analyzed (some TI launchnad in this case). The grey area to the right is bare die of Xilinx Kintex K160T.

With this setup the USB DP/DM are directly connected to FPGA I/O Pins with no added ESD protection circuitry, this is eventually deadly for the I/Os, but so far the Kintex has survived all experiments.

For actual USB Analyzer desing the "break out" PCB or connection to physical USB lines should include some protection circuitry.

Antti Lukats

Antti Lukats

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.