The YASEP started in 2002 started as a side-project, a hobby that has now turned into my first Mandelbrot-complete architecture. It has also spawned several sub- or side-projects such as HTTaP, YGWM and more (see my other projects).

The YASEP strives to be as free as possible (to the point of creating custom tools), small and simple (easy to understand by newcomers, uses as few resources as possible), hence as cheap as possible so it can be used anywhere, even for education (I'm looking at you, Arduino !)

All you need to get started is to point your browser at the HTML5-based windowed IDE. The last stable version is stored at http://archives.yasep.org/yasep2013/

Follow the tips, click around... It's all in your browser so you can't break anything (though you can lose your work). No per-seat fea or artificial limitation. You can hack (with) it !

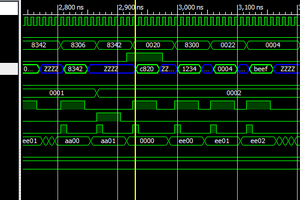

You can start from existing code, edit your own version and simulate it ! (Code save and load are a bit broken but there are workarounds, please help me fix that). When you are happy with the code, it can be uploaded in a matter of seconds to a Flash SPI memory (this feature was then spun-off as #SPI Flasher).

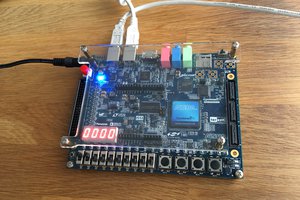

In october 2015 I started a related project : #Discrete YASEP

It's a YASEP implemented with MSI CMOS chips for maximum visibility and insight into the guts of this architecture.

Logs:

1. Call for help !

2. ASIC

Yann Guidon / YGDES

Yann Guidon / YGDES

ErwinM

ErwinM

f4hdk

f4hdk

Erik Piehl

Erik Piehl

aaron

aaron

Is there a C compiler for this CPU? If not, I could try to create one with Clang and LLVM.