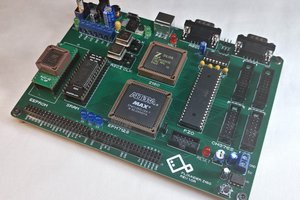

Motorola 68000 computer

A mc68k-based computer motherboard, some expansion cards, and a very basic multitasking OS, all built from scratch.

A mc68k-based computer motherboard, some expansion cards, and a very basic multitasking OS, all built from scratch.

To make the experience fit your profile, pick a username and tell us what interests you.

We found and based on your interests.

The following is a rant. If you're not in the mood for reading a rant, please don't bother reading on.

So: the LM3671 dc-dc converter. According to its data sheet, "...only three tiny surface-mount external components required (one inductor, two ceramic capacitors)". Astonishing! Compared with an LDO, the cost of an extra inductor buys you a switching converter with much better efficiency. Unless, of course, it doesn't.

Some background: I'm building a video card for the MC68000 system. I'm using the design of the video card as an opportunity to validate some tech that I'm going to use in an MC68030-based system that's coming along soon. The video card will attach to one of the expansion sockets on the MC68000 motherboard; these provide +5V power. The video card uses a LM3671MF-3.3 and a LM3671MF-1.2 to develop the 3.3V and 1.2V supplies required by the card. Easy! So I thought, anyway...

The LM3671 features an enable pin, EN, which enables or disables the regulator. On all the regulators I've ever worked with, such a pin can be strapped to the input voltage rail in order to force the regulator into a permanently-on state - this is the required behaviour in the majority of cases, after all.

There's an interesting throwaway sentence on page 18 of the LM3671 data sheet: "... It is recommended to set EN pin low to turn off the LM3671 during system power up and undervoltage conditions when the supply is less than 2.7V...." This appears to be the only concrete recommendation in the datasheet regarding the EN pin.

It turns out that this "recommendation" is actually rather more of a requirement. In my design, the EN pin is connected directly to the input voltage supply - a regulated +5V - because I want the LM3671 to be operational all the time the +5V supply is present.

It appears that this arrangement is not suitable for the LM3671-1.2 and the LM3671-3.3. What I see, at the output of both regulators, is a rough triangle wave, sawing between 0V and about 2V. The regulators draw an effectively unlimited amount of current in this state, and present an output that is not only unregulated, but swings far above the rated output voltage. I have reproduced this result on multiple LM3671 devices, using a pcb layout which is nearly identical to the layout suggested in the device's data sheet. I am not the only person to have encountered this problem.

So: my conclusion is that I will definitely not be using this device in future, and I will be suspicious in the extreme of any device making similar claims regarding the number of external components required to make an effective regulator. It's a shame, as the device promises so much; I guess the rule is, as ever: if it seems too good to be true, it probably is. Caveat emptor.

This is the shortest log ever, written mainly because a) I'm feeling guilty about not having written a log for so long, and b) to prove that I'm still making progress on the MC68000 computer project.

I've already got an ATA (IDE) interface and serial ports on the MC68000 motherboard; other project logs describe my adventures creating Ethernet and PS/2 controller expansion cards for the system. The obvious next step is therefore to add video support. This is what I've been up to for the last month or two.

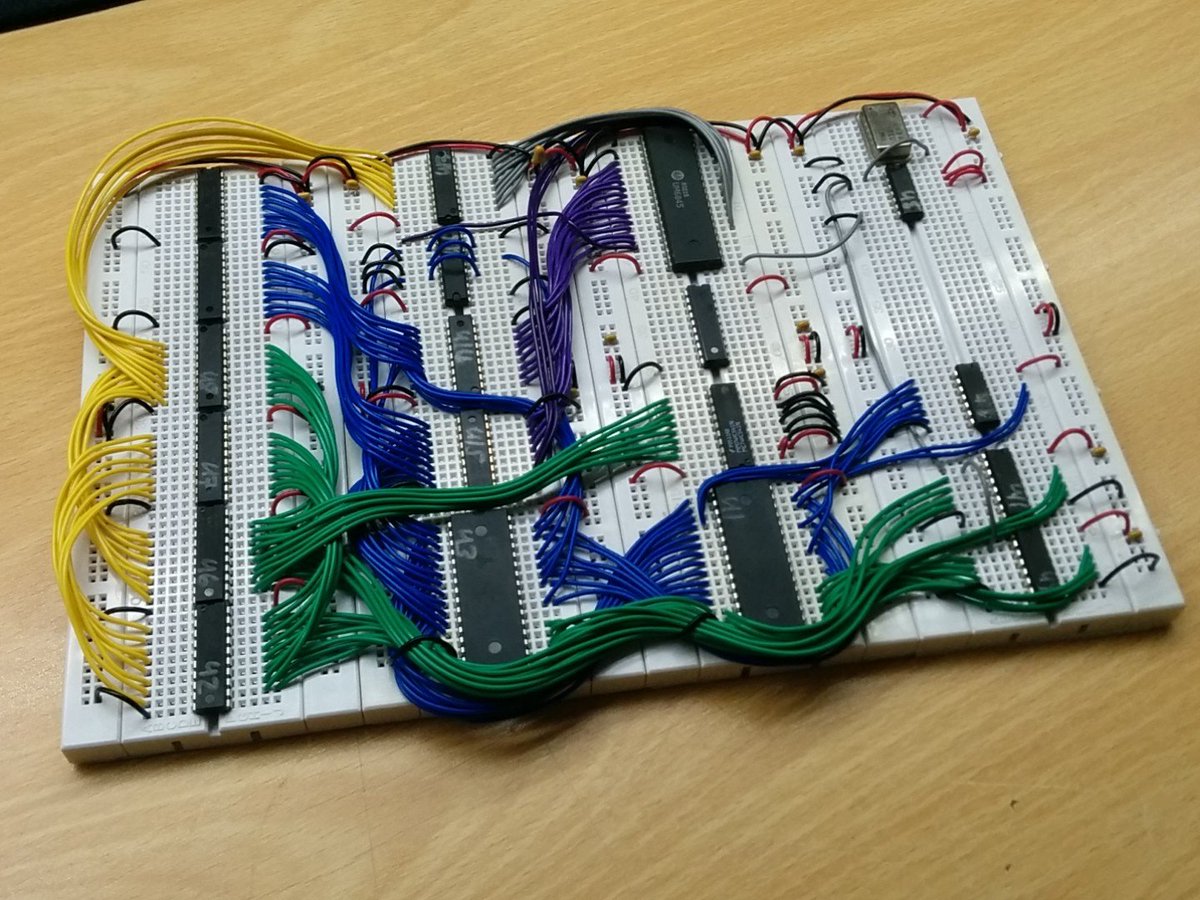

Initially I designed a framebuffer card based on an MC6845. I managed to get a viable-looking design together using some fast SRAMs, a couple of high-speed shift registers, a triple video DAC and a *lot* of bus transceivers. The prototype looked a bit like this while it was under construction.

I became a bit demotivated when the time came to route the (gigantic) PCB. I have already routed one fairly gigantic PCB (the motherboard), and it can be a real time-sink. So: I ended up breaking a few of my own rules.

I became a bit demotivated when the time came to route the (gigantic) PCB. I have already routed one fairly gigantic PCB (the motherboard), and it can be a real time-sink. So: I ended up breaking a few of my own rules.

So far I've kept the MC68000 project fairly "vintage". Except for the Ethernet controller, the system uses technology consistent with the 68k's era: no surface-mount, all DIL packages, no fancy stuff. The point of the project, however, has always been to learn as much as possible. Readers of my other logs will know that I've tried to avoid using too much pre-packaged stuff; there are plenty of good, easy-to-use 80s/90s-era video controller ICs out there, and it would be quite easy to throw together a graphics card based on one of those, but where would be the fun in that? So, I thought - stick with me on this - what better way to learn about video hardware than to design my own video controller IC, and build a graphics card around it?

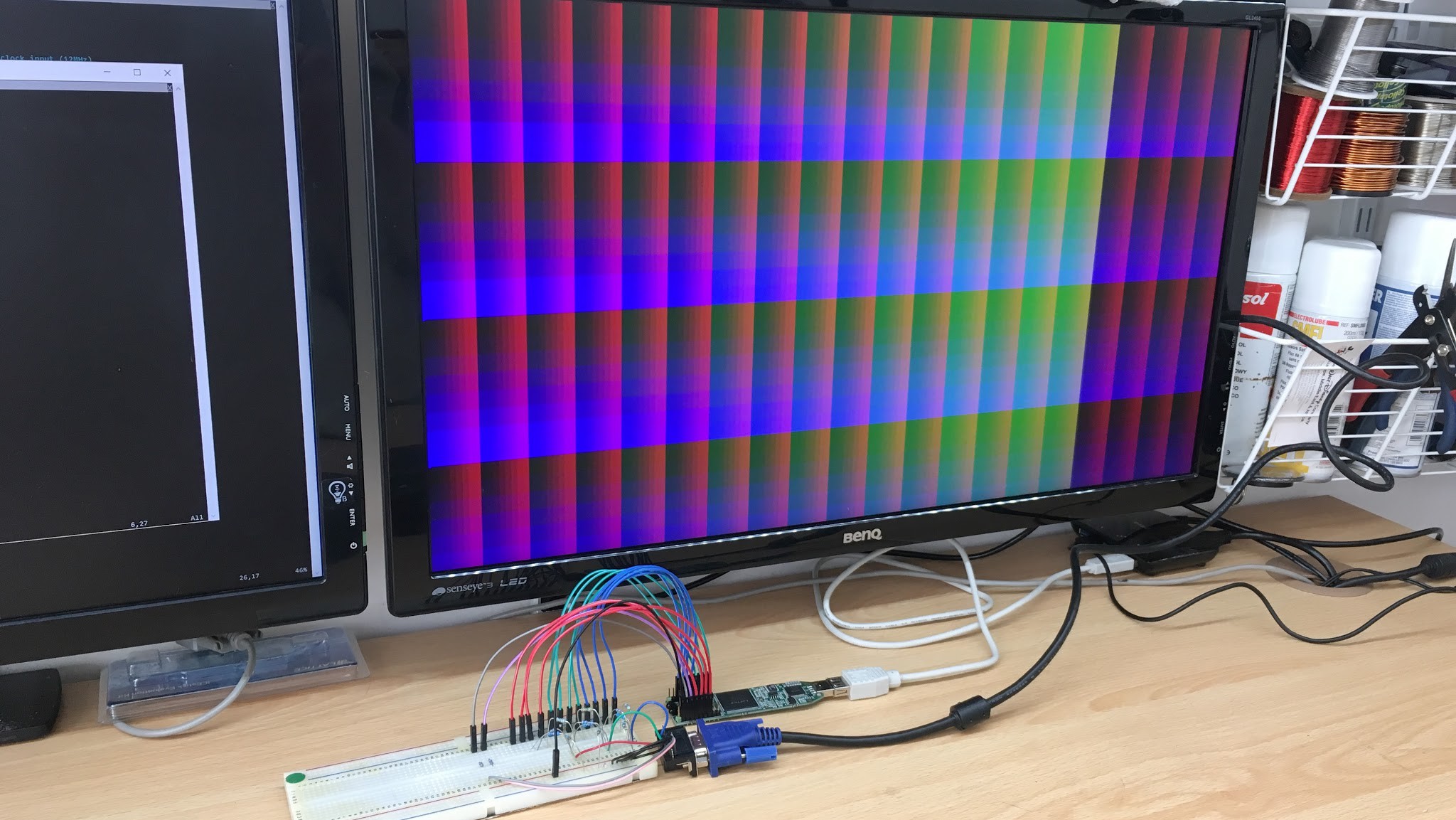

I started a design based on a Lattice iCE40HX1K FPGA. I had already played around with a Lattice iCEstick and found the FPGA (and, crucially, the tools) quite easy to use. I learnt a bit of VHDL, and implemented a VGA pattern generator:

| Controller | iCE40HX1K-TQ144 |

| On-board video RAM | 1MB SRAM (512k x 16), 12ns access time |

| Supported video modes | 640x480, 800x600, 1024x768 (all at 60Hz) |

| Colour depth | 8 bit (3:3:2 R:G:B) via ladder DAC |

| Interface | 15-pin high-density D connector (analogue VGA) |

| Host interface | 16-bit data bus, direct-mapped RAM, zero wait state, zero contention |

| Host interrupt support | VSYNC / HSYNC / both |

Anyway, the design is done and the PCB is ready to go to manufacture. I'm still working on the logic implementation in VHDL, but I'm reasonably confident that it can all be made to work.

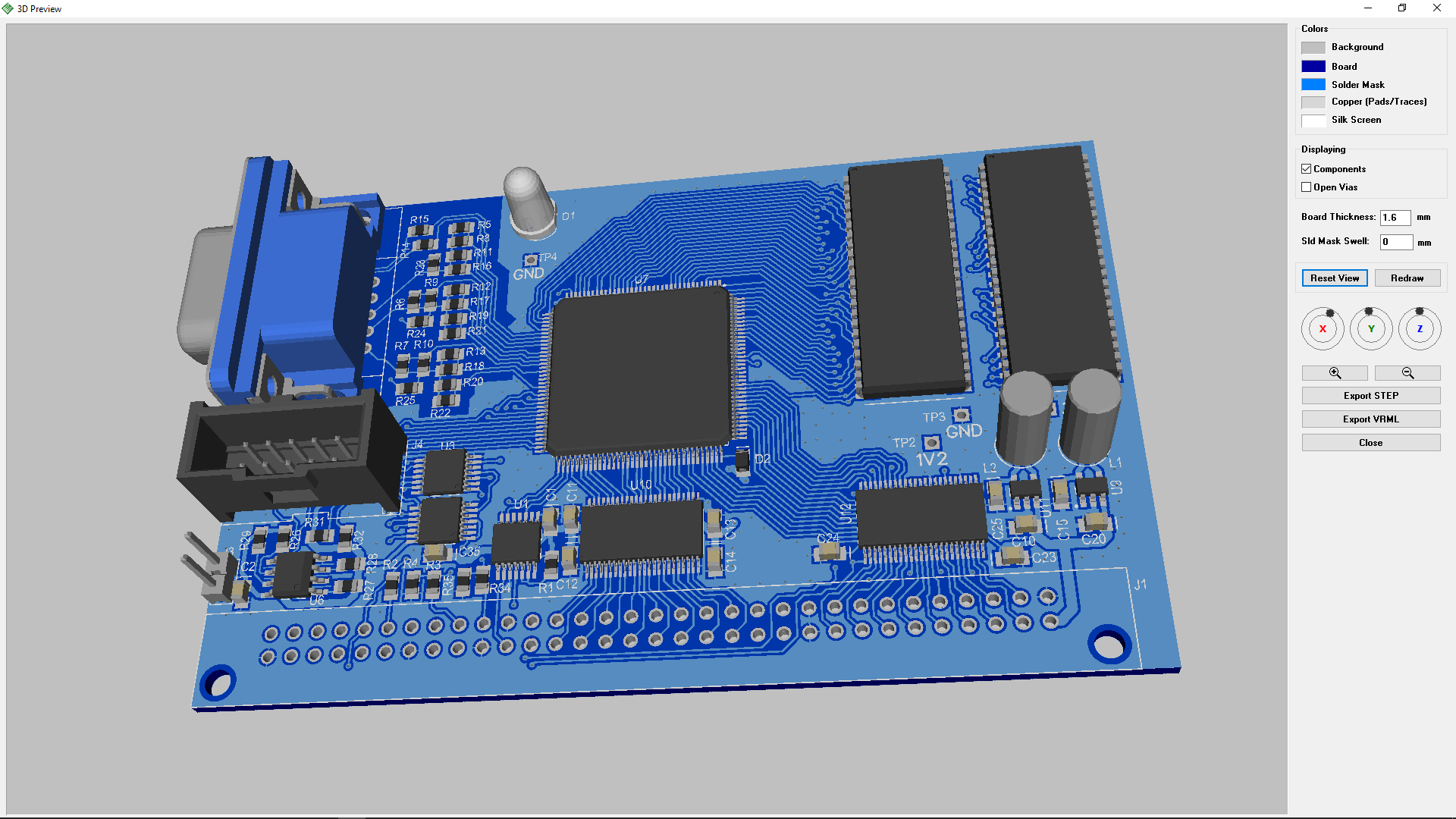

Here's a poorly-rendered 3D image of the completed board.

The design is almost entirely surface-mount. The two ICs in the top-right corner are the SRAMs; the FPGA is in the centre. The ladder DAC is the collection of resistors to the right of the 15-pin D connector. Most of the remaining ICs implement the host interface; the host connector (a DIN41612 plug) is missing from the image, as I don't have a 3D model for it. The 10-pin header connector below the VGA socket is a programming header for the SPI Flash ROM which contains the FPGA configuration bitstream.

I hope to be able to upload a photograph of the real thing very soon!

I spent a little while reworking the network stack in the m68k OS code. The idea is to end up with a reasonably generic stack: ideally, like Linux and friends, the OS code shouldn't really care about what kind of network adaptors are plugged in, and should support a variety of higher-level network protocols.

Having done a fairly substantial refactor, I was able to get basic protocol handling and routing working. The network stack knows how to enumerate attached network adaptors and to instantiate one kernel process per adaptor to deal with incoming network traffic. Each network protocol is written as a separate module, conforming to a common API; these are "discovered" at boot time, after the system hardware discovery phase, and started independently.

I made a 10/100Mbps Ethernet adaptor using an ENC624J600; I've written about this network card in an earlier log. On boot, the OS detects the network card and loads its driver; the network stack creates a virtual device, eth0, to represent the Ethernet interface. Multiple network adaptors are supported - a separate virtual device is created for each card.

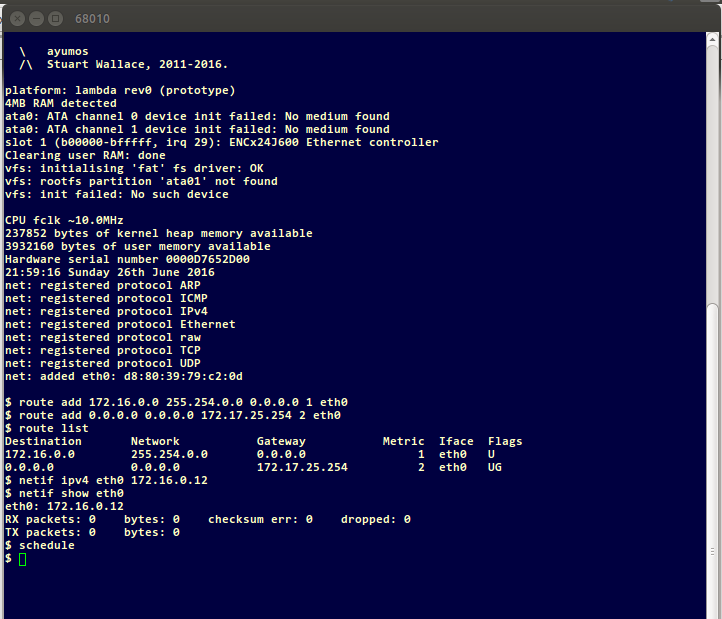

The screenshot below shows the OS booting, performing hardware discovery and other startup tasks, starting the various network protocol drivers, and finally dropping into the interactive shell (lines beginning with the "$" prompt). The output looks quite Linux-ey, but it's not Linux - all of the software running on the system is my own work.

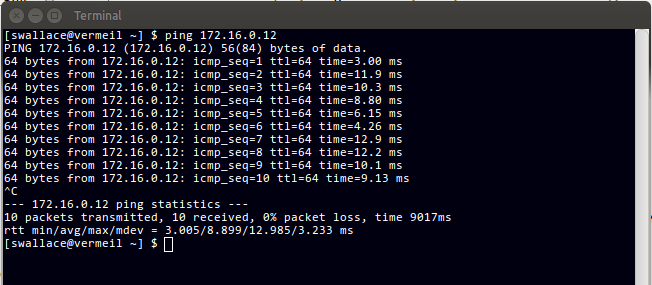

Having reached the shell, I then enter some "route" commands to set up the kernel IPv4 routing table (I have implemented basic IPv4 routing), and use the "netif" command to add an IPv4 address (172.16.0.12) to interface eth0. Finally, the "schedule" command starts the task scheduler. The system is now ready to deal with network traffic!

So, starting from the bottom of the network stack: after writing an Ethernet protocol driver, I added support for ARP. This enables the kernel to maintain a mapping between hardware addresses (e.g. MAC addresses) and protocol addresses (e.g. IPv4 addresses). All ARP traffic is handled transparently within the kernel; once the system has been up for a while, and has gathered a bit of ARP traffic, it's possible to dump the contents of the ARP table and see details of various network neighbours. All address-handling is fully generic; the output below just happens to show Ethernet and IPv4 addresses.

Next up, after ARP, I wrote a very basic ICMP driver. This enabled me to reach an important and deeply satisfying point: pinging the board! The screen-grab below shows the result of pinging the MC68000 system from a Linux host elsewhere on the LAN. The latency isn't great; this is mainly a consequence of the rather primitive task-scheduling logic. I hope to improve this in future.

I need to do a little more work on the low-level protocols before I can make a serious attempt at implementing TCP and friends. A half-decent TCP implementation is going to take a lot of work, but it should be an interesting challenge.

It's been a long time since I wrote an update on the project. My excuse is that I have been working on a new hardware platform based on a Motorola 68030 processor. This system will run the same OS code as the MC68000 system; I'm going to add virtual memory support to the code. The main focus at the moment is on designing a workable memory subsystem using 72-pin SIMMs. This has been a lot of fun, and I'll probably set up a separate project page soon to describe my work.

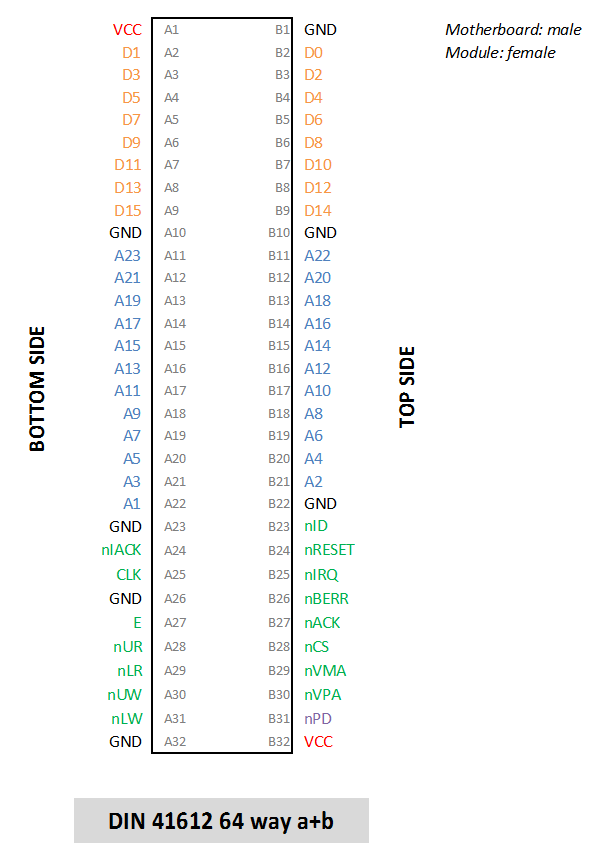

This is a short log[*] describing the 16-bit expansion card interface in the 68000 system. I've deliberately kept the design of this interface as simple as possible, in order to make it easy and quick to build expansion cards. I know I could have implemented a standard interface, like VME, S100, or (shudder) ISA, but I didn't. I felt like I'd learn more by implementing my own interface, mainly so that I could discover all of its shortcomings!

The motherboard has four expansion sockets, all with an identical pinout. Here's the setup:

The motherboard sockets are actually DIN41612 "Q" connectors - i.e. the motherboard has a male (pins) connector, and the peripheral card uses a right-angled female (sockets) connector.

Most of the pins are directly mapped to the 68000 bus interface; some are a little different. This table describes the pinout. In the table, "input" means "signal generated by the host", and "output" means "signal generated by the peripheral". "Host pullup" indicates that there's a 10K resistor pulling the pin to VCC on the motherboard.

| PIn | Type | Description |

| VCC | Power | Regulated +5V rail |

| GND | Power | Ground |

| D0-D15 | Bidirectional, 3-state | Buffered CPU data bus; only valid when nCS is asserted. |

| A1-A23 | Input, 3-state | Buffered CPU address bus; only valid when nCS is asserted. |

| nID | Input | When asserted with nCS, indicates that the host processor is running an "identify peripheral" cycle. The peripheral should place its ID on D15-D8 and assert nACK. |

| nIACK | Input | Asserted when the host processor is acknowledging an interrupt raised by the peripheral. |

| nRESET | Bidirectional, open-drain, host pullup | System reset input. Can be pulled low by a peripheral to reset the system. |

| CLK | Input | Host processor clock. |

| nIRQ | Output, host pullup | Peripheral interrupt request. |

| nBERR | Output, host pullup | Peripheral bus error output. |

| E | Input | 6800 peripheral interface: "E" clock signal (10% of f(CLK), 60:40 duty cycle). |

| nACK | Output, host pullup | Peripheral bus cycle transfer acknowledge: asserted by the peripheral to complete a bus cycle. |

| nCS | Input | Peripheral chip select: asserted by the host during a bus cycle addressed to the peripheral. |

| nUR | Input | "Upper byte read": asserted when the host wishes to read bits D15-D8. Only valid when nCS is asserted. |

| nLR | Input | "Lower byte read": same as nUR, but applies to bits D7-D0. |

| nUW | Input | "Upper byte write": asserted when the host has placed valid data on bits D15-D8 during a write cycle. Only valid when nCS is asserted. |

| nLW | Input | "Lower byte write": same as nUW, but applies to bits D7-D0. |

| nVMA | Input | 6800 peripheral interface: "valid memory address" strobe. |

| nVPA | Output, host pullup | 6800 peripheral interface: "valid peripheral address" strobe. |

| nPD | Output, host pullup | "Presence detect": should be tied to GND by the peripheral. Enables the host to detect that a peripheral is plugged in to an expansion slot. |

Each slot is mapped to a fixed 1MB region of the MC68000 address space. The expansion interface exposes all 23 of the MC68000's address lines. This might seem pointless, given that only the lower 19 lines are needed to address a 1MB space; however, exposing the entire address creates the possibility of plugging a bus analyser into a slot in order to help with debugging.

The nPD (presence detect) lines on each of the four expansion slots are connected to general-purpose inputs on an MC68681 DUART. At boot, the operating system code uses the status of these pins to determine whether any peripheral cards are attached. If a card is found, the OS runs an "identify" cycle to work out what's plugged in. To do this, the host asserts the nID line and runs an eight-bit read cycle on each occupied expansion slot. The peripheral must respond by placing an ID number on the upper eight bits of the data bus and terminating the cycle with nACK. This enables the OS to initialise a driver for the attached peripheral.

Here's a screenshot of the output generated by the system during the boot process, showing the OS identifying some peripheral cards (lines highlighted in red). Having found two Ethernet cards,...

Read more »As usual, it has been a while since my last update. I've been busy working on some new expansion cards for the MC68000 motherboard. It's a bit boring interacting with the system via an RS232 serial port, so I thought I'd build an expansion card enabling me to connect the motherboard to a keyboard and mouse.

The first step in the design was to pick a communications protocol. I wanted to implement a standardised protocol so that I could use an ordinary keyboard and mouse without modification. Having ruled out ancient XT keyboards, I was left with USB and PS/2. USB felt too modern for this project - after all, the idea is to build a system which has a level of technology roughly in line with the sort of stuff that was available in the 80s and early 90s. PS/2 it is, then! To the breadboards!

Here's the prototype dual-channel PS/2 controller plugged into the MC68000 motherboard.

The PS/2 protocol is pretty straightforward. It's an 8-bit synchronous bidirectional serial interface in which the "device" (the keyboard or mouse) generates a clock signal at around 10kHz and exchanges data with the host in a format quite similar to RS232. In PCs, the interface was implemented using an Intel 8042 microcontroller. When a key is pressed on the keyboard, a scan code is sent by the keyboard to the host. This code uniquely identifies the key, but is not related to e.g. the ASCII code representing the symbol on the key-cap. When the key is released, the keyboard sends a "key released" code (0xF0), followed by the scan code of the key. The PS/2 mouse protocol works a bit differently: whenever the mouse is moved, or a button is pressed or released, the mouse sends a small packet of data (three or four bytes, depending on the type of mouse) containing information about the mouse's relative motion and the state of the buttons.

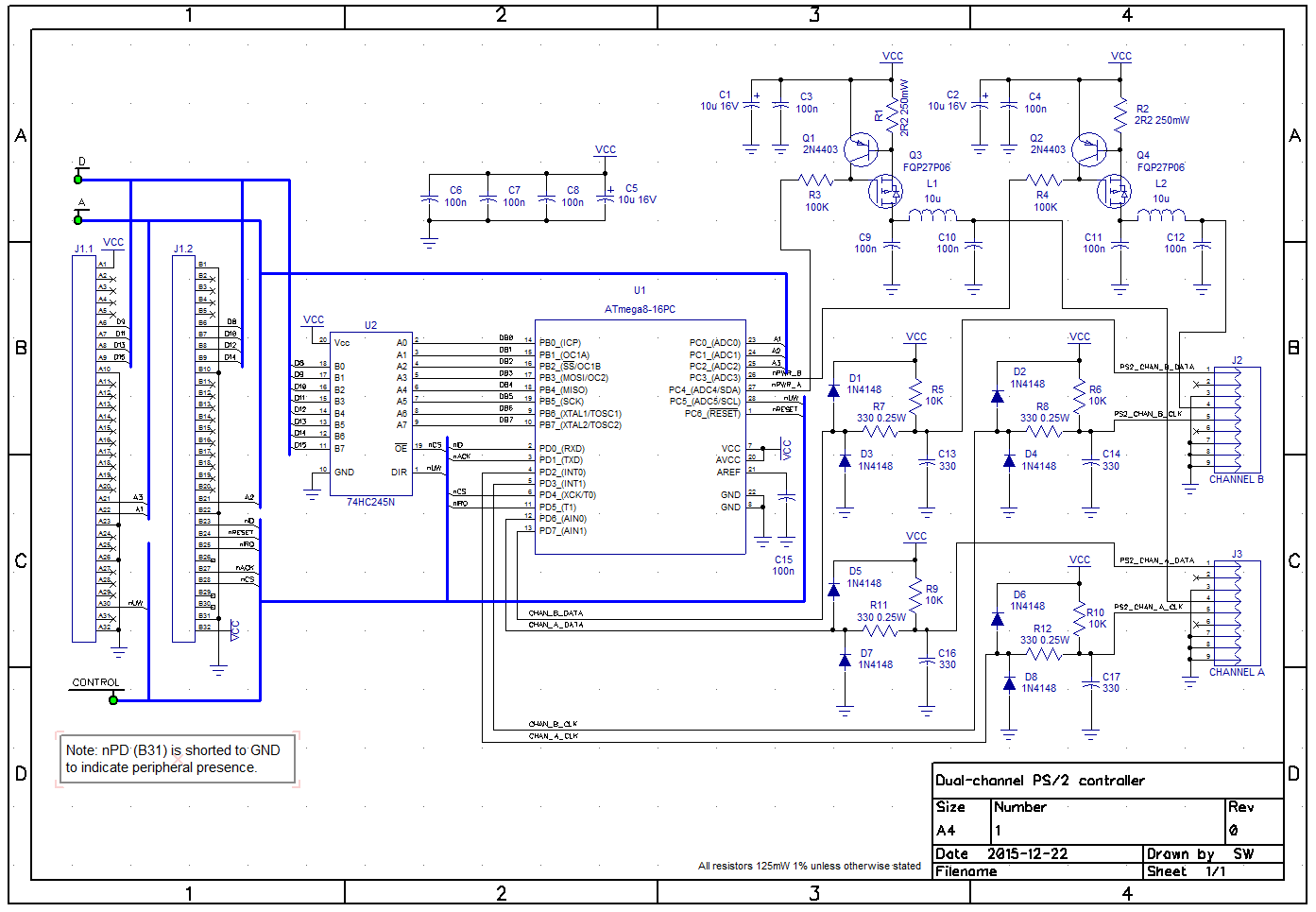

I considered building the controller around an Intel 8042, but eventually decided against it. It's a decent enough chip, but I felt that I wouldn't learn the protocol in sufficient depth by using somebody else's implementation. Instead, I decided to build an interface around a microcontroller: the (admittedly fairly modern) Atmel ATmega8. This is what I came up with.

The ATmega8 has 28 pins, which is just about enough to implement two separate PS/2 ports and an 8-bit interface to the host system. The firmware is quite simple: it's mainly an interrupt-driven state machine which manages communication between the microcontroller and the PS/2 devices. The non-interrupt-driven part of the code is pretty much just a loop which deals with the interface between the controller and the MC68000.

The controller exposes a bunch of registers to the host processor; these include a configuration register which can be programmed to enable interrupts to be raised when various different conditions are encountered on each port: byte received, transmission completed, timeout, parity error, etc. The controller also contains a 256-byte FIFO for each PS/2 channel (unlike the Intel 8042!); this means that the host doesn't need to respond immediately whenever data is received from the peripherals.

There are horror stories about the damage caused by unplugging PS/2 peripherals from early PCs. Apparently the electrical interface wasn't very well-protected, or whatever; if the rumours are to be believed, a motherboard could be destroyed by connecting or disconnecting a PS/2 keyboard at the wrong moment. It's difficult to know how much of this is true, but given that my controller connects to the outside world, it needs to be reasonably tolerant of abuse. With this in mind I have added short-circuit protection, protection against shorts to out-of-range voltages (within reason), and some transient/noise suppression. In order to make the interface somewhat hot-pluggable, I've wired things up so that the ATmega8 can switch each PS/2 port's power on and off independently.

Another slightly annoying thing about early PCs was the need to connect the keyboard and mouse to...

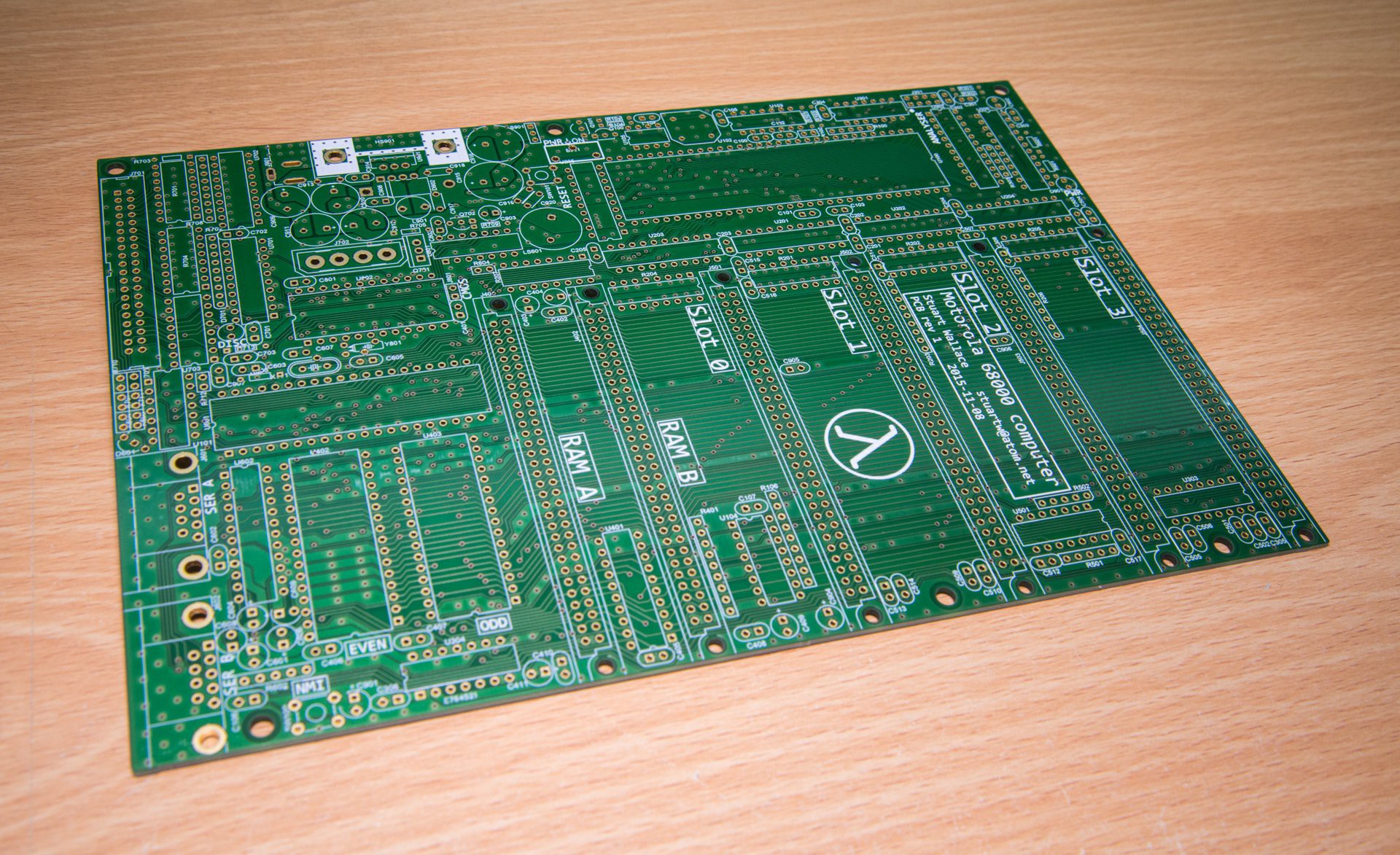

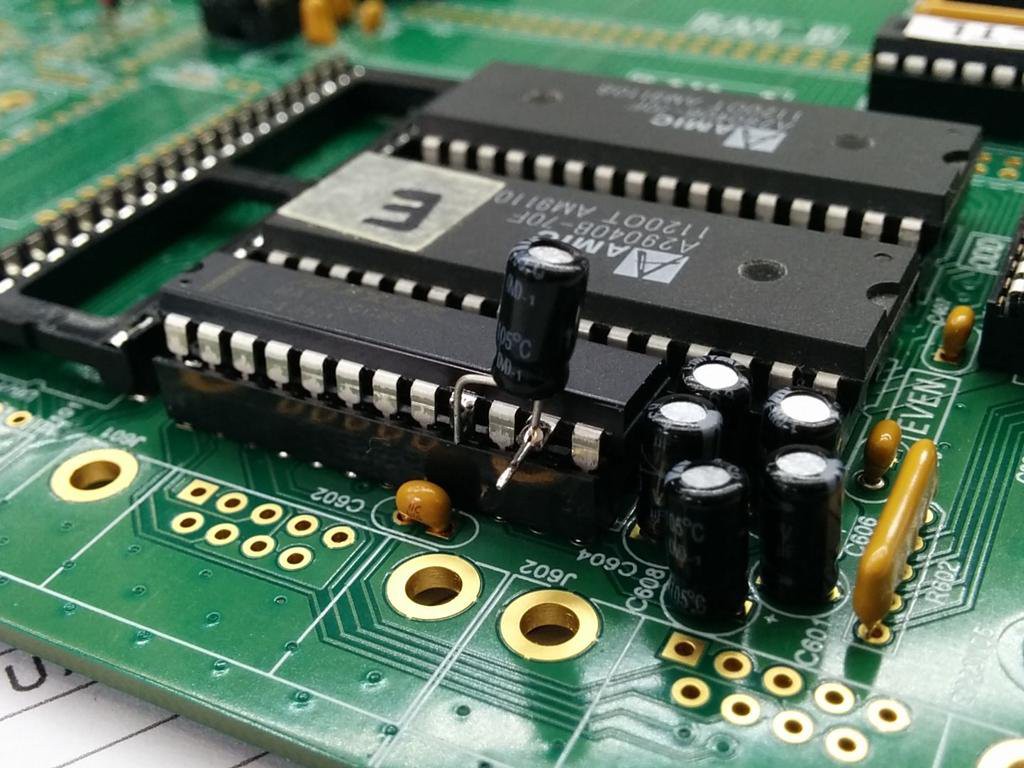

Read more »I'm about to start assembling the first revision of the Motorola 68000 motherboard. This revision, rev1 (I start my revisions at rev0), includes a few fixes for minor problems in the prototype. None of these problems were show-stoppers, and I was able to craft fixes where necessary in order to get the rev0 (prototype) motherboard working. More importantly, rev1 adds some minor new features to the board. Here it is.

Here's an example of a rev0 bug I needed to fix. This is my hacky fix for a wiring error in the capacitor network which the MAX238 RS232 driver/receiver IC uses to drive its internal voltage converters...

The second revision fixes these bugs in the prototype:

A few other, more cosmetic, problems are also fixed in rev1:

New features in rev1 include

So: I'm about to start populating the board. The last one took about 8 hours to solder; this one should be quicker, as I will be doing a lot less testing as I go along. I also won't be socketing all the ICs this time around; I'm only going to socket the expensive ones.

Wish me luck...

It has been quite a while since my last update, and the project has moved forward a long way! I’ve made a lot of progress with the operating system software (I’ll be writing a log about this soon) and the hardware has advanced a bit too.

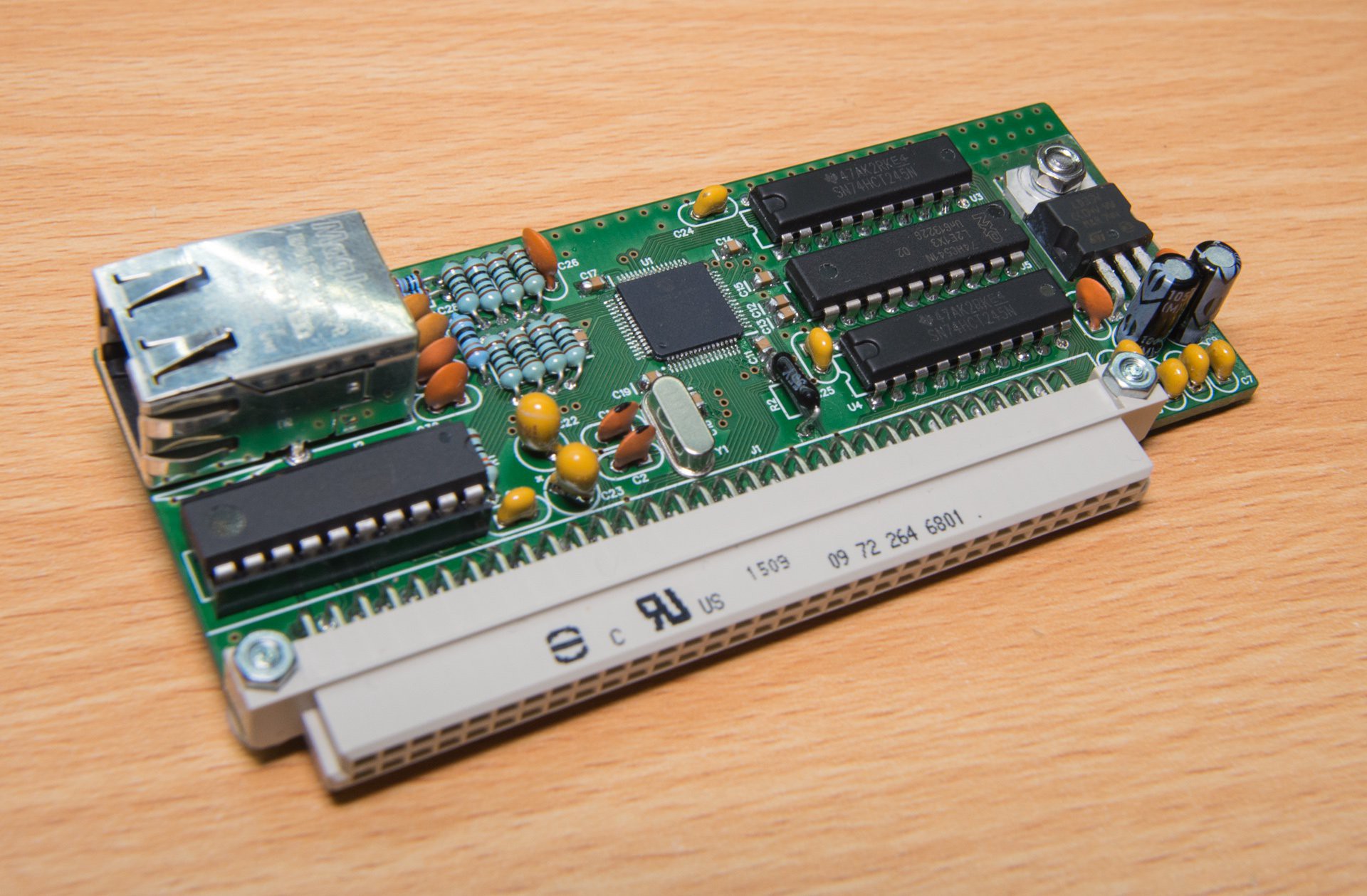

I designed a 10/100Mbps Ethernet peripheral card, based on a Microchip ENC624J600, for the system. This enabled me to validate the motherboard’s peripheral interface design, and - more importantly - to start writing networking code in the operating system. Here’s a picture of the bare pcb next to a populated board.

The bare pcb is actually rev1 (i.e. the second version of the board - I start my revisions at 0). It contains two minor fixes to the rev0 design.

I mentioned in an earlier post that I'm trying to keep the whole design as close as possible to Motorola 68000-era (i.e. 1980s) technology. As time goes by, that's proving to be more of an aspiration than a rule set in stone. When considering designs for a network card, I looked at a few 80s/90s-era Ethernet controllers but - unsurprisingly - none were as capable or as easy to use as the ENC624J600. Also, magnetics (i.e. Ethernet transformers) suitable for these old parts are now really hard to find. I'm keen to avoid using parts that must be scavenged from ancient PCs, or are only obtainable on eBay, so I decided to use a modern part in the design. The ENC624J600, and a few of its decoupling capacitors, are (so far!) the only surface-mount parts I've used in the system. I admit that my desire to get the motherboard attached to a network trumped my desire for that pure '80s look.

The ENC624J600 is a really nice chip. It provides an integrated Ethernet MAC and PHY, has a built-in encryption engine (albeit a slightly buggy one…), has 5V-tolerant inputs, provides 24KB of buffer RAM and is extremely configurable. What's not to like? There is even a 16-bit data bus interface - ideal for the MC68000/68010 - and the chip glues to the system bus very easily. Most importantly of all, Microchip’s data sheet for the part is excellent. It's a 3.3V part, and it's fairly thirsty, hence the enormous TO-220 LDO at the right-hand side of the card.

I've byte-swapped the data bus in this design, meaning that the upper half of the ENC624J600's data bus (D15...D8) is connected to the lower half of the MC68000's data bus (D7...D0), and vice versa. The ENC624J600 is an inherently little-endian device, unlike the big-endian MC68000. Sadly the world is now overwhelmingly little-endian (boo...), so - while Ethernet header and footer data is big-endian (yay!) - the contents inside packets is typically not. Byte-swapping the data bus in this design saves me the effort of swapping received bytes around in memory, thereby increasing the overall performance of the interface. I've used the same byte-swapping trick in the ATA interface on the rev1 motherboard - more on this in a future log.

I have written most of a driver for the ENC624J600; the operating system is able to configure the part, establish an Ethernet link, and transmit and receive packets. The motherboard peripheral interface design incorporates a way for the operating system code to automatically detect and identify plugged-in peripheral cards, so the OS can locate the card and start its driver during the boot process. There's no reason why I couldn't plug additional Ethernet cards into the motherboard, if - for example - I wanted to create an extremely low-performance network router.

Here’s a picture of the Ethernet controller card installed in the motherboard.

I’ve also started work on a network stack in the OS code. So far it’s quite minimal - it knows how to handle incoming Ethernet packets and route them to appropriate protocol handlers (IPv4, ARP, etc.) Eventually I hope to have a working TCP implementation, but that’s going to take some time. For now, I’m happy to have reached a point where the operating system can, using a background process which listens for incoming packets, respond to ARP requests sent by...

Here's another picture of the board - this time with RAM modules, ATA CompactFlash card, RS232 cable and power supply plugged in.

The board requires a regulated 12V input. It generates a 5V logic supply using an LM2678 (the package mounted to the large heatsink at the rear of the board). A four-pin Molex socket provides 12V and 5V for an external hard drive. At the moment my mass storage is a CompactFlash card on a CF-to-ATA adaptor board.

The serial cable connects to a USB-RS232 converter, which is plugged in to my development PC. The PC runs an Ubuntu virtual machine that hosts an m68k-elf-gcc cross-compiler and toolchain. I use PuTTY for interactive sessions with the board.

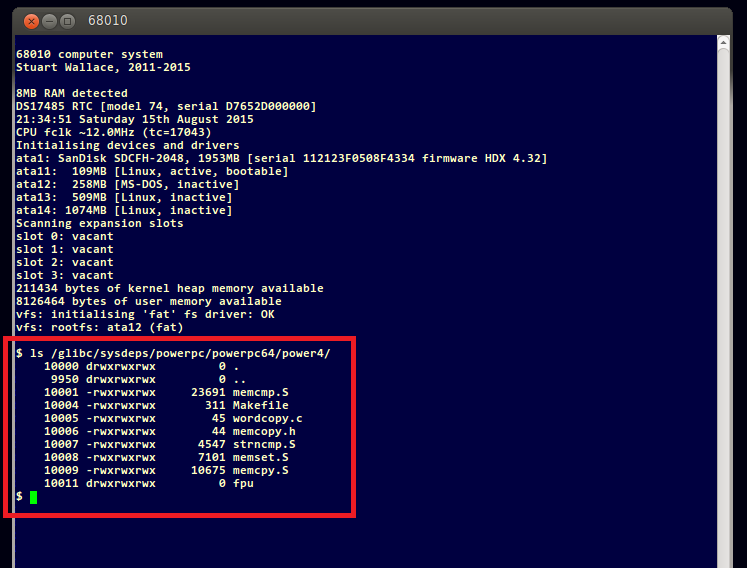

I'm currently working on file system support in the OS. So far I've written a minimal virtual file system (VFS) abstraction, and the beginnings of a FAT file system driver. I'm working on the FAT file system first because it's extremely easy to implement. I am also in the process of resurrecting some old ext2 driver code that I wrote a few years ago. My goal is to prove the viability of the VFS design by supporting two different file system types in a way that's transparent to the code accessing the code accessing the files.

To test the system, I partitioned a CompactFlash card, created a few ext2 and FAT file systems on it, and copied a bunch of files and directories into each file system. The 68010 motherboard is able to read the card's MBR and partition table, and can expose individual partitions as block devices. It's a bit like the Linux block device abstraction.

I'm now at the point where I can traverse a FAT file system and list files in a directory, which is nice :)

The picture below is a screenshot of a serial terminal session between my dev PC and the 68010 system. It shows the system booting, and the output of an "ls" command.

(The references to powerpc are irrelevant - I just happen to have a copy of glibc on this file system)

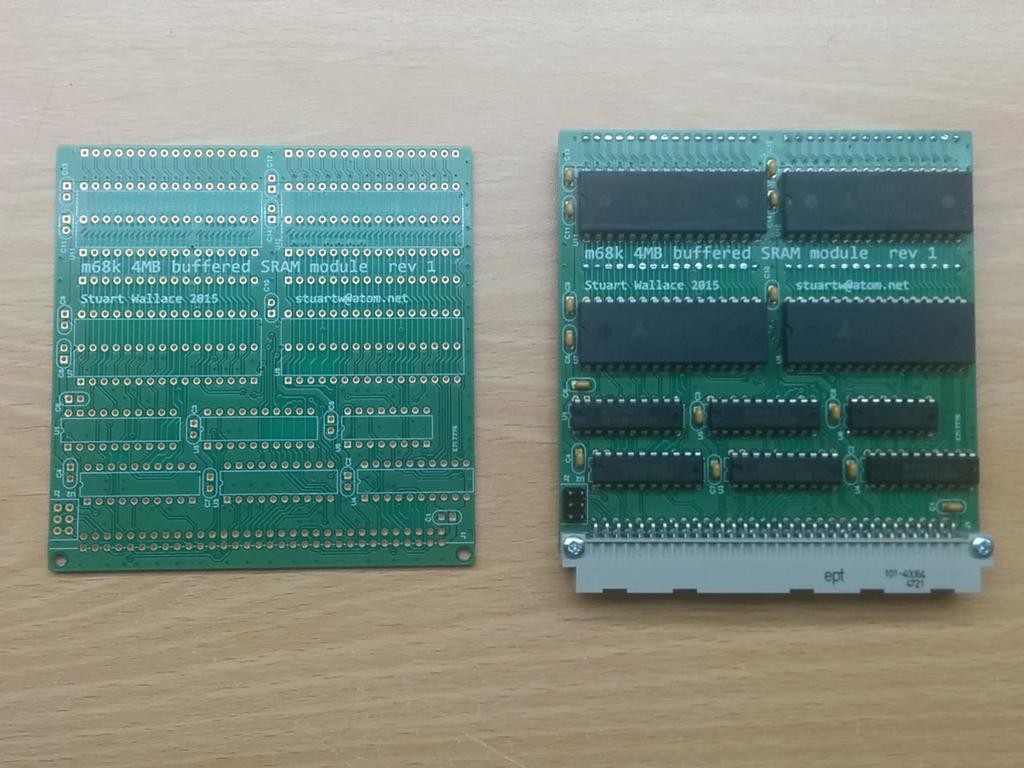

1/2/4MB RAM module (this one is 4MB), before and after assembly

Create an account to leave a comment. Already have an account? Log In.

Would it be possible to get the schematic as a pdf? I'd like to try creating an SMD version of this in kicad, and since I'm on linux, I won't be able to use diptrace (might possibly work in wine, haven't checked that option yet). This project just seems too good to not to make an attempt at continuing it.

I'm very interested in hearing of any updates to this project. Very Cool !! HSS

This is the most ambitious and impressive project I have EVER SEEN. I take my hat off to you, sir. Is this truly just the work of one man? Insanity!

Created a Hackaday account just to comment on this project.

Very nice project, would like to see it get going again lol

Anyways, I'm starting my own 68k project to get my hands dirty with electronics again and want to build a 68k puter and a 8080A puter and work my way up to more complex projects with the somewhat end goal of building a Engine puter.

Ur work has inspired me quite a bit and I hope you dont mind if I borrow some things from your setup lol

Hope all is well and good luck in the future.

this is one of the most inspiring projects i've come across - so inspiring in fact that i designed and built a little 68008 SBC as a stepping-stone to creating something like this! i'd love to hear if you ever went any further with the design, your VGA card, or the 030 project you mentioned. and at the very least i'd like to say thanks! especially for the structure and annotation of your code.

Hi there,

Thanks very much for your comments - I really appreciate them, and I'm amazed that this old project is still generating any interest! It's great to hear that my little project has inspired you to design some of your own gear.

Life intervened between me and my project work for a while, meaning that I only got about 50% of the way through the design of the 68030 system; I didn't push the VGA card much further in the end.

Thanks also for being the first person to say nice things about my code - I honestly didn't think anybody would ever look at it. Very little of it is complete, and there are undoubtedly many bugs, but if it has proven useful to you then it has served its purpose.

It would be good to hear more about your SBC project!

Stuart

consider selecting the surface mounted 68SEC000 part, it's the youngest chip in the series and has the added benefit of a selectable 8/16 bit data bus along with fully static operation for debugging.

I am wondering how you came up with the system boot, as I notice that you have two EPROMs, marked high and low. Are they based on some other kind of system, or is it so that it can be a system loaded from something else such as system on a chip?

Hi eepaul,

Sorry for the long delay in my reply! I have been busy with other projects, and with work. Were you asking about the two Flash ROMs on the motherboard, marked "odd" and "even"? If so, the answer is simple: the MC68000 has a 16-bit data bus, but the data bus on these standard ROMs is only 8 bits wide. I therefore use two of them to feed 16 bits at a time to the CPU. In this arrangement, one ROM contains data for all the odd-numbered memory addresses and the other contains data for all the even-numbered addresses -- hence the labels!

Stuart

I have two questions one of them is are you going to post any schematics on how to build one of these yourself? Also what sockets are you using to plug in peripherals like the Graphics card and the Ethernet card?

Hi manamster,

Sorry for the long delay in my reply! (I seem to be saying that a lot lately...). The schematics, PCB layout files and PLD source code for all of the system components are all freely available in github - there's a link on the left-hand side of the page. Here's a link to the directory containing the design files for the current motherboard revision - <https://github.com/stuartatpeasy/m68k-system/tree/master/hardware/Motherboard/rev1>. I'd be delighted if somebody else wanted to build their own board using this design, and (time permitting!) I'd be happy to help if I can.

Regarding the sockets for the peripherals and the memory cards: they're DIN41612 two-row types.

Stuart

I am definitely interested in building one of these. Are any of the schematics published?

Did you order any to sell?

Hi Vahe,

Sorry for the long delay in my reply! The schematics are all on github - <https://github.com/stuartatpeasy/m68k-system/tree/master/hardware>. You'll need a copy of Diptrace to view them; the free trial version of Diptrace should work fine.

I would love to see other people building these boards, and I'd be happy (time permitting!) to support anybody who wanted to do so. but it won't be easy. Several of the parts are rather difficult to find (especially the MC68010 and the MC68681), and there's a *lot* of soldering involved. Also, the operating system (also freely available on github - <https://github.com/stuartatpeasy/m68k-system/tree/master/ayumos>) is in a very early state - the network stack doesn't yet support TCP, I have barely implemented any system calls, memory-management is practically nonexistent, etc etc.... If you're still interested, I salute you!

Stuart

Would it be hard to implement ISA or PCI with some not too recent CPLD's (to keep the vintage spirit with PLCC and not go to the present BGA) ? Then you could recycle a VGA card. I also like this project that may inspire mine because I have just started to gather similar components found in the attic: a 68010 that I had from the Amiga era, several 68681 and 68230. Then some fast SRAM pulled in the early 2000's from discarded 386/486 boards, but they are low density chips: 16x TC55416P-15 or 24x TC55328P-25. Would 128K with the 416's be enough to start with or should I look for 8 more 328's to get 1MB ? Then for the Flash I have a tube of Am29F040B PLCC. My first target application should be a SCSI to IDE emulator (can't stand the modern scsi2sd, don't want to learn AVR or ARM, SD is too small to handle and too easy to lose, have many old CF cards that are still be larger and faster than the classic 68k era spinning rust), so I ordered a WD99C93A to be used as a target. On the IDE side, a 68230 should be enough to interface with a CF card (I have already used CF with 8052 and 8255, or 16-wide-bit-banging the CF with a P89V51RD2). For the glue logic, I found discarded NOS of Lattice isp1032E, it may be enough after comparing with other recent 68k SBC projects. Last, has anybody experience with DMA, do I need a 68440 DMAC ?

Hi silicium,

Wow, this is probably the longest I've ever taken to reply to somebody's comment. I'm very sorry about that! In case you're still interested in my reply, here it is...

I think it would be entirely possible to implement ISA in a reasonably "vintage" CPLD. I looked into it during the early stages of the project. What put me off was its relatively low performance, and the fact that it's *very* 8086-centric. I ended up implementing my own peripheral bus, which has a 16-bit non-multiplexed data bus and runs at the system bus speed. This gives significantly better performance than ISA, but obviously has the (major) disadvantage of preventing me using commercial ISA cards. PCI is a different matter. The big drawbacks of PCI, from my perspective, were a) it's a closed standard, b) it's a 32-bit bus, and c) it operates far faster than the 68010 on on my motherboard.

Regarding the RAM you salvaged: you can do a lot with 128KB. My 68010 system has 8MB of RAM, but I have not yet reached the point where I need a fraction of that amount. Most of the RAM is currently used for caching disc blocks; this is (somewhat) optional, and I'm sure I could get the OS up and running in 128KB.

Regarding a SCSI to IDE emulator: this is an interesting idea, but it might be worth considering implementing an IDE interface. This is exceptionally simple: in my design, it's about four 74-series chips. This gives you the ability to use pretty much any CF card, and a lot of ancient HDDs.

A DMAC is certainly a nice-to-have, but by no means essential. At this level of performance (12MHz CPU clock, 3MHz max bus speed, no caches) you're unlikely to be shifting a great deal of data around, and the processor is unlikely to be able to do much meaningful work while it waits for a DMAC to copy a few blocks from disc. I would like to include a DMAC in a future version of the system, but it adds a tonne of complexity to the hardware design.

Assuming you're still working on your project: good luck with it! I'd love to hear how you're getting on.

Stuart

Beutiful! Does it have any specific form factor or case?

Sadly no - there's no case (yet!). I would quite like to put it in an enclosure, but I have absolutely no skill in mechanical design -- I would probably try to use something off-the-shelf. There's a bit of a limitation in the design: the expansion cards present their connectors to the outside world along one side of the motherboard pcb, but the inbuilt serial ports are on the adjacent edge, at 90 degrees to the peripheral connectors. This was a rather silly design decision :)

Thanks for your comment! It's always nice to know that people are looking at my project :)

That's a sweet looking system. The heatsink on that switching regulator seems a bit overkill though. Does it even get hot? How much power does the system draw?

Hi Koen! Actually you're right. At a reasonable room temp (~20C) the heatsink doesn't get warm at all. The system dissipates about 3W with 8MB of RAM, an Ethernet card and a PS/2 controller attached. I specified the heatsink for a worst-case scenario: 50 deg C ambient (i.e. system mounted inside a case with no forced-air cooling), and 25W dissipation. Originally I budgeted for 5W per peripheral slot (total: 20W) plus another 5W for the system board itself. TL;DR: the heatsink is a lot bigger than it needs to be, but I'm a pessimist :)

Actually, that's not very clear. What I meant was: I selected the heatsink based on a worst-case of 25W system dissipation at 80% regulator efficiency. That gives me about 6.25W dissipation in the regulator, and the heatsink is rated for 6 deg C/W. So: I end up with the heatsink roughly 40 deg C above ambient in the worst case, meaning that it would take a fairly extreme ambient temperature to start overheating things.

Thanks very much for taking an interest - it's really nice to be asked about the system :)

To remain withing safe operating limits you can get away with a heatsink with a thermal resistance of about 16 C/W. As an example: http://www.mouser.com/ds/2/303/sink_ex-1076311.pdf

I made a few assumptions:

P = 25W

Vin = 12V

Tamb = 50C

efficiency = 0.84 (Vin = 12V, Vout = 5V, Il = 5A from datasheet)

The max safe temperature of the junction is 125C. With this in mind we can calculate the max thermal resistance of the IC and the heatsink combined.

Tjunction,max = 125C (from datasheet))

dT,max = (Tjunction,max - Tamb) = (1 - efficiency) * P * Rthermal = 0.16 * 25 * Rthermal = 75

Rthermal = 75 / (0.16 * 25) = 18.75

Now assume all heat is passed trough the heatsink and not trough the leads of the IC this would result in a heatsink with a thermal resistance of about 16C/W. Of course in reality the IC leads transfer heat to the PCB and it also conducts heat directly to the air. Running the device cool is of course a good idea to increase its lifespan, but you're barely even using 1/8th of that power supply, so if you would like to you could totally get away with a shorter heatsink.

@Stuart thanks a lot for sharing such a wonderful project! I have just finished my first WDC 65C02 based SBC and have been looking to move on to bigger and better things since.

I have really been inspired by your work and have seen some really great ideas to think about for my (hopefully upcoming) 68K based microcomputer.

I hope that you will continue to post updates for everyone to see.

- Billy

Thanks Billy! Your comment reminded me that it has been a very long time since I have written anything about the 68k project - I'll try to get some more updates live soon :) Recently I've mainly been working on the OS code; specifically, the network stack.

Good luck with your 68k project!

I am looking forward to more updates (software updates are great too *hint* *hint*).

On another note, where did you get your 68k? I have been looking on ebay but have also considered purchasing one off of digikey (for some reason they have the MC68SEC000 still in stock!).

@simongarstin33 (I really wish I could reply to replies in comments, instead of starting new threads...) Interesting to hear about the R6545 - I hadn't heard of it before. I looked up a datasheet and it does indeed look like a drop-in replacement for the 6845. It's not immediately apparent to me how it permits the host to access video memory, but I didn't look at the data sheet in much detail (I was at work at the time). I'll definitely keep it in mind :)

If your memory are fast enough, you can run the video memory bus at 2X speed and alternate access between CPU/video (see figure 8). Modern SRAM are very fast, so sharing memory cycles shouldn't be too difficult. Otherwise you have to wait until the video system is done with memory access e.g. at VSync/HSync (page 2-72). MUX the address/data (figure 5) to the memory and insert wait states at the CPU side when needed.

You can make your life a bit easier if the CPU and video clock are derived from the same clock frequency so that you know exactly when you have to feed the CPU or the video. Realistically, the 68000 memory cycle starts from S4-S7. This is the trick they pulled on the Amiga to interleave custom chip/CPU cycle to 280ns DRAM cycles. Yeah, you'll need to do these type of things in a state machine in a GAL or something.

Hi K.C! What you describe is reasonably close to the approach I'm taking. The video RAM bus is 16 bits wide, so (at 800x600x4bpp) each read cycle latches four pixels into the scan-out shift registers, which are clocked at 40MHz. This clock also drives a state machine which arbitrates memory access for the host CPU and the scan-out logic. With a 12MHz core clock, CPU reads and writes should require 0 or 1 wait cycles, depending on how well they align with the scan-out reads. Deriving the CPU and video clock from the same source isn't really an option in my system, unfortunately, and I wanted to avoid locking the CPU out until hsync/vsync, so this approach seemed like a reasonable compromise.

Thanks for your interest :)

The 6545 has some extra internal registers for READ/WRITING to video RAM, useful if your using an asynchronous CPU like Z80 etc. If your using synchronous type CPU 6502/6809 with a split phase clock then the 6545 can be used to share VRAM with no penalty in speed... Namely it doesn't nee to halt the CPU. With clever design the 68000 can be used with a 6845/6545 with no need to HALT the CPU when the Video Chip is Read/Writing to VRAM.

I know you don't want to make this a 'commercial' product... but turning it into a homebrew Self-Build kit for others to learn about computer design and architecture would be really COOL. Either as a Multi-board project or as a Single board design for other to build and learn !

Hi Simon! Thanks for your interest in my project :)

I would really like to share the project with others, and it would be great to see some people building these boards. One small problem is the cost: for it to be worthwhile, I'd need to order a *lot* of boards. The single-unit cost of the bare pcb from my preferred board manufacturer is about €80, although this drops to about €5/pcb in 100-off quantities. The cost problem extends beyond the bare pcb, though... I produced a full bill-of-materials for the project recently, and realised that I had used some rather expensive components! If there was enough interest, I might do another revision of the board using cheaper parts.

All the design docs - including schematics and pcb layouts - are on Github, and I'd be very happy to help anybody mad enough to want to build a board :)

Thanks again for your interest.

Stuart

Awesome Project... would be amazing to see this with a Video / Sound card !

Thanks! I'm working on a video card at the moment. It's going to be a fairly modest spec - probably 800x600 resolution and RGBI (16 colours total). I'm trying to keep the hardware for the whole project quite "contemporary", i.e. no modern stuff. I've also built an Ethernet card, which is working nicely - I'll post an update on this soon. I hadn't really considered doing a sound card -- I guess it would be quite easy to build something around e.g. a 6581 SID.

Thanks for your interest!

SID 6581s can be quite tricky to source and are getting rather expensive. some cheaper alternatives might be worth considering, though the SID chips are Good:

SN76489 ($0.50 each)

AY-3-8910/YM2149 (about $1.40-$2.0 each)

SAA1099 ($1.50 each)

You could use a YM2149 (Left Audio) and a SN76489 (Right Audio ) to give stereo and still be much cheaper than a Commodore SID chip ??

Some 'Old' Retro Video Chips worth looking at :

V9990 (Surface Mount) possibly one of the best 'Old' video chips (about $20 each) mainly PAL/NTSC with a few VGA modes

V99x8 Cheap and good spec giving MAX 512x424 , 16 Cols display (about $6.0 to $10 ) PAL/NTSC

V6636 basically an enhanced 6845 (about $4.0 each) VGA/ or PAL/NTSC

D72020 full Video display Processor with Line,Fill,Circle etc also cheap about $2.0 each. VGA/ or PAL/NTSC

There's schematics and stuff online for most of trhese ICs

I ordered some YM3812s. I'll let you know how I get on with them :)

@simongarstin33 - interesting suggestions :) At the moment I'm working on a video card based on a MC6845, some high-speed RAM, and some GALs acting as fast shift registers for pixel data. The 6845 is surprisingly capable - with a bit of trickery, you can get quite high resolutions out of it. The biggest issue is, of course, memory bandwidth. I'm shooting for a resolution of 800x600, which requires a 40MHz pixel clock. I can't use fast RAM, like DDR (too modern!), so I'm using some Cypress 15ns SRAMs. I think I'll be able to squeeze 4 bits per pixel out of the design, giving 16 colours total, while also enabling the CPU to access the frame buffer during scan-out. That's the theory, anyway :)

The MOS R6545 is a later version of the MC6845 you might be able to push it to greater speeds ?? It can also read/write VRAM via internal registers if required. Possibly worth looking at the datasheet it may also be pin compatible as a direct replacement for a 6845.

Become a member to follow this project and never miss any updates

By using our website and services, you expressly agree to the placement of our performance, functionality, and advertising cookies. Learn More

Tom

Tom

Colin Maykish

Colin Maykish

Jonathan 'theJPster' Pallant

Jonathan 'theJPster' Pallant

for video have a look at this interesting proposed image format from the 90's it claims to offer true color performance with only 16 bits. https://r0k.us/graphics/png16Tech.html#fc16 who knows it could be fun implemented in hardware.