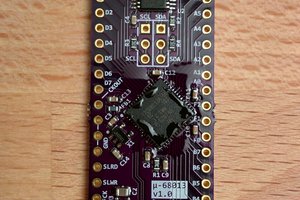

This little weird idea sprung in my head a decade ago, while playing with samples of SPI and I²C memories. I figured that the pull-up of the parallel printer port could work well for a I²C memory dongle with 8×64KB chips.

I went the SPI route and that's what I use today: that's 4 wires instead of 2 but speed and capacity have increased dramatically. They cost $1/pc or less if you search well (www.ebay.com/itm/252015791482) which amounts to 0.06$/MB or 60$/GB, it's not comparable to USB sticks or SSDs but it's much easier to hack.

Experience with the #SPI Flasher has proved that my programming algorithm works well so it will be interesting to extend it to N simultaneous bits (why limit to 8 bits when I work with a 16-bits CPU ?)

Fine control and extension can be controlled by an embedded 74HC595 (or more). For example, if more than one bank of SPI chip exists, a 2nd 595 will select which chips are selected. The reset pin can select all the chips in one cycle. SPI memories don't have an "/output enable" pin, only a "/chip enable" pin, and the 595 and 273 reset to 0, which is not handy if we want to use the data bus in both directions. More on this later...

Yann Guidon / YGDES

Yann Guidon / YGDES

forthnutter

forthnutter

Kaili Hill

Kaili Hill

Yin Zhong

Yin Zhong

Jeremy g.

Jeremy g.

If you wire the /CS decoding logic as SCK and the Si/SO[7:0] to the data line via buffers, then each read/write can toggle in the parallel data. Just need a GPIO to toggle the flash chip select line. :)