The dry diet is spreading to the output drivers. First, let's count the parts for the "normal" version where each of the 6 7-segment digits are driven by their own decoder:

- According to https://hackaday.io/project/8121-discrete-yasep/log/26997-redneck-disintegrated-7-segments-decoder there are 21 diodes for the BCD to 7 segments decoder. That's 101 diodes for the 6 digits.

- The output AND2 of one Johnson counter stage requires 2 transistors (incompressible)

- There are 6×7=42 segments (41 because of the tens of hours digit) hence 41 transistors and 82 resistors (though the leftmost digit can reduce the complexity a bit)

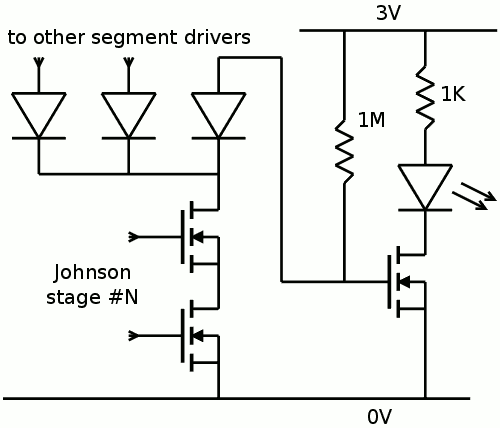

Here is the simplified schematic of how one output stage normally drives one segment:

What about saving some parts ? This requires multiplexing the decoder. Here is the summary of the parts count:

- 21 diodes because only one decoder

- 7 N-FET in series with the AND2 of each Johnson counter

- 6 P-FET for digit selection

- 2×7 resistors

It's getting more complex but the saving is significant.

However, the driving logic requires 6×AND3, or 6×6=36 transistors, plus 6 inverters (12 transistors). Fortunately there are some tricks to reduce this count.

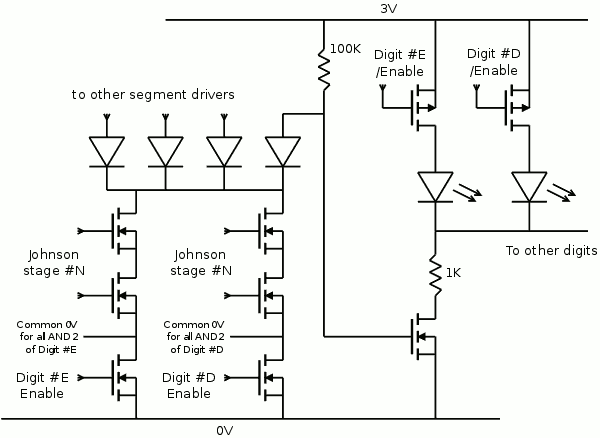

Trick #1 : save 6 inverters with just 6 resistors !

Solution: add a pull-up resistor between the gate of the P-FET and +Vcc then connect the gate to the corresponding common 0V of the AND2 gates. This is not "kosher" since the pull-up will draw power when the digit is enabled but A) only one digit is enabled at a time B) under 3V, that's 30uA with a 100K resistor. And C) the LED draw much more anyway.

Trick #2: factor some AND logic directly in the digit's common rail

This adds another resistor in series with the existing AND2 of the Johnson counter but this is not really critical because the current is pretty low (3V-0,7V)/100K=20uA so the actual drop is very close to the diode drop. The N-FET can pass 20uA with Vgs=1.5V already and all the N-FETs will be saturated. Furthermore this is a pretty slow part of the circuit (KHz range) so there is almost no RC overhead. Assuming 20pF for the gate, t=RC=2us ? This would add only a very light "shadow", proportional to the scan frequency.

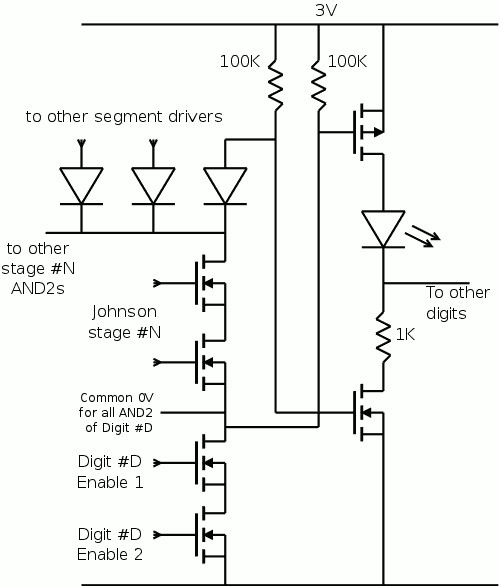

Where are we now ?

- 7 segments : 2 resistors and 1 N-FET each (14 res+7N-FET)

- 6 digits : 1 resistor + 2N-FET + 1 P-FET

==> 21 diodes, 20 resistors, 6 P-FET and 26 N-FET (32 FET)

This saved 9 transistors, 60 resistors and about 80 diodes, or 150 parts. The power consumption is also reduced a bit because only one digit is on at a time.

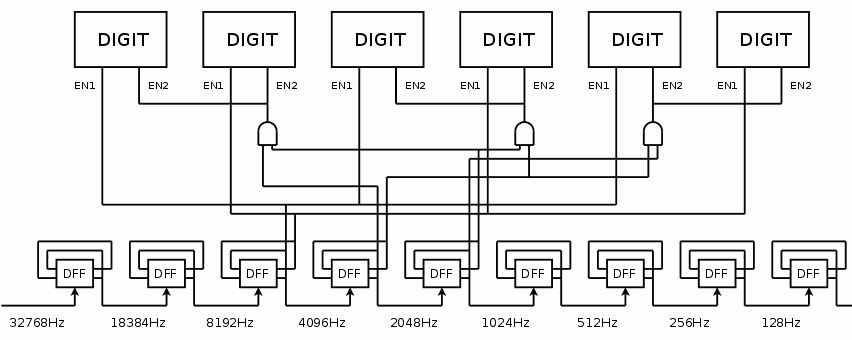

Now all we have to do is decode the Digit Enable bits.

I wish I could reuse the enable bits for the cascaded Johnson counters but they must be run only once per second. The refresh should run run at about 500 or 1000Hz to be visually 'nice' so the highest frequency is 8KHz. If I reuse the 5 outputs of the Johnson pulse generator, I'll consume quite a lot of transistors to make a AND10 (a least 20 transistors !).

However it's possible to use only 3 AND2, or 12 transistors !

Total : 21 diodes, 20 resistors, 44 FET (vs 41 FET, 82 resistors and 8+21+15+21+15+21=101 diodes), that's 84 parts instead of 224!

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.