Having completed building my version of Ben Eater's 8-bit breadboard computer nearly a year ago, building my own Apple 1 clone, building and looking into the inner workings of the Gigatron kit and studying the book Digital Computer Electronics it is finally time to design and build my own computer from scratch!

The main goal is to learn how to do this and see if I can actually accomplish this build. The computer itself must be usable as a learning tool for people that want to learn about CPU architecture.

That means lots of blinking lights and switches!

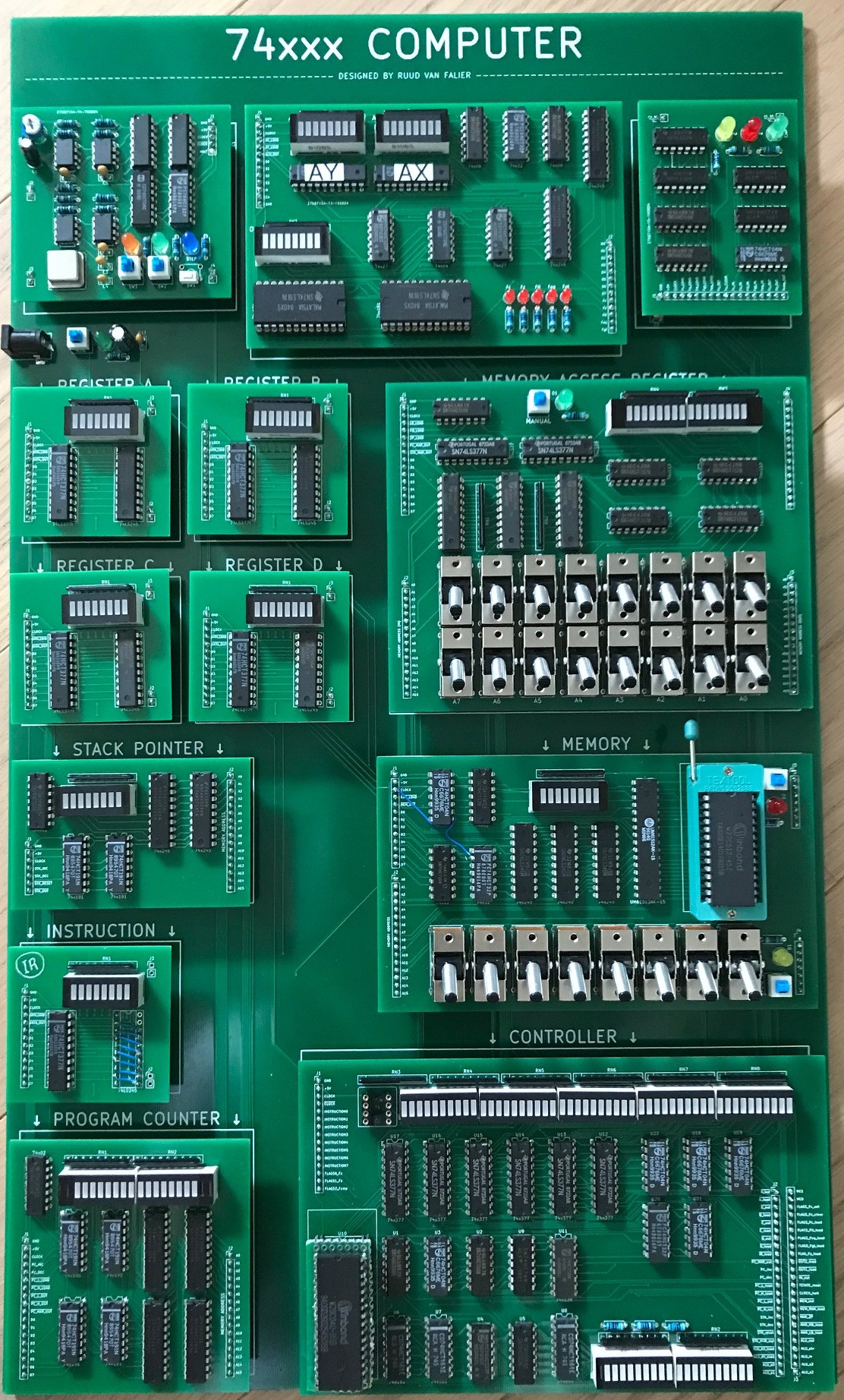

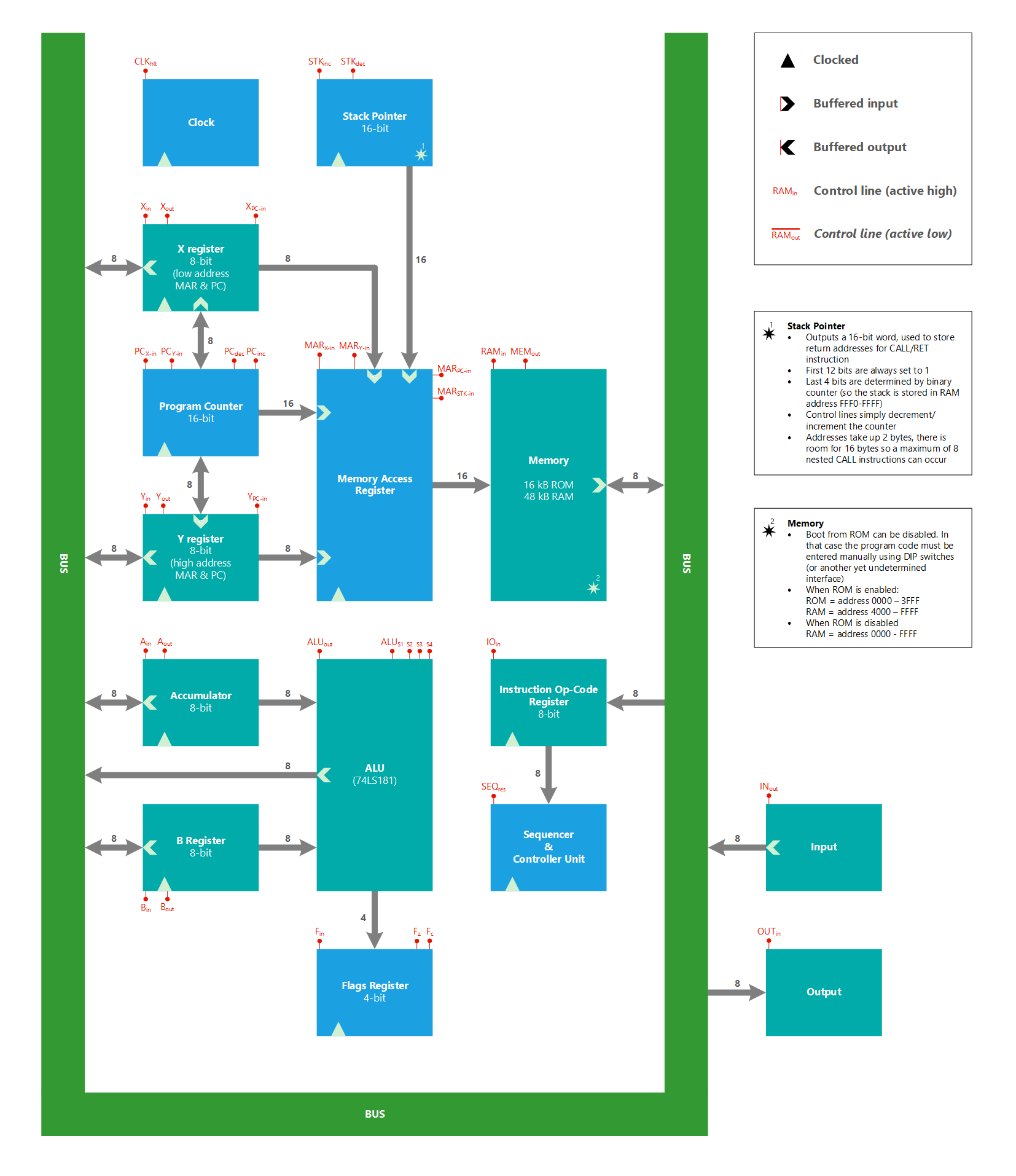

The plan is to build an 8-bit computer with 74xx (TTL/CMOS) logic chips that supports 64 kB of memory and a clock speed up to around 1 MHz.

-

PROJECT SHELVED - CHECK DM-02 PROJECT INSTEAD

-

Status as of April 10th, 2019:

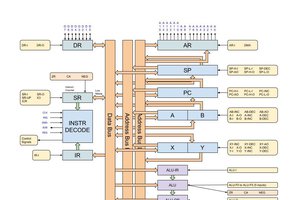

General architecture has been worked out as high level schematic.

Worked on instruction set, micro code, module documentation & general notes from time to time (see: Documentation). This is still work in progress! I'm planning to write a short piece of documentation on each of the modules, like I did for the Controller.

Circuit diagrams have been worked out in KiCad for all modules except for the Controller. These circuits were designed in KiCad (before the Logisim design was done) and not tested. All circuit diagrams need to be updated according to the Logisim design!

I've built a microcode compiler for the Controller's ROM image. This takes a source file which defines all the microcode and compiles it into a binary image that is loaded into the microcode ROM.

The 74xx Computer's instruction set has been implemented and its assembly language is fully documented. I've built an assembler to convert 74xx assembly to machine code.

The entire computer has been built in Logisim to verify that the way I had everything in mind is actually going to work.

While working on the Logisim design, I made several changes to the circuits that still need to be applied to the previously designed circuit diagrams.

Ruud van Falier

Ruud van Falier

2-Zons

2-Zons

spudfishScott

spudfishScott

ammarbhayat28

ammarbhayat28

Michael Morton

Michael Morton

How do you plan to implement the instructions? WIll they be hardwired or microprogrammed? Hardwired is easy for a Load or Store instruction but difficult for a multiply instruction.