-

HDD crash!!!

08/05/2018 at 00:09 • 3 commentsI managed to crash my hard drive. With the VHDL designs and DEXT Meteor schematics.

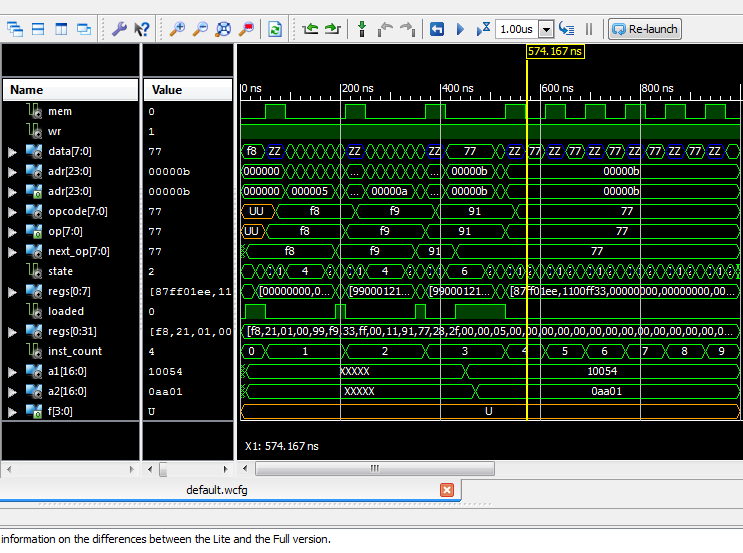

Sooo.... That really sucks. I hadn't backed up the data, but I realized there were older copies of the CPU designs on my other drive, in my desktop computer. It turns out the older CPU is actually faster (with less features however), by about 2 ns. When your FPGA project is running at 100Mhz though, that's a big difference.

The hard drive is probably toast, but I will rebuild!!! I will never surrender... XD

[edit] - I am going to use this terrible occurrence as an oppertunity to more easily upgrade the CPU. It will have a higher bus width and less states per instruction, so a higher instruction throughput. I don't know what I am going to do about the missing schematics yet though...

-

Parts Arrived! Prototype flaws but mostly works.

07/21/2018 at 04:57 • 0 commentsThe parts for the prototype came about 3 days early from LCSC and EasyEDA!

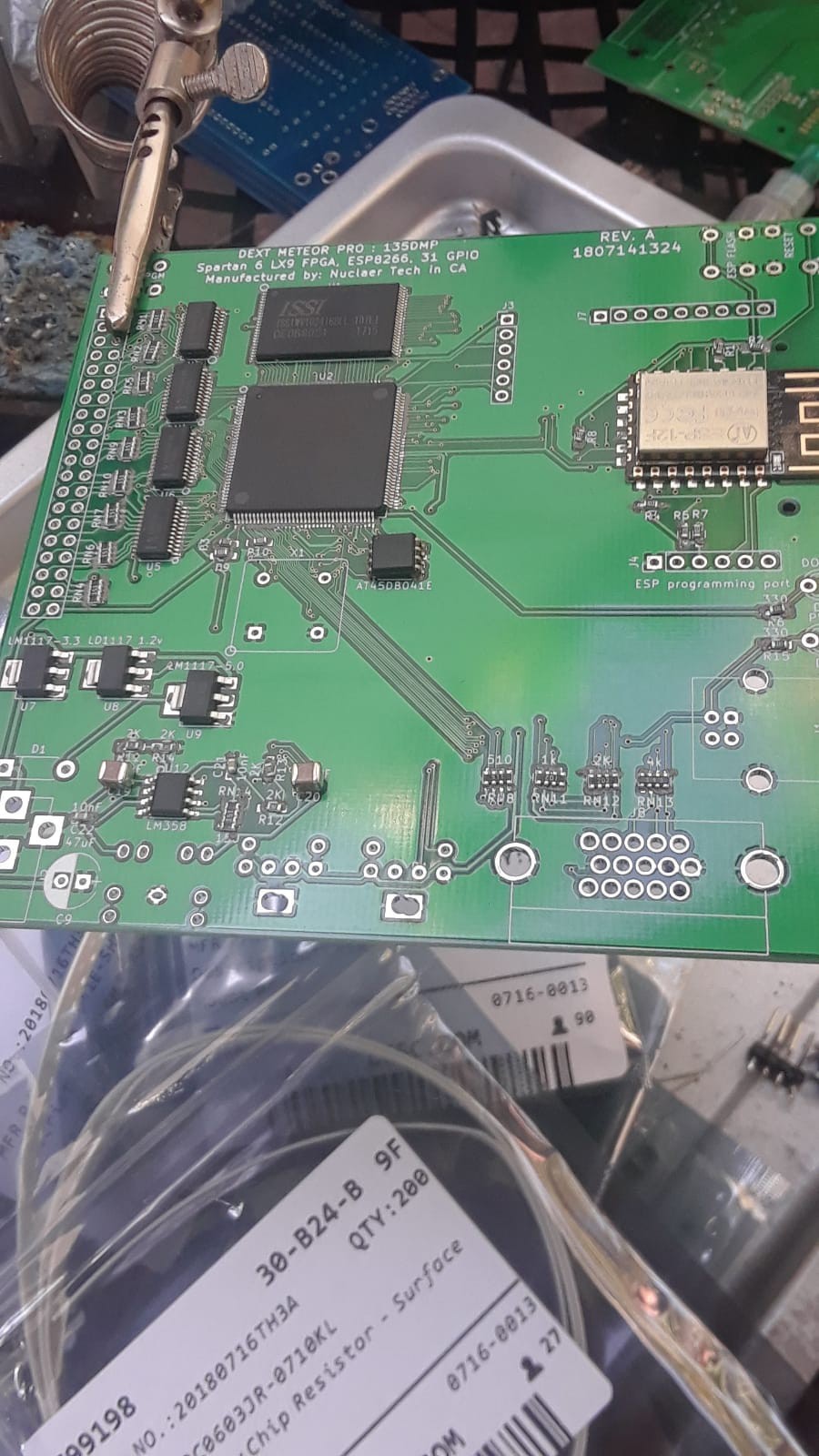

I don't have a solder stencil yet, so I used my solder paste for the whole board. I must say I've gotten somewhat good at soldering .5mm pitch ICs, considering only two pins had a joint. Trick is so simple yet so true: less is more. Use a tiny bit of paste and it works!

![]()

Top of board before being put in my toaster oven On the flip side, my PCB has a pretty bad error in it: the SRAM pinout is completely wrong. When I plugged in the board the 3.3v regulator got hot and the SRAM chip started getting warm. I had to cut the ground connections to salvage the board.

![]()

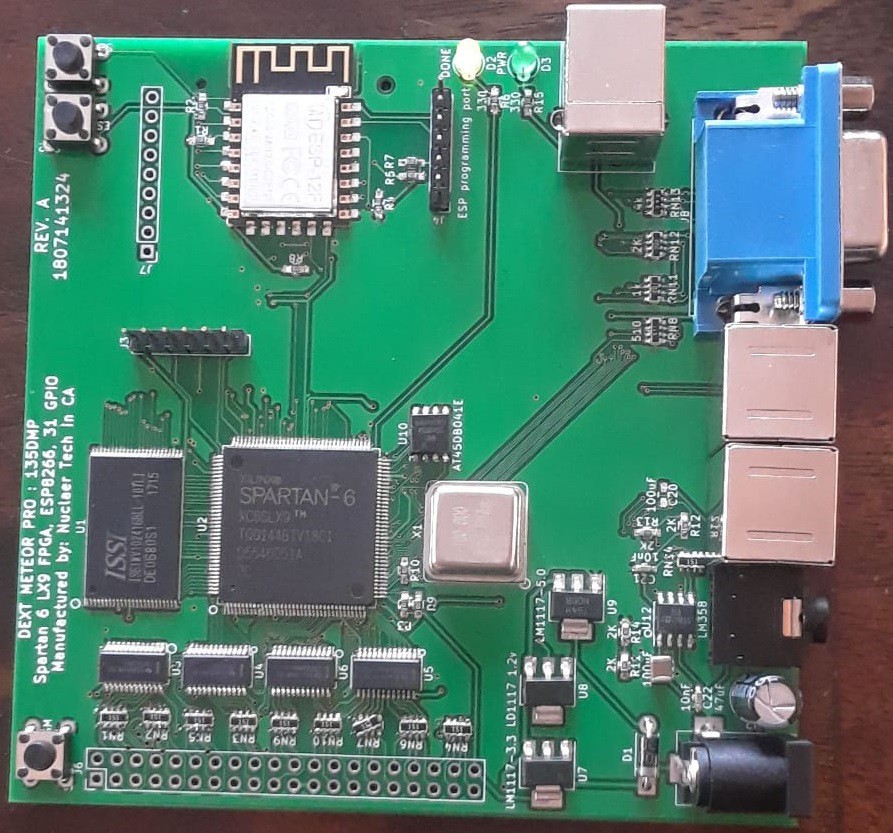

The completed board before cutting SRAM ground pins, with a few trivial errors Anyway, I finally connected the board to ISE iMPACT and it recognized the FPGA! So the board works. Time to start testing my compiler on real hardware!!

-

Creating a cross compiler, and parts on the way!

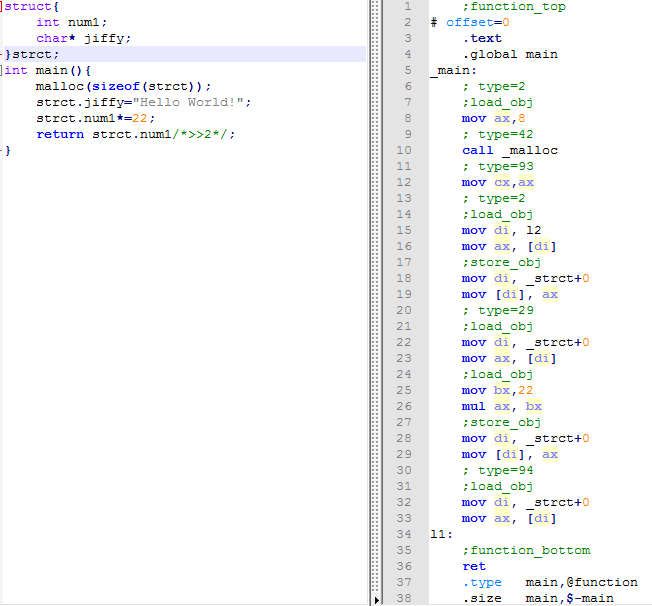

07/20/2018 at 01:03 • 0 commentsI've been writing a compiler backend for VBCC and am now getting some assembly output. I'm starting to get the hang of the compiler's internals and am writing and compiling test programs to test the compiler.

Here is one of the test programs I made:

There is some assembly that was generated either inefficiently or incorrectly, but for the most part it's good. This is the third program I have written and the other two now compile fine. At some point it will be able to compile itself!

Also, I have ordered the parts and boards for the computer itself and they will arrive in a few days.

Happy Hacking!!

-

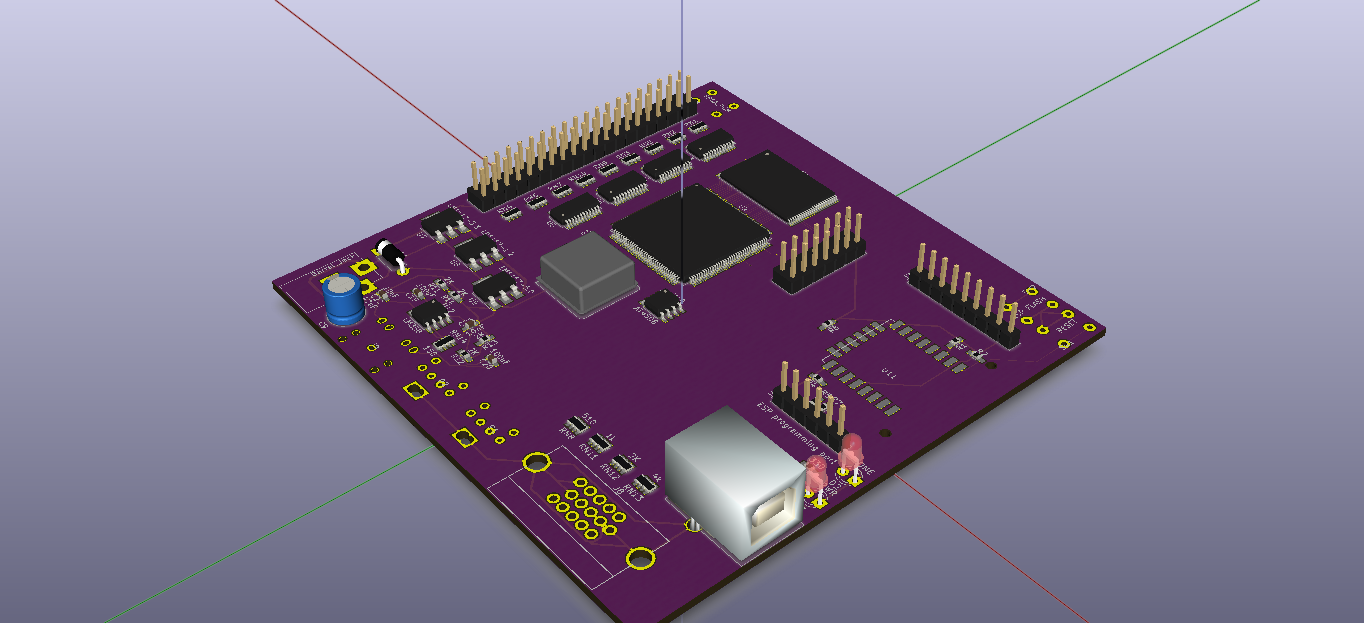

Finished the PCB design for the prototype

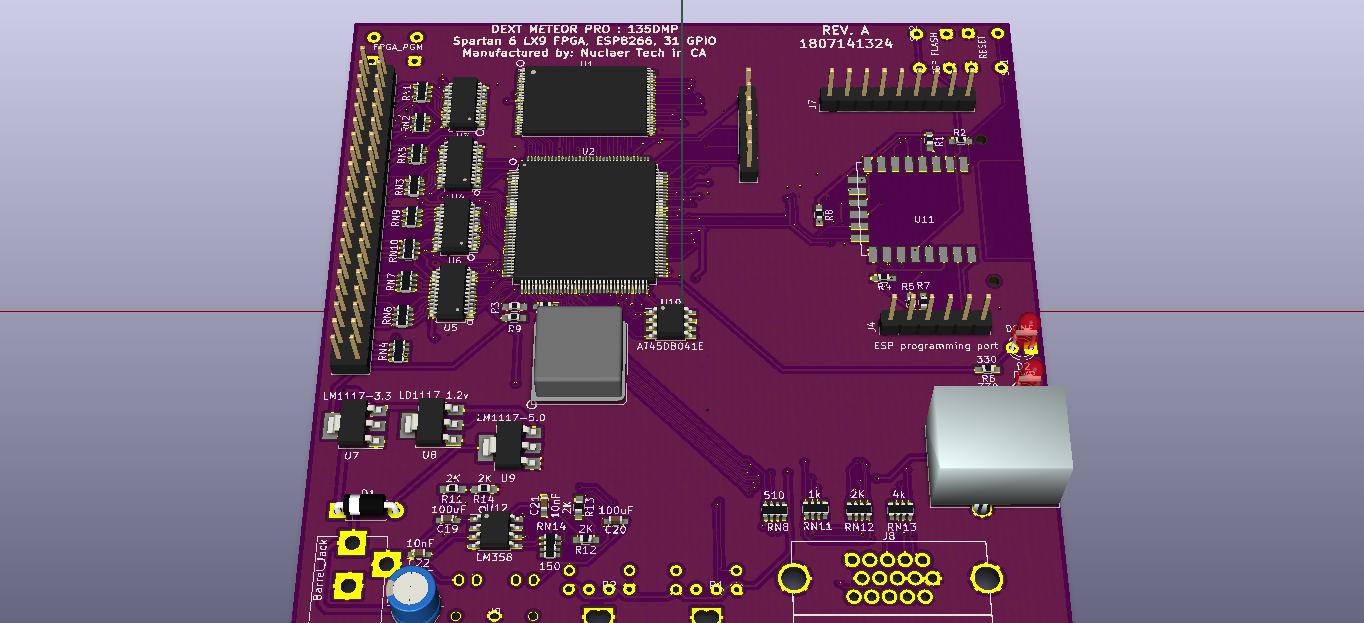

07/14/2018 at 21:02 • 1 commentKiCad's Pcbnew didn't like my 420+ small connections (well, I didn't either, but...), but I got it done!

![]()

For some reason I love seeing the final result, how complex it is, with all those tiny connections.

I made the PCB rendering purple because we want to make the final product with @oshpark PCBs. We will also be ordering a solder paste stencil because the FPGA is a QFP-144, with .5 mm pitch and almost no margin for error to get a good manufacturing turnout. We will be getting our stencils from oshstencils.

For the prototype we will be getting cheap PCBs from EasyEDA to play with and get used to building the boards with.

-

Designing Hardware

07/13/2018 at 03:03 • 0 commentsI may be jumping between parts of the project, but I want to test on real hardware.

I have the board about 14% routed at this point. I used KiCad's 3D view to make this rendering:

![]()

I love that feature. At this point we have decided on all specifications of the computer.

Our audio output is a 3.5mm audio jack with both right and left outputs. They are connected via an LM358 to two FPGA pins.

The video output is a VGA output connected to the FPGA, which has 11-bit color. The video resolution is controlled by the FPGA.

-

More accurate specifications and FPGA design well underway

07/01/2018 at 04:10 • 0 commentsI have been working a lot on the FPGA design. I now have a more accurate idea of specifications.

short list of new specs:

- 100 Mhz Plasma Cortex CPU

- Spartan 6 LX9 FPGA

- 2 MiB of SRAM

- SD card for storage

- ESP8266 for WiFi and Bluetooth

- 30+ GPIO

- Audio and video - no specifics quite yet.

Detailed explenation:

First off, we are now going to use a Spartan 6 LX9 FPGA. They are much faster, and allow the system to run at 100Mhz (YAY!) - but just barely. about .5 ns slack. But doing pretty well!!

I don't have any experience with SDRAM controllers, so we are going for the more expensive, lower density, yet much faster option: SRAM. I don't want to play with any technology I am not used to for this project, maybe another project I will use SDRAM.

Not entirely sure about graphics or audio yet, ESP8266 for WiFi and bluetooth, and an SD card controller somewhere in there.

I will either build the graphics into the FPGA, or I will use the VLSI chip VS23S0100.

-

CPU development

06/22/2018 at 16:22 • 0 commentsBecause I have *zero* experience using premade CPU cores.

I had a great idea for a CPU design a while back and started building it in VHDL. I have been perfecting it for the DEXT Meteor project recently.

The architecture has 8 32-bit registers, including the stack pointer and program counter:

The architecture

ID Register Name 0 AX 1 BX 2 CX 3 DX (can be used as address) 4 SI (can be used as address) 5 DI (can be used as address) 6 SP 7 PC The architecture and instruction names are loosely based off of the Intel 8086, except 32 bit instead of 16 bit. The instruction set, however, comes from the Z80, except there are no extensions. There will be an ldir instruction to load memory, but also instructions like lodsb and stosb from the x86 series of CPUs.

I call it the Plasma Cortex (because plasma sounds really cool), and currently I am implementing a cache and better memory controller.

-

Hardware decisions (FPGA, or Z8S180 CPU?)

06/19/2018 at 19:18 • 0 commentsThe idea of the DEXT meteor is to create an easy to use, uncomplicated single board computer with the most processing power for it's cost.

So lets compare CPU specs:

SPEC Z8S180 FPGA Speed: up to 33 Mhz 50+MHz Max RAM: 1 MiB about 16 MiB CPU bits 8 up to 32 RAM type DDR SRAM Voltage: 5v 3.3v Estimated cost: about 50 USD about 65 USD The FPGA design is about 15$ more than a Z8S180 design. The processing power difference is HUGE though. Not only can an FPGA allow for a faster and bigger processor, it can handle all the glue logic and many peripherals. Also, the FPGA can have a bigger address bus, so it can be upgraded further.

These price estimates assume the following about the produced SBC:

- Installed RAM is 1 MiB

- comes with dedicated audio, video, 28 GPIO pins, and WiFi support

- Computer has a BIOS or bootloader of some kind in ROM, at least 2KiB

- Doesn't include mass storage options.

We decided to go with the FPGA because the greater processing power is awesome.

-

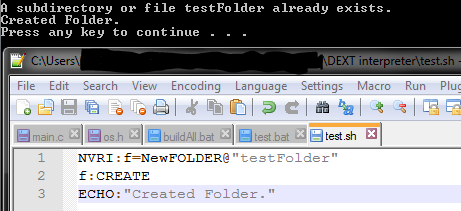

Started writing DEXT interpreter

06/16/2018 at 03:34 • 1 commentDEXT is a scripting language for use with the DEXT computer (but is multiplatform) that is more powerful than the terminal. The catch? I need to write an interpreter.

I am writing the interpreter in C++ so that I can compile for the DEXT computer. I came up with a simple program written in this early version of the DEXT language and interpreted it sucessfully!

There are only a few small parts of the language completed so far, but I'm doing good considering this is my first day working on the interpreter.

Here is what I have implemented:

- variables

- strings

- integers (only inc/dec operators for now)

- folder objects (only can create, not delete, for now)

- comments

- printing to the screen (a hello world program is possible!!)

- null object

DEXT Meteor:

The DEXT Meteor is a powerful and small FPGA computer with a unique OS.

london almida

london almida