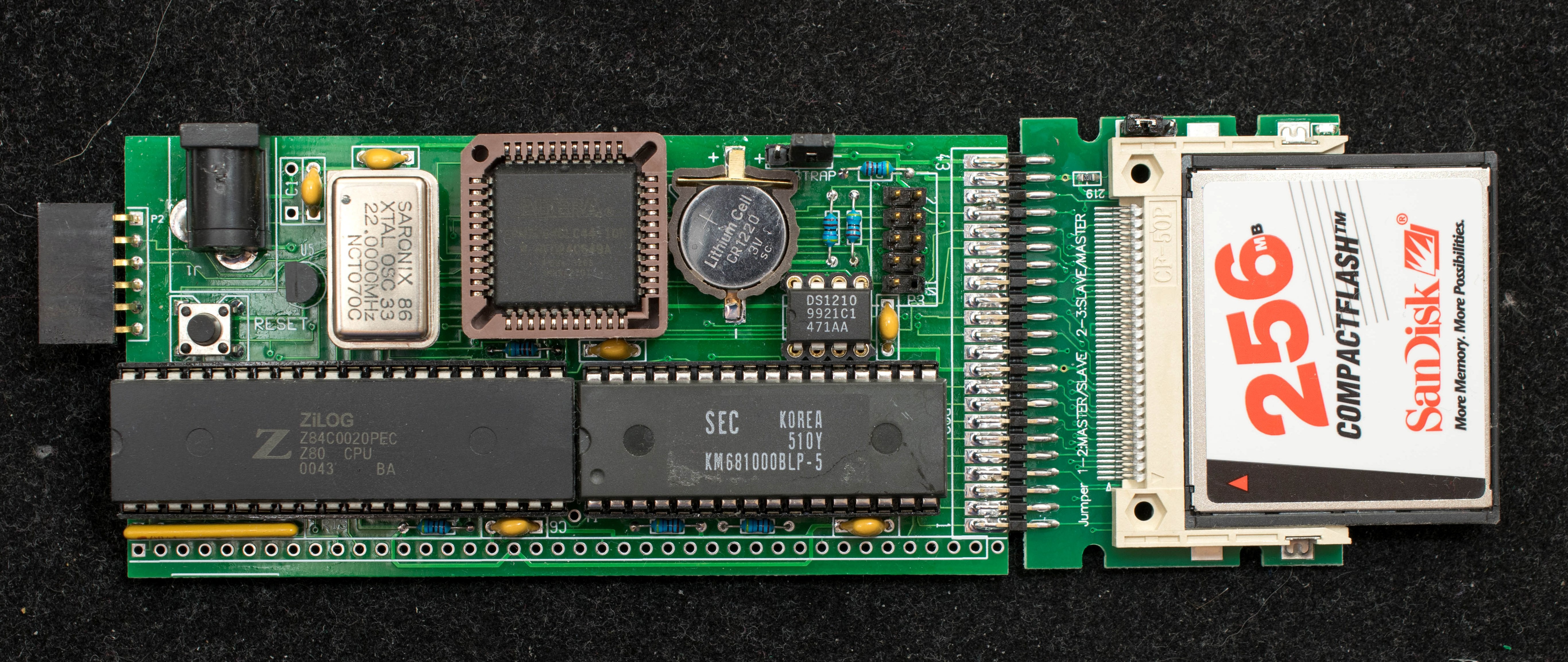

Outline of the project:

Introduction

- Bill of materials,

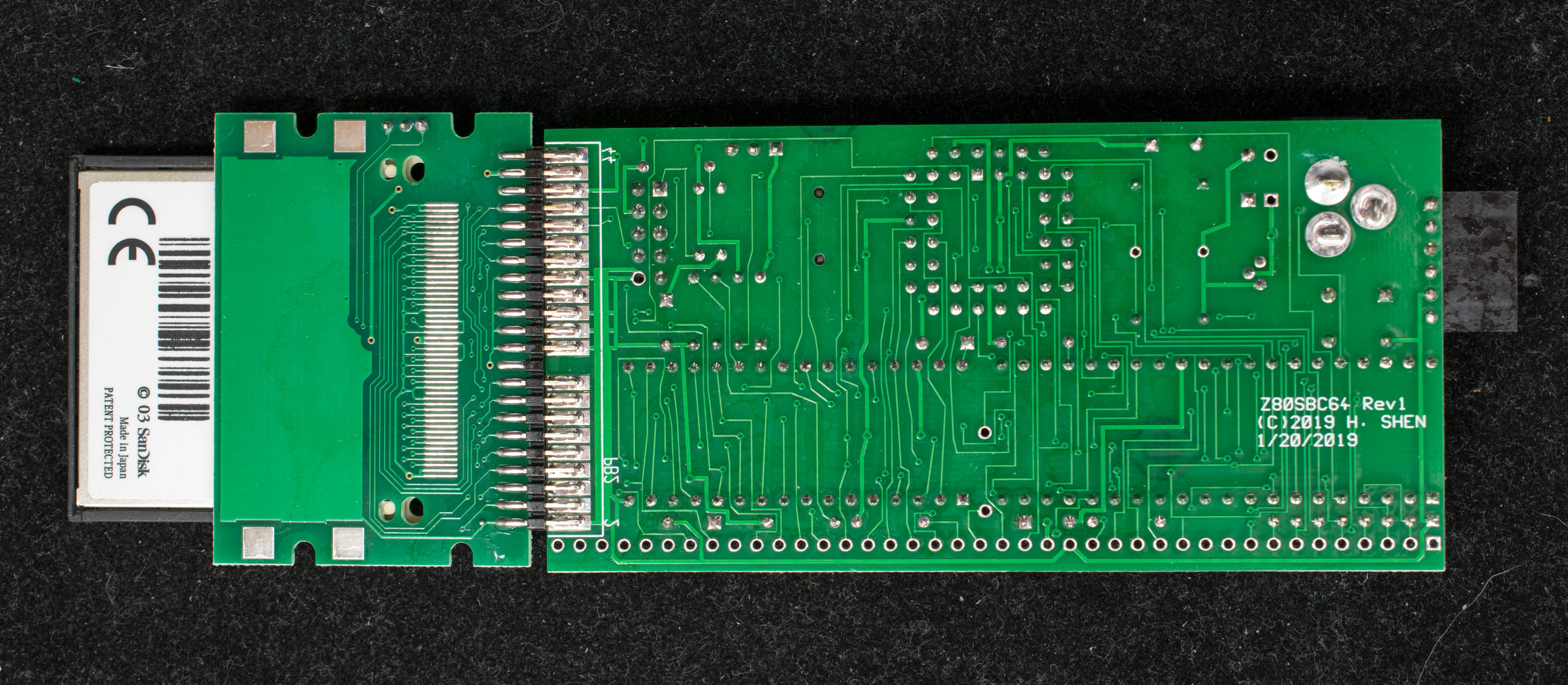

- schematic,

- pc board Gerber photoplot files,

- CPLD programming file

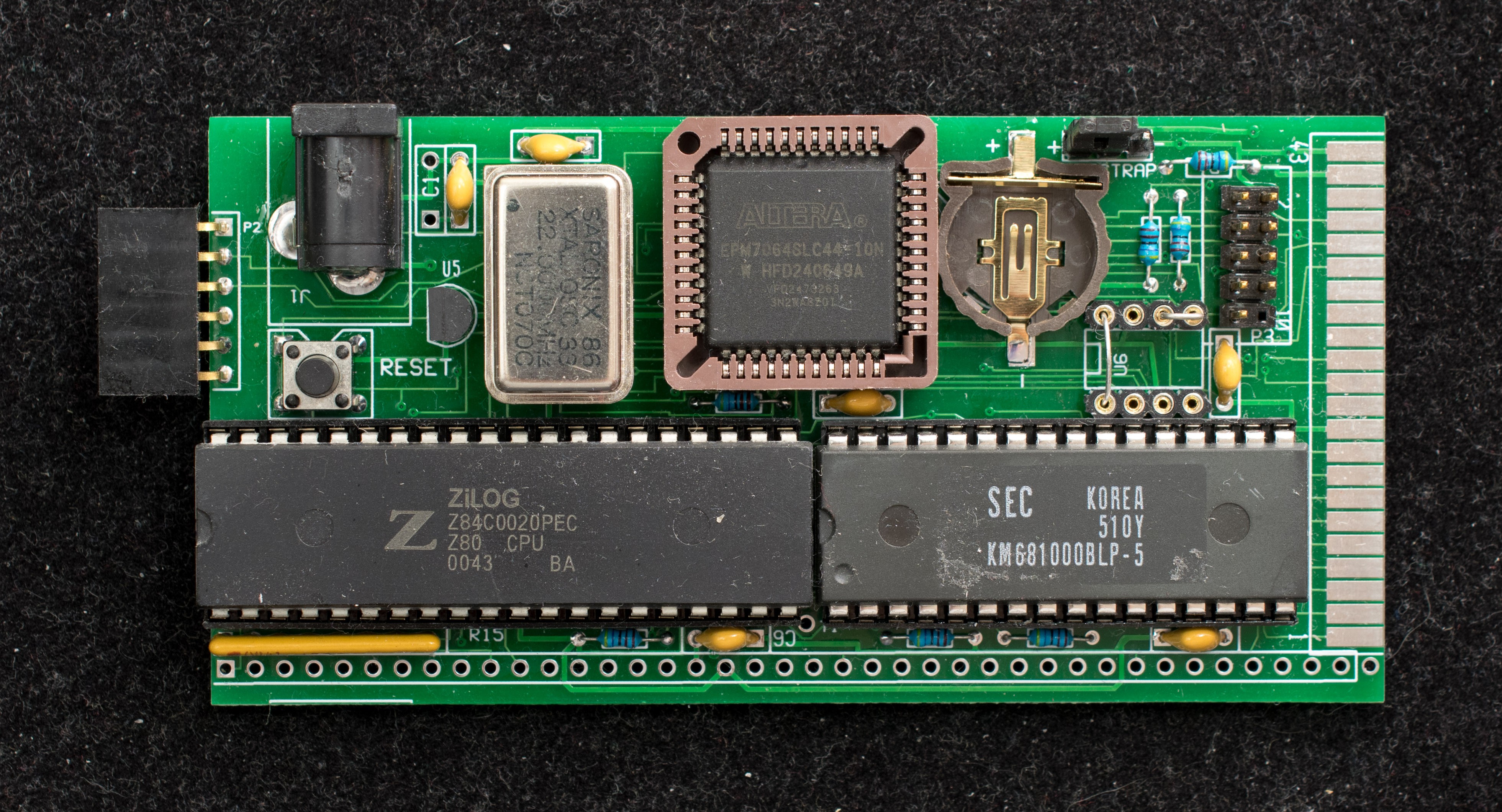

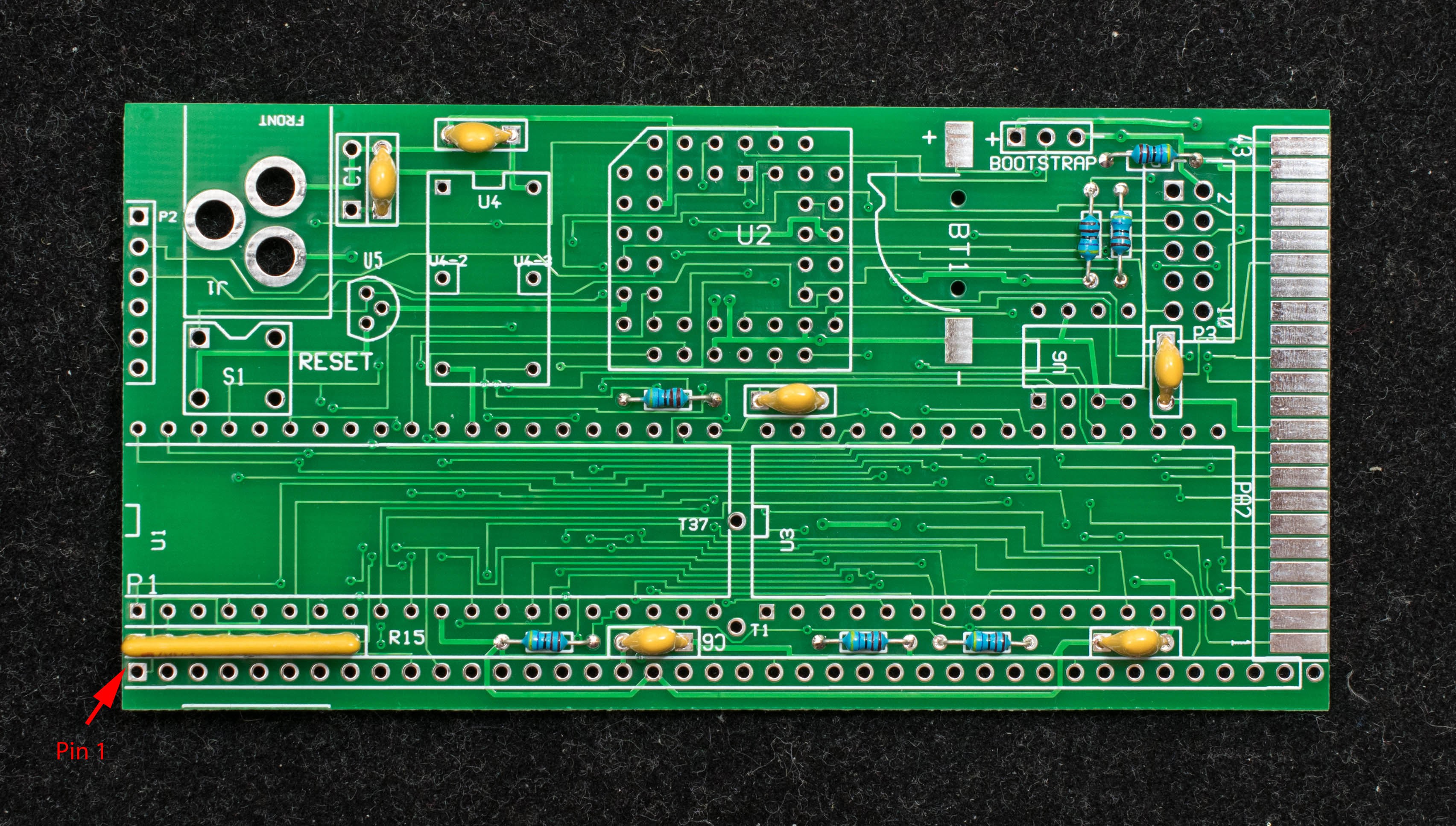

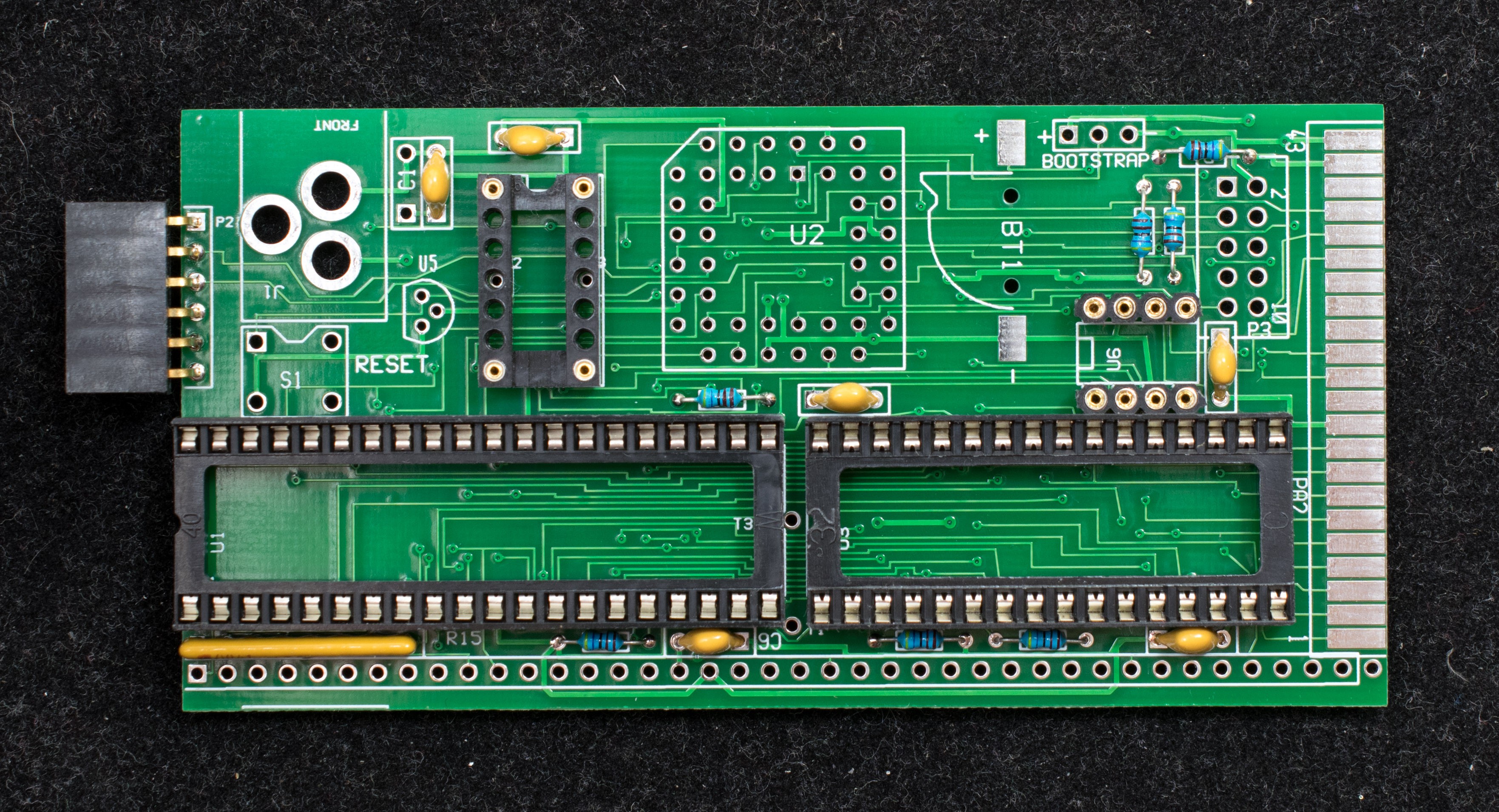

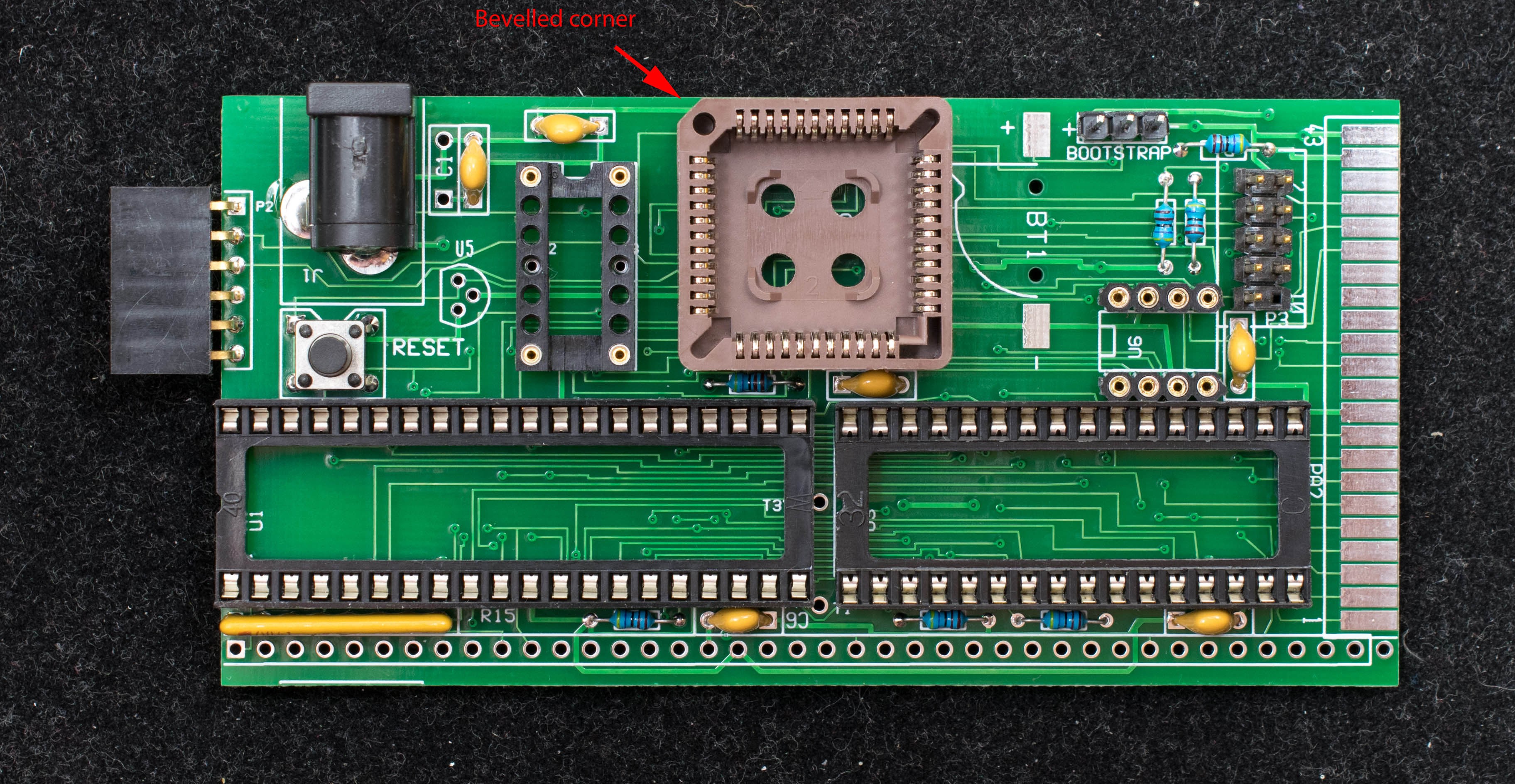

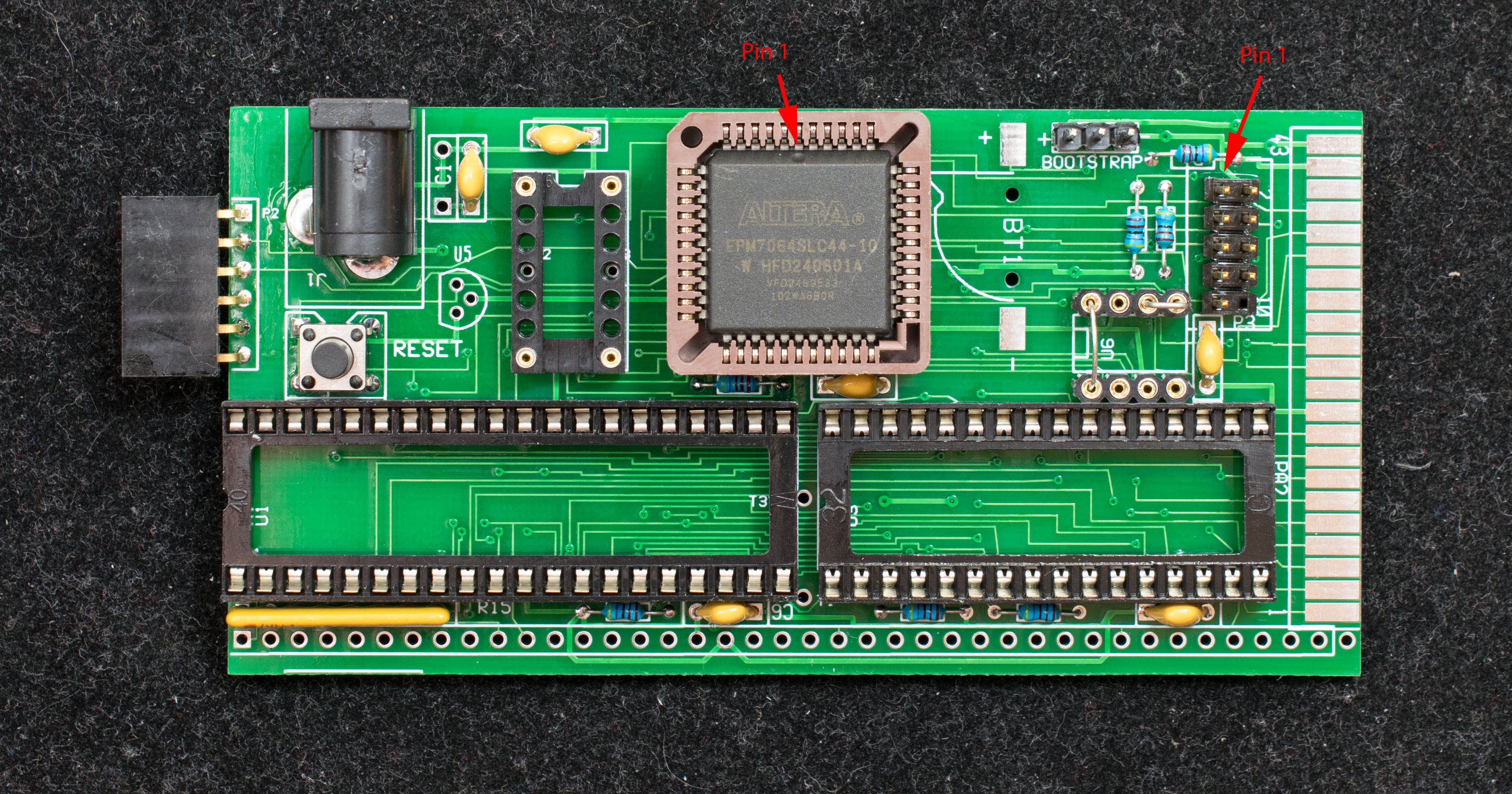

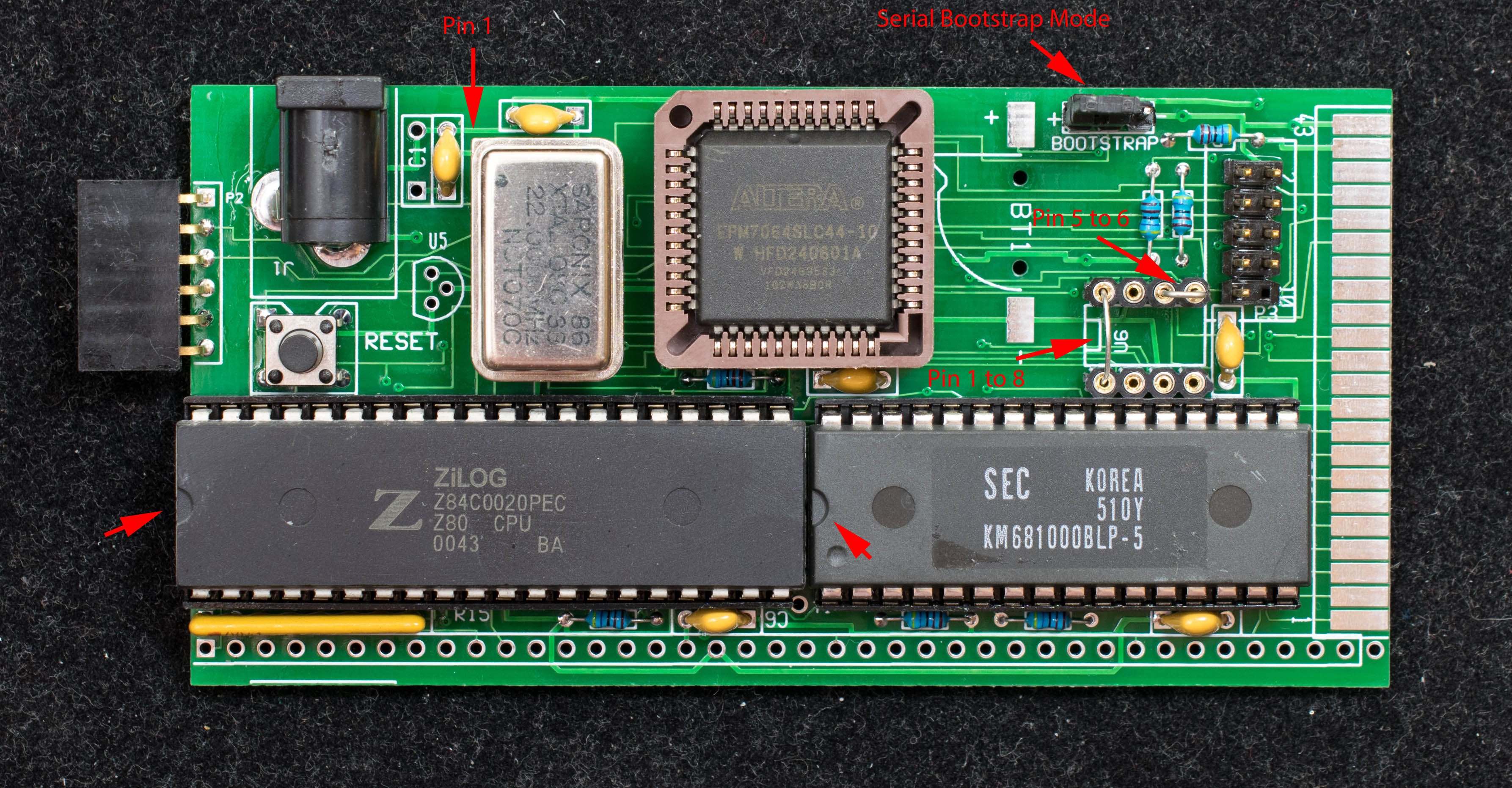

Stage 1 hardware

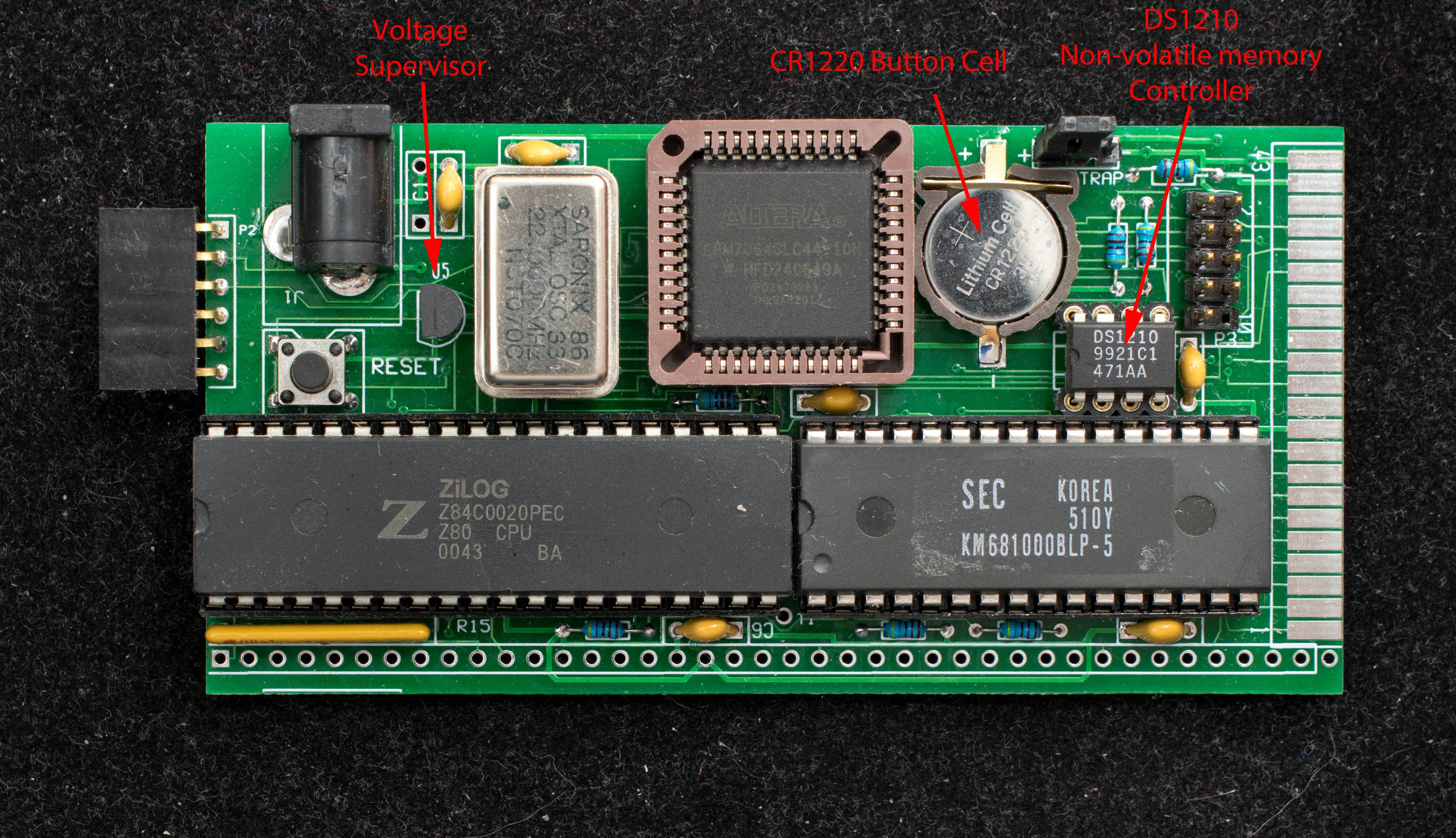

Stage 2, Non-volatile RAM

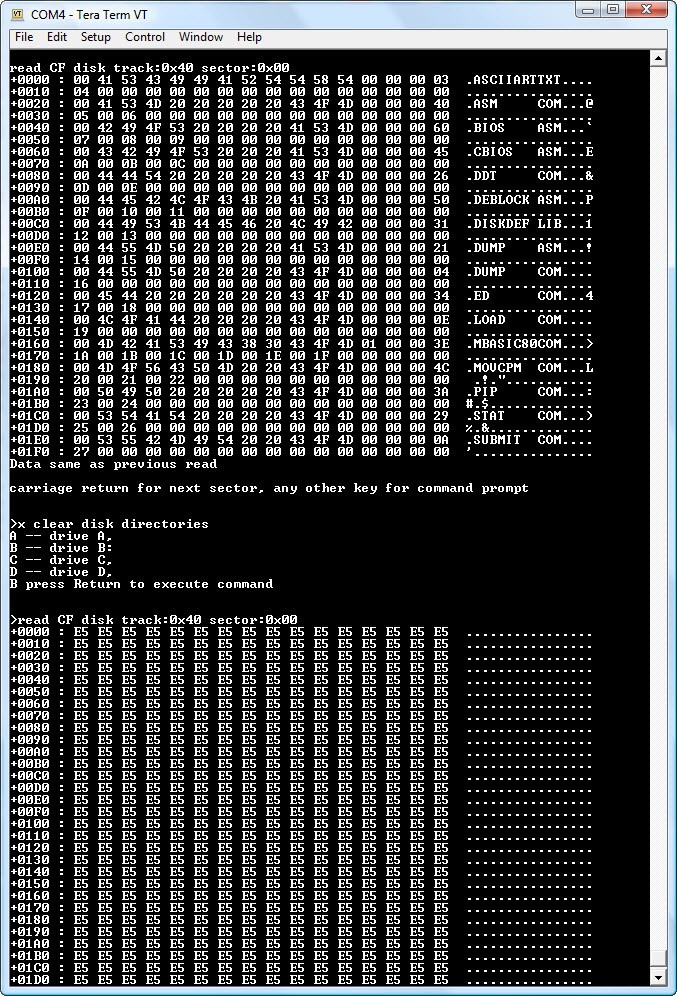

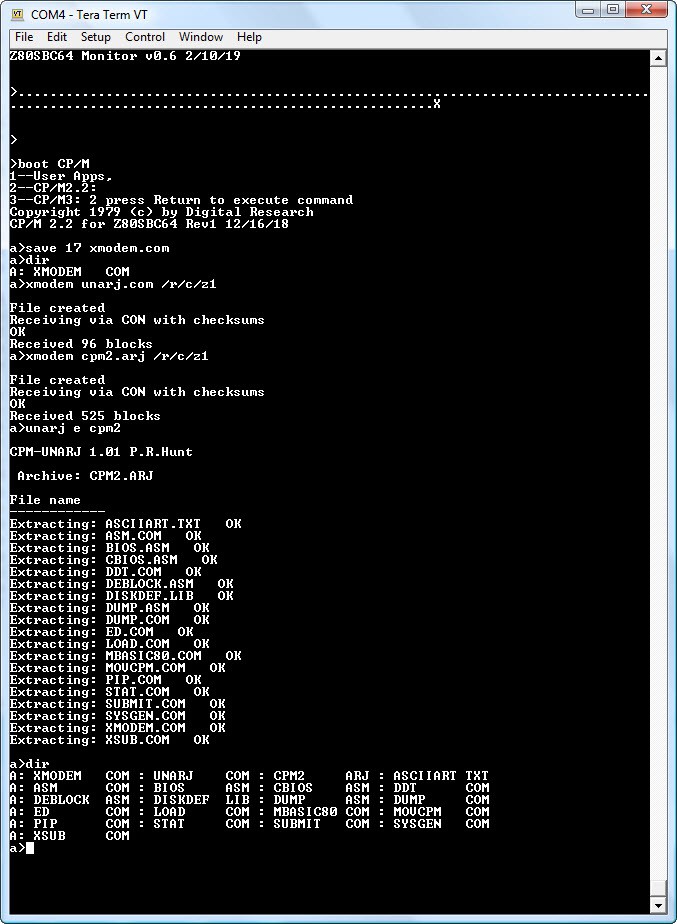

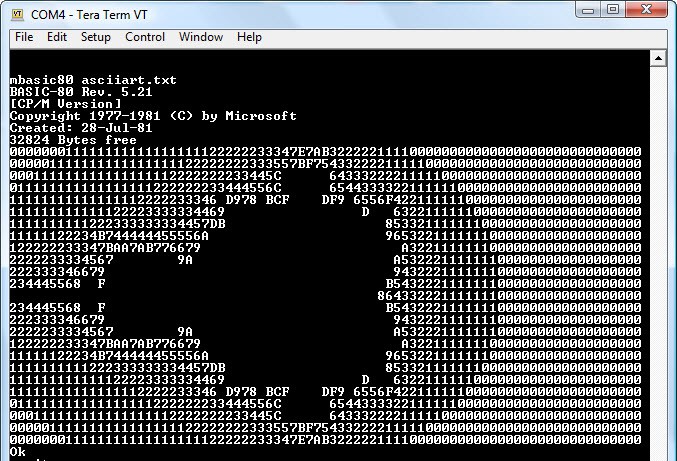

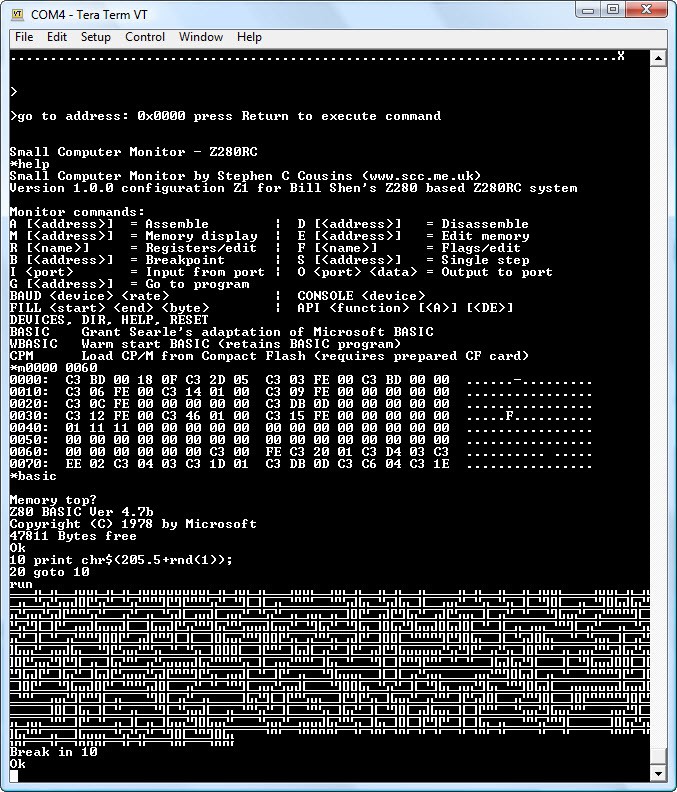

Stage 3, CP/M

Stage 4, RC2014 Ecosystem

- Adding RC2014 connector

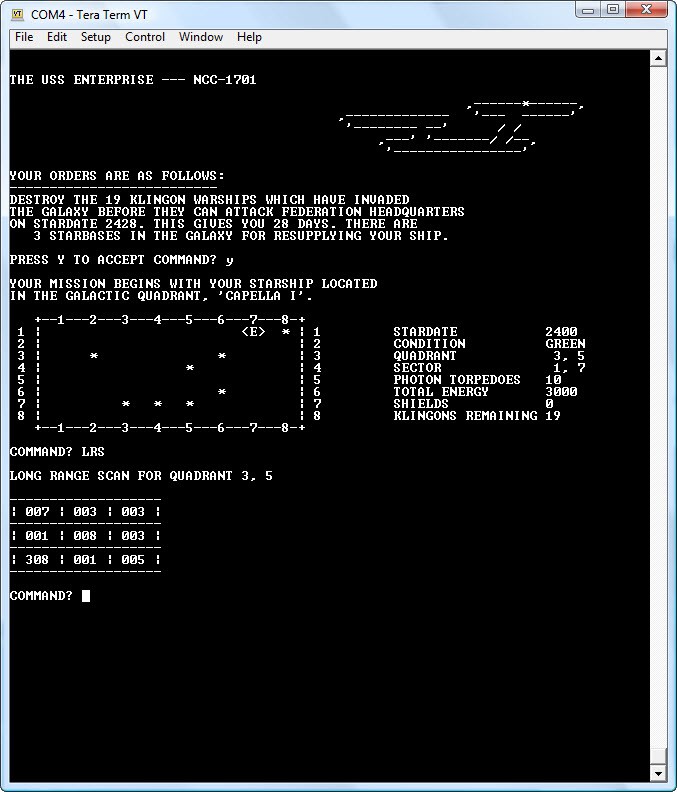

Video of Z80SBC64 running selected monitor commands and CP/M commands in real time

Plasmode

Plasmode

Hi Assif,

OK, I'm back.

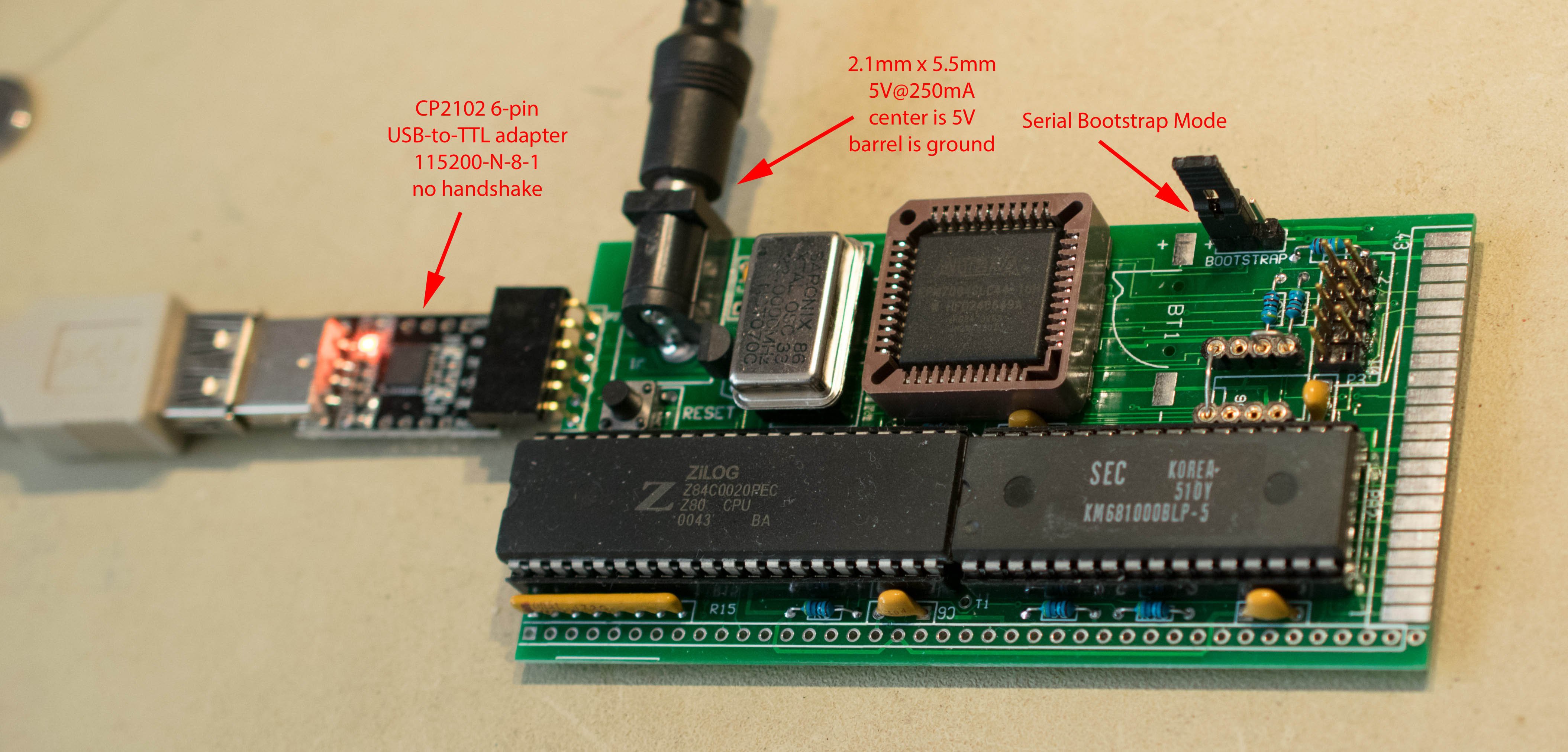

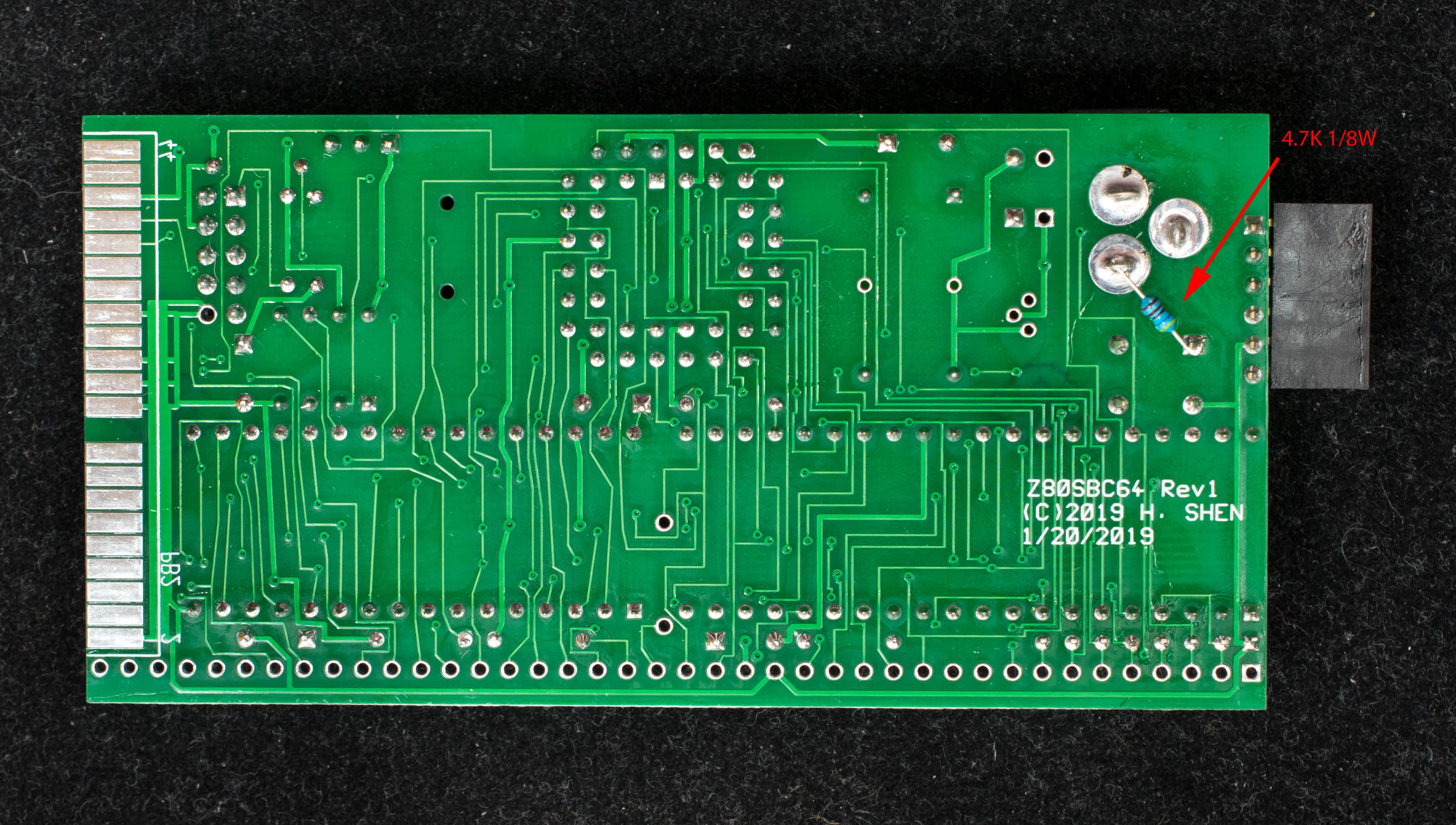

The Z80 RESET low is not a good sign. It should be low when you press the reset button, but goes high when released. Since you don't have the voltage supervisor installed, you should've install a 4.7K pull up as shown in this photo: https://cdn.hackaday.io/images/2713781549836203800.jpg

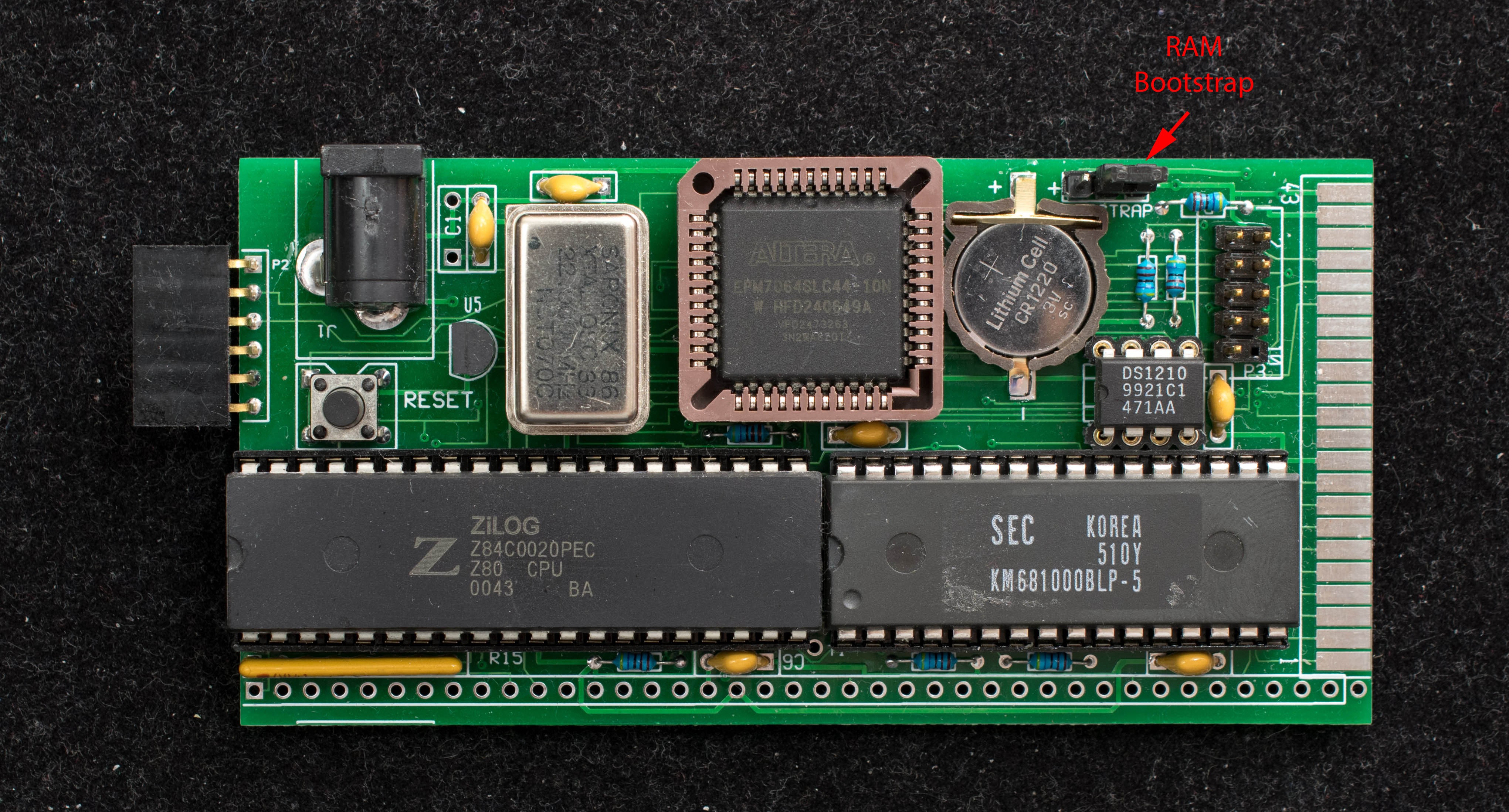

Since you have a scope, the signal you may want to monitor is Z80 pin 25, BUSRQ. At power up, CPLD will hold BUSRQ low. As soon as it has received 256 bytes of serial data, it will release BUSRQ so Z80 can start execution.

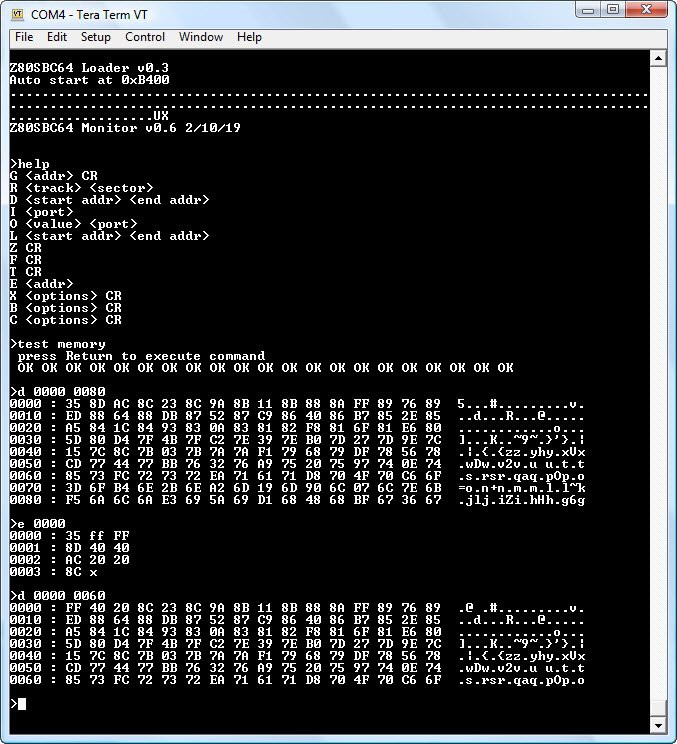

The small file 'Z80SBCLD_r03.bin' is a binary file, so be sure to send it as binary. In TeraTerm Send file menu there is a 'Binary Option' box that need to be checked. You should see the message: Z80SBC64 Loader v0.3

Auto start at 0xB400