-

New case design and setting a schedule

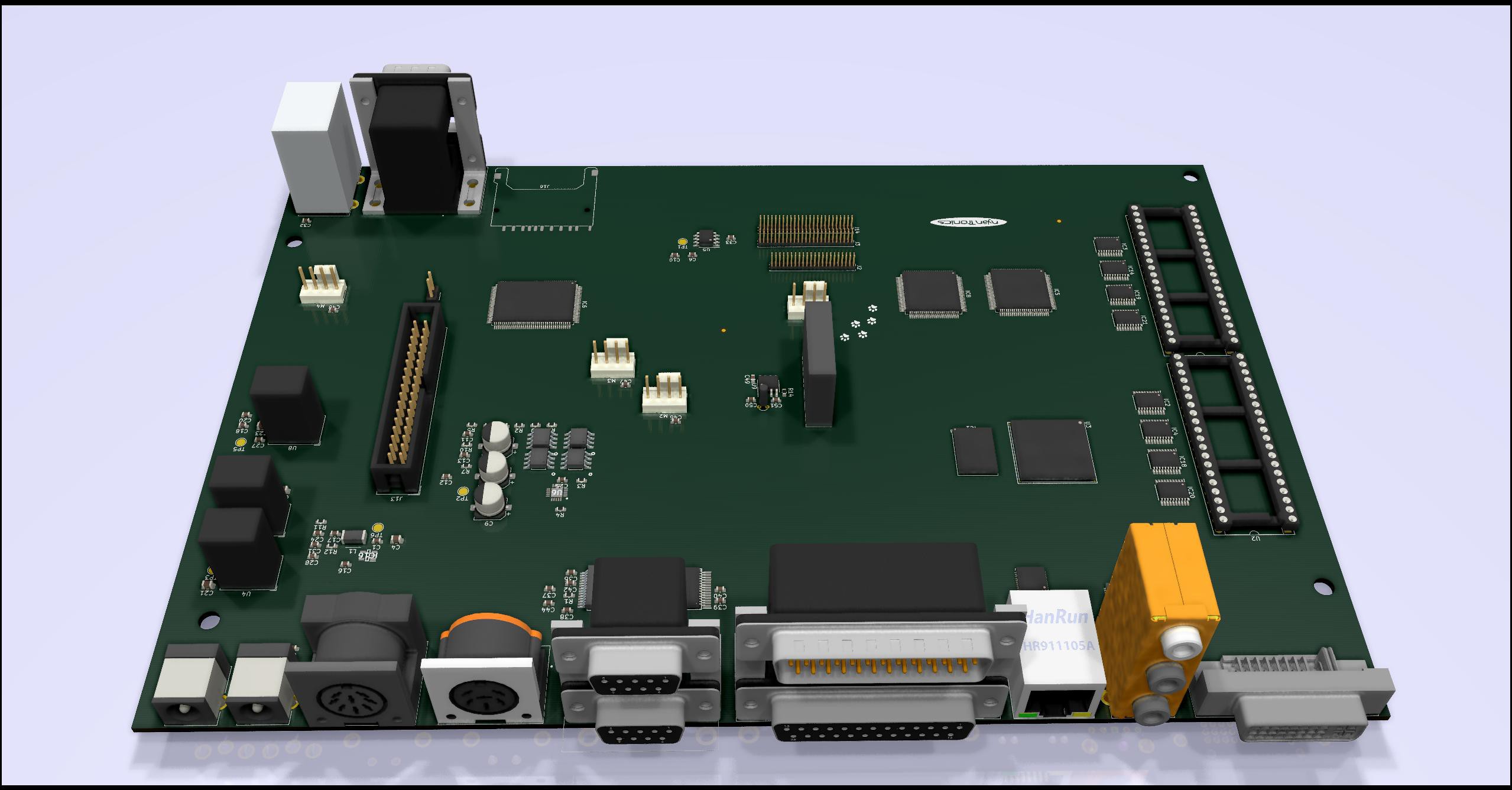

08/28/2019 at 19:18 • 0 commentsWith the PCB I/O layout close to being finalised, a mock-up of the case for the system was created that should give some idea of what the final product should look like:

![]()

![]()

Rough dimensions for the case are: 340x190x120 mm (WxDxH). The final look will likely differ from these preliminary renders, but it should give some idea of what to expect there. The 'Legend of Nyan' MSX cartridge is not included with the final product (unless sponsored to become a real game, of course).

Alice update

Sharp eyes may have noticed that the specifications for "Alice" have been changed slightly. The internal communication bus has been firmly set to be AXI4 (AMBA 4), with the internal CPU core being the Plasma, MIPS I-compatible core which is currently being ported to ECP5 FPGAs. While some may lament the loss of RISC-V as a feature, this change should provide the fast prototyping and stable development toolchain that the project can use to get it finished.

Remaining schedule

Barring any major setbacks, next month should see the integration of the individual parts of Alice, followed by the integration of the Super-IO chip and other components external to the FPGA. This will initially be done on breakout boards to ease development.

Following this, the schematic for the PCB will be finalized for prototyping. This should happen later this year, with possibly final integration and assembly testing following before the end of the year. That should conclude the PCB development and with it most of the FPGA core development.

Finally, next year should see the development of the final case design, the integration of the PCB and the progress towards towards actually getting the whole package produced, the progress of which will most likely depend on the demand and the resulting budget.

-

Progress Report #1: Optimism

08/18/2019 at 11:37 • 0 commentsAs they say, the best way to do a project is to head into it with overflowing amounts of enthusiasm and a vague inkling of how all the bits and pieces will actually fit together. Or maybe that was actually about how not to start a project. Regardless, after many hours of bashing away at the Tomodachi X2 project, something resembling an actual product is beginning to emerge, like a beautifully refined sculpture being carved from a shapeless piece of rock.

At the onset of the project it wasn't quite clear which compatibility modes would be added. This has now been solidified into the Commodore 128 and MSX2+. The former also gets one Commodore 64 and CP/M mode. The latter gets one the whole range of MSX systems, barring the MSX TurboR, which uses a different processor altogether.

Biggest progress on the physical system has been the work on the schematic and PCB layout, which has led to the current 250x170 mm board and its connectors:

![]()

This connector layout has been selected to merge both the connectors for the RISC-V system and the Super-IO chip, as well as those of the Commodore 128 and MSX2+. The latter will have to use the C128's tape drive and the Super-IO's printer port via a bridge in the chipset to make them compatible. This means that physical MSX tape drives and printers are not directly supported, but would require external hardware to convert the signalling to the appropriate format for those devices.

These decisions were mostly made to support the most commonly available hardware, and to limit the number of physical connectors on the board. Even at its current size it's already a fairly expensive board to have produced.

Alice chipset

The Alice chipset now features at its core a RISC-V processor, which forms part of the native TX2 mode. It coordinates the configuration of the system, and allows the other modes to be enabled. This part of the system is currently being prototyped on an FPGA development board, with the external processors, Super-IO chip and further hardware being added as needed on breakout boards. This approach should hopefully speed up development.

Custom enclosure

With abandoning the mini-ITX form factor and going for a custom form factor, this meant that while existing cases could not be used any more, we could however design a case that is specific for the TX2 system. This offers quite a lot of possibilities.

Later this month we hope to get some preliminary renders of this case online, to give an impression of what one might expect.

-

Let the development commence

06/25/2019 at 16:03 • 0 commentsOver the past weeks/months/too much time, I have been primarily occupying myself with the details of the "Alice" chipset, as this is the magic sauce that will make Tomodachi X2 either awesome or not so cool. Details such as how to switch between system modes, how to make everything flexible enough that one isn't limited to just a handful of options, and maybe most importantly of all, what 'native Tomodachi mode' is all about.

While brainstorming about this both by myself and with some friends, it quickly became obvious that while one could totally use one or more of the hardware CPUs on the board for native mode, it would be easier and much more powerful to use a more modern architecture. That's when picking a RISC-V core came into the picture.

These cores are nice and small, with some taking up only a few thousand LEs on an FPGA like the ECP5. Meanwhile they are efficient (depending on the core in question, of course) and very flexible due to the RISC-V architecture. This led to us poking at a number of cores, including f32c, Rocket and a funky one called Potato. Depending on which of these are the least painful to use, and with a strong preference for VHDL will ultimately decide which one will be featured on the first functional TX2 prototype.

Best thing of course is that since they all use the RISC-V ISA, switching cores later on is totally cool, as the software will still run.

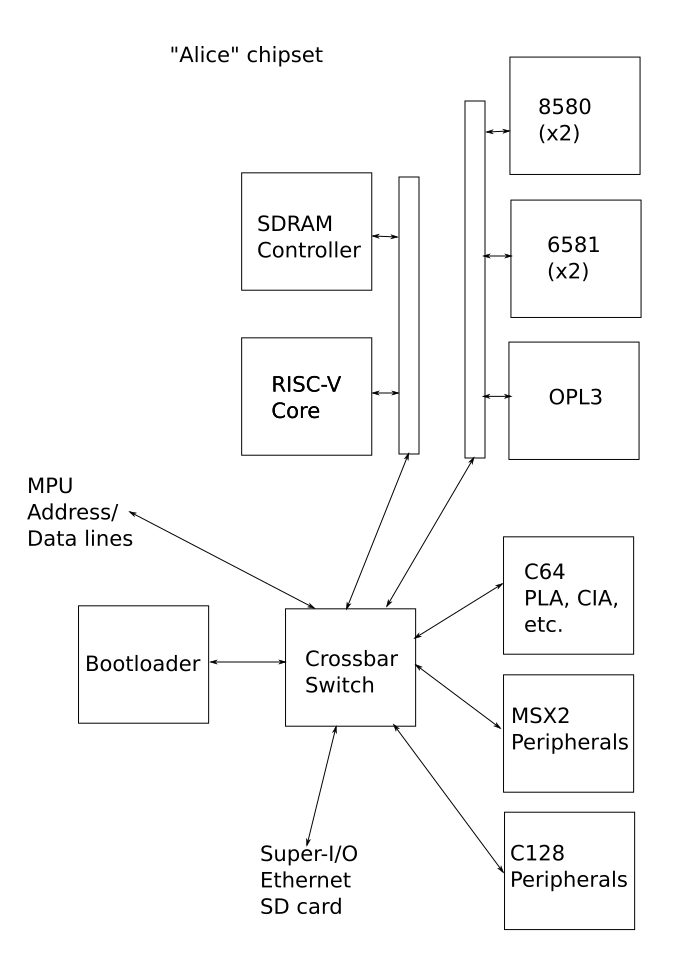

As for the architecture of the chipset itself, it'll likely end up looking somewhat like this:

![]()

Using a crossbar switch fabric to tie relevant elements together, and likely splitting mode-specific peripherals (such as the C64 PLA, ROMs and CIA chips) into their own modules should provide maximum flexibility. Meanwhile the SDRAM controller (DDR3 or otherwise) would be designed to accommodate different modes, such as 16- or 24-bit addressing, even allowing each MPU to have its own dedicated block of RAM, up to 64 kB or 16 MB.

As far as mode selection goes, one might be reminded of the C128, where one had to remember in which mode one was, followed by performing the required ritual steps to boot into the other mode: C128 manual.

Here a thought is to either boot into native mode, and execute a command there that will perform the switch, or have physical switches (hooked up to the bootloader in the FPGA) that can set the desired mode before one powers up the system. Perhaps a tad Altair 8800-ish, but could be useful if one intends to use the system in a specific mode for an extended period of time.

-

Settling on a first prototype design

05/10/2019 at 09:27 • 0 commentsThe Tomodachi project isn't a new one. It's something which I have toyed with in some form or another probably since the 1990s. What is new is that for the first time I have decided to put my love for those old home computers and modern technology together to make a system that is practical to make (now and during the coming years/decades). It should also cover all of the points that made systems back then so much fun to use, while not shying away from new technologies that enhance the experience instead of taking away from it.

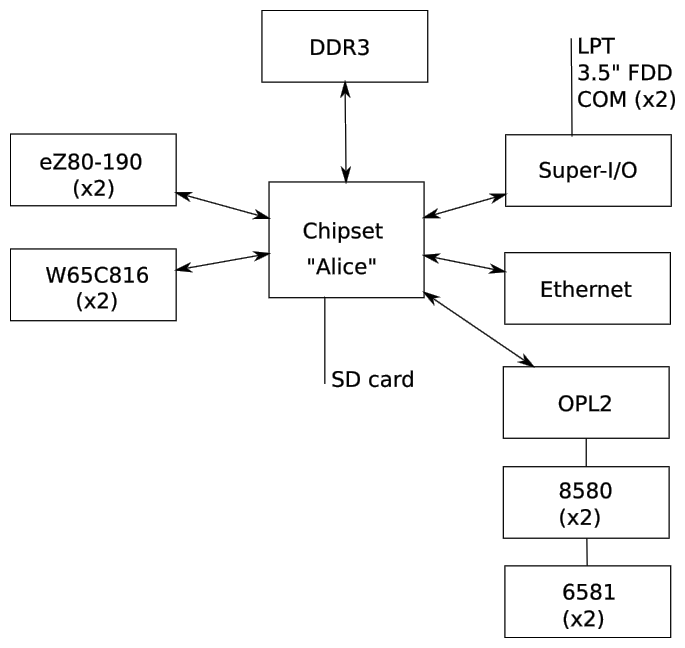

After months of brainstorming, the design that I came up with is basically the following:

![]()

I have had people comment on this diagram with 'it's basically a Commodore 128!', which I think is fair enough. It has the same 6502 compatibility (in the form of the 65C816) and CP/M-via-Z80 compatibility as the C128, though it ups the game by having the 16-bit successor to the 6502, as well as the modern, pipelined version of the Z80.

Also, it has two of each MPU, with the chipset providing access to the full range of DRAM, meaning 16 MB of RAM per 65C816 and eZ80-190 and DMA possible between these RAM segments as well as peripherals. Because there should be peripherals. From a floppy drive (obviously), to Ethernet (100 Mbit at least), to a range of synthesizer chips (Yamaha OPL2, stereo SIDs), as well as LPT (parallel) and COM (serial) ports.

Video isn't drawn explicitly into this diagram, but will be integrated into the chipset, with both VIC-II compatibility as well as its own, 1080p (or better) capable video adapter, outputting video likely via DVI-I (digital & analog output) and DisplayPort.

At this stage a Mini-ITX compatible board layout is being targeted, with the schematic and board layout gradually being finished for the first prototype board. All of this is done in KiCad, naturally. For the chipset an FPGA will be used, with the Lattice ECP5 (without SERDES) being a likely target. Much like the PLA in the C64, it's this chipset that will be the 'magic sauce' that makes the whole system work.

After initial prototyping, fun details such as which shell to use will pop up. Clearly, the system should boot from ROM like the C128 and C64 for that 'instant on' experience. Whether one would use a BASIC shell of some type, boot into a DOS, or use a Forth shell (why not?) is all still up in the air.

My hope is that others will feel interested enough in this project to pitch in, even if it is just with some ideas and sketches on the back of envelopes, scanned in and faxed to me. It's going to be fun, I'm sure :)

Maya Posch

Maya Posch