-

ALU Implemented

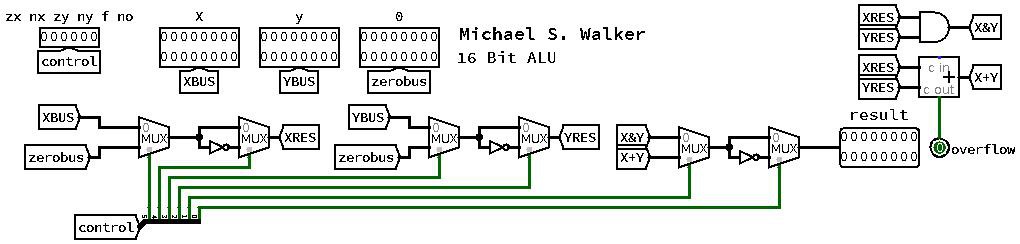

06/26/2019 at 06:10 • 0 comments/** * The ALU (Arithmetic Logic Unit). * Computes one of the following functions: * x+y, x-y, y-x, 0, 1, -1, x, y, -x, -y, !x, !y, * x+1, y+1, x-1, y-1, x&y, x|y on two 16-bit inputs, * according to 6 input bits denoted zx,nx,zy,ny,f,no. * In addition, the ALU computes two 1-bit outputs: * if the ALU output == 0, zr is set to 1; otherwise zr is set to 0; * if the ALU output < 0, ng is set to 1; otherwise ng is set to 0. */ // Implementation: the ALU logic manipulates the x and y inputs // and operates on the resulting values, as follows: // if (zx == 1) set x = 0 // 16-bit constant // if (nx == 1) set x = !x // bitwise not // if (zy == 1) set y = 0 // 16-bit constant // if (ny == 1) set y = !y // bitwise not // if (f == 1) set out = x + y // integer 2's complement addition // if (f == 0) set out = x & y // bitwise and // if (no == 1) set out = !out // bitwise not // if (out == 0) set zr = 1 // if (out < 0) set ng = 1 CHIP ALU { IN x[16], y[16], // 16-bit inputs zx, // zero the x input? nx, // negate the x input? zy, // zero the y input? ny, // negate the y input? f, // compute out = x + y (if 1) or x & y (if 0) no; // negate the out output? OUT out[16], // 16-bit output zr, // 1 if (out == 0), 0 otherwise ng; // 1 if (out < 0), 0 otherwise PARTS: // zx And16(a=x, b=false, out=zxTrue); Mux16(a=x, b=zxTrue, sel=zx, out=zerox); // nx Not16(in=zerox, out=notx); Mux16(a=zerox, b=notx, sel=nx, out=negx); // zy And16(a=y, b=false, out=zyTrue); Mux16(a=y, b=zyTrue, sel=zy, out=zeroy); // ny Not16(in=zeroy, out=noty); Mux16(a=zeroy, b=noty, sel=ny, out=negy); // f And16(a=negx, b=negy, out=andfxy); Add16(a=negx, b=negy, out=addfxy); Mux16(a=andfxy, b=addfxy, sel=f, out=fxy); // no Not16(in=fxy, out=notfxy); Mux16(a=fxy, b=notfxy, sel=no, out=out); }![]()

-

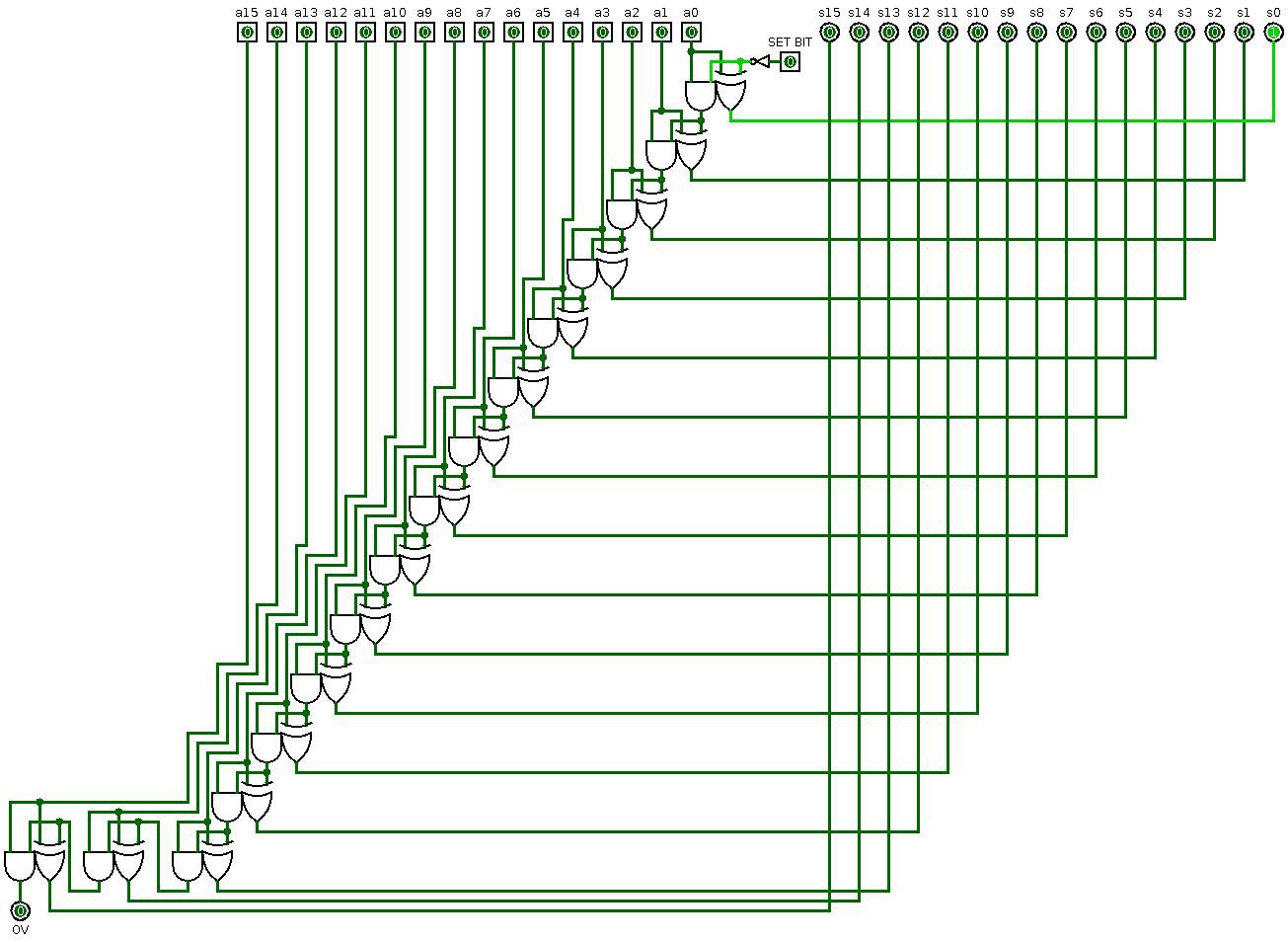

16 Bit +1 Increment implementation. + HDL

06/26/2019 at 00:13 • 0 comments![]()

/** * 16-bit incrementer: * out = in + 1 (arithmetic addition) */ CHIP Inc16 { IN in[16]; OUT out[16]; PARTS: HalfAdder(a=in[0], b=true, sum=out[0], carry=c0); HalfAdder(a=in[1], b=c0, sum=out[1], carry=c1); HalfAdder(a=in[2], b=c1, sum=out[2], carry=c2); HalfAdder(a=in[3], b=c2, sum=out[3], carry=c3); HalfAdder(a=in[4], b=c3, sum=out[4], carry=c4); HalfAdder(a=in[5], b=c4, sum=out[5], carry=c5); HalfAdder(a=in[6], b=c5, sum=out[6], carry=c6); HalfAdder(a=in[7], b=c6, sum=out[7], carry=c7); HalfAdder(a=in[8], b=c7, sum=out[8], carry=c8); HalfAdder(a=in[9], b=c8, sum=out[9], carry=c9); HalfAdder(a=in[10], b=c9, sum=out[10], carry=c10); HalfAdder(a=in[11], b=c10, sum=out[11], carry=c11); HalfAdder(a=in[12], b=c11, sum=out[12], carry=c12); HalfAdder(a=in[13], b=c12, sum=out[13], carry=c13); HalfAdder(a=in[14], b=c13, sum=out[14], carry=c14); HalfAdder(a=in[15], b=c14, sum=out[15], carry=false); } -

HDL Completed for Boolean Logic.

06/25/2019 at 09:21 • 0 commentsFinished the HDL code for the logic, starting work on the ALU.

Computer build from first principals

Complete computer build from the logic to the compiler and operating system.

Michael Walker

Michael Walker