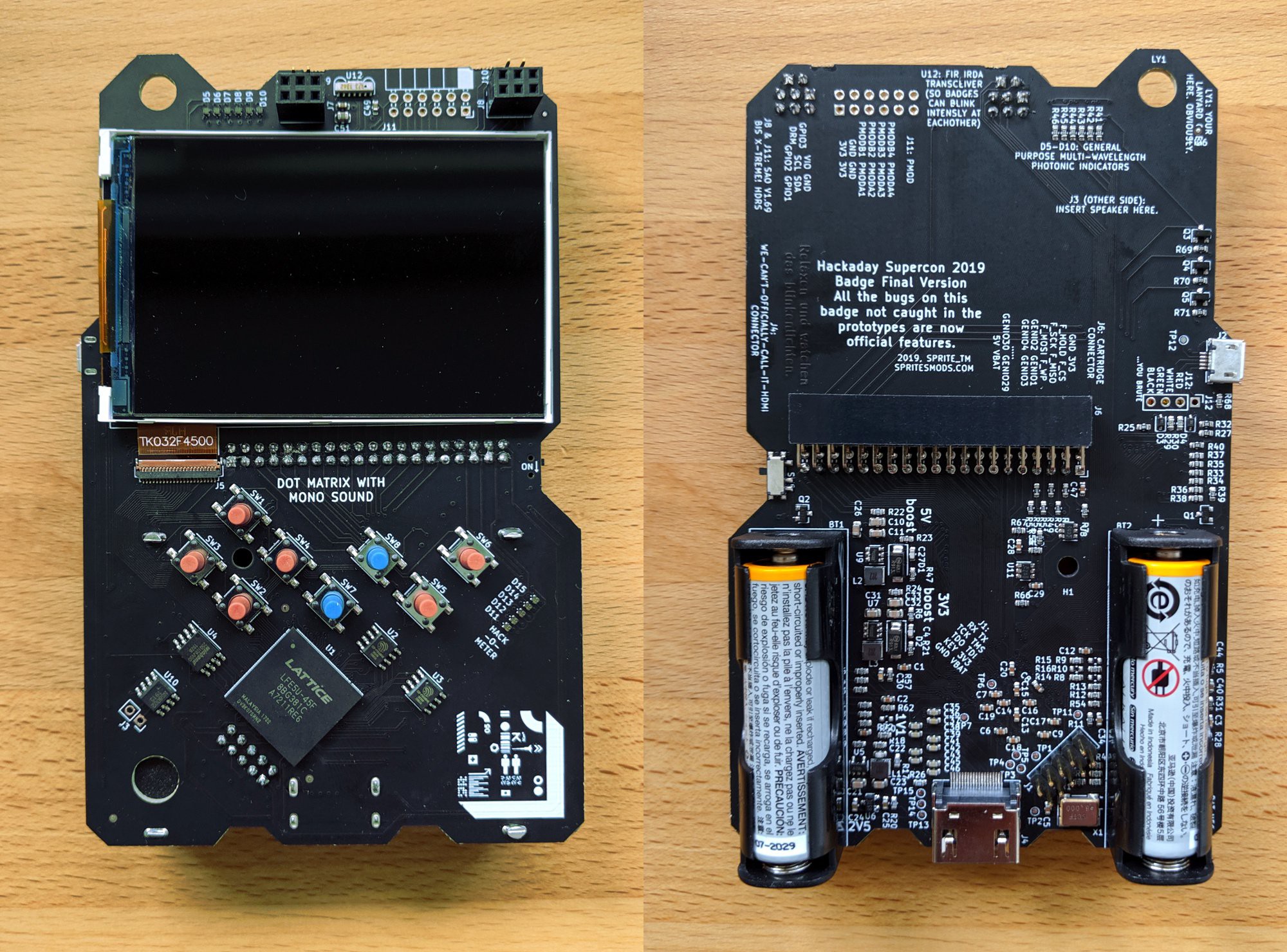

Jeroen Domburg (aka Sprite_TM) is the hardware and software designer for this badge. He began working on the concept in January of 2019 and the production run of over 500 badges was completed about three weeks prior to the Hackaday Superconference

The firmware and software efforts continue, with a large badge team jumping in to help test and stabilize the FPGA design, to build up workshops around the badge that teach FPGA concepts, and to write the games and apps that come with the stock firmware.

Please Install the Toolchain Before Arriving at Supercon!

You can be up and running very quickly once you get the hardware if you already have the toolchain installed. Sean Cross put together packages for Linux, Mac, and Windows that just need to be unpacked and added to the path of your OS. This includes the open source tools you need to synthesize bitstreams for the FPGA and to compile C code to run on the RISC-V core. See his repo for more information:

https://github.com/xobs/ecp5-toolchain

Main Code Repository:

https://github.com/Spritetm/hadbadge2019_fpgasoc/

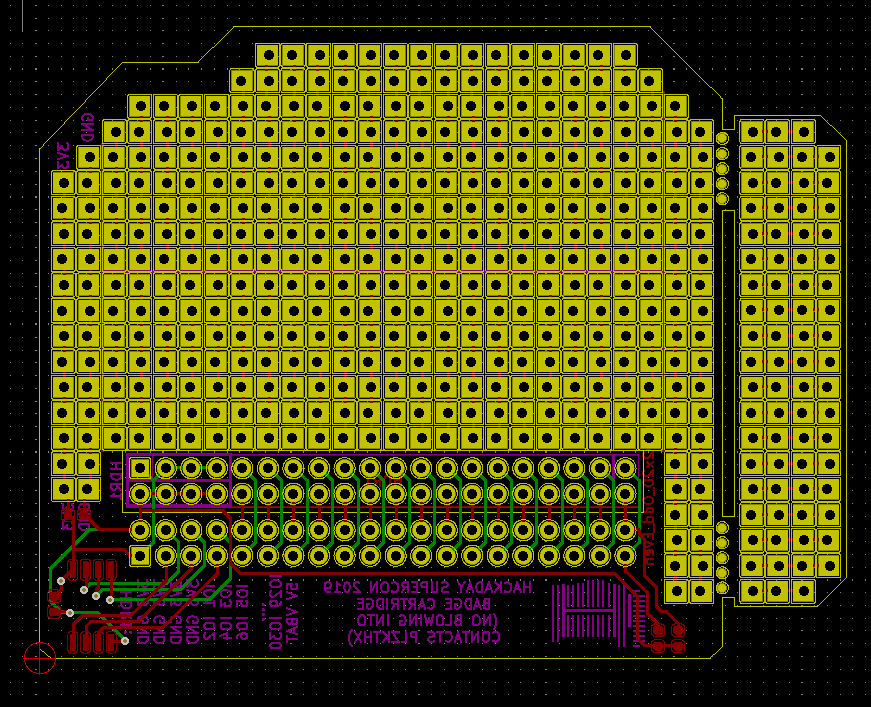

Hardware Repository:

https://github.com/Spritetm/hadbadge2019_pcb

Documentation is a Work In Progress.

While you don't need to program the FPGA directly, you might want to. If so:

http://bit.ly/fpga_badge_workshop

and not as complete, but still fun:

https://github.com/hexagon5un/hackaday_supercon_2019_logic_noise_FPGA_workshop

Lutetium

Lutetium

Voja Antonic

Voja Antonic

Zapp

Zapp

I noticed in your latest hardware files, many of your escape traces between vias necked down to .09mm (~3.5mil). I also read OSHPark built the boards for the con. OSHPark's 4 layer DRC has a restriction of 5/5 mil trace/width. Did you work out a deal with them for the advanced specs?