-

VHDL migration, SoC implemented, First program running on HW

08/05/2020 at 20:02 • 0 commentsVery good progress happened.

First of I've rewritten everything in VHDL, because the very first version of my processor was in VHDL and I feel much more confident with writing it than verilog.

As a second step I implemented a very basic BRAM module, tested most instructions (i just realized while typing this that I am still missing the shift instructions. Lazy me.) with a testbench and wired up the SoC.

Created a simple ROM too which is for the moment directly in the SoC module file and contains just 32 instructions max for the moment, BUT I got the very first program working looking like this:

load 0 into r0

load 1 into r1

load 16 into r2

load 0 into r3

load 5 into r5

add r0 = r0 + r1

set address (leds) 0x5 to r0

set lower than r3 = r1 < r2

branch when r3 != 0 --> 5 (to add instruction)

sub r0 = r0 - r1

set address (leds) 0x5 to r0

set lower than r3 = r0 < r1

branch when r3 = 0 --> 9 (sub instruction)

jump 0

This counts to 16 and back down to 0. And this works super nice! See embedded video:Pretty happy about this. I think I will implement a very very simple assembler first, a nice ROM module next and then will see where it goes on. The updated VHDL code can be found in my gitlab repository

-

Addition works.

07/29/2020 at 08:17 • 0 commentsI think I finished writing the CPU up. Missing are the ROM and RAM.

But I only tested load and addition commands yet. TODO: Test every instruction

See:

![]()

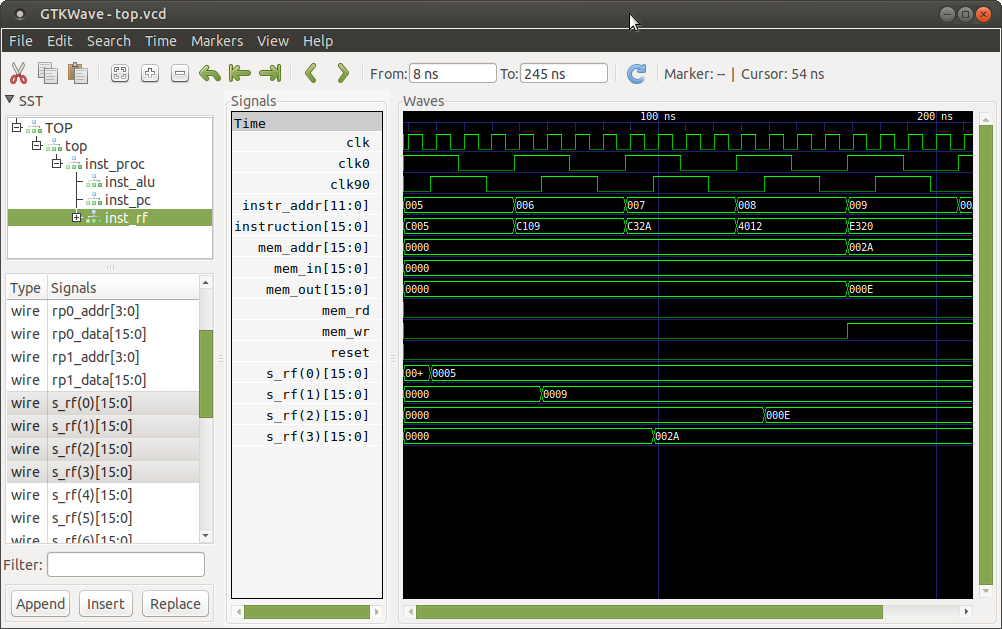

What can be seen here?

load 5 into register 0

load 9 into register 1

load 2a into register 3 (Output address)

Add reg 0 and 1, save into reg 2Display result (0x000e) at address (0x002a)

Looking good.

ICE-CPU MK II

Simple 16 bit soft-core CPU for FPGAs written in VHDL (previously verilog)

Mario

Mario