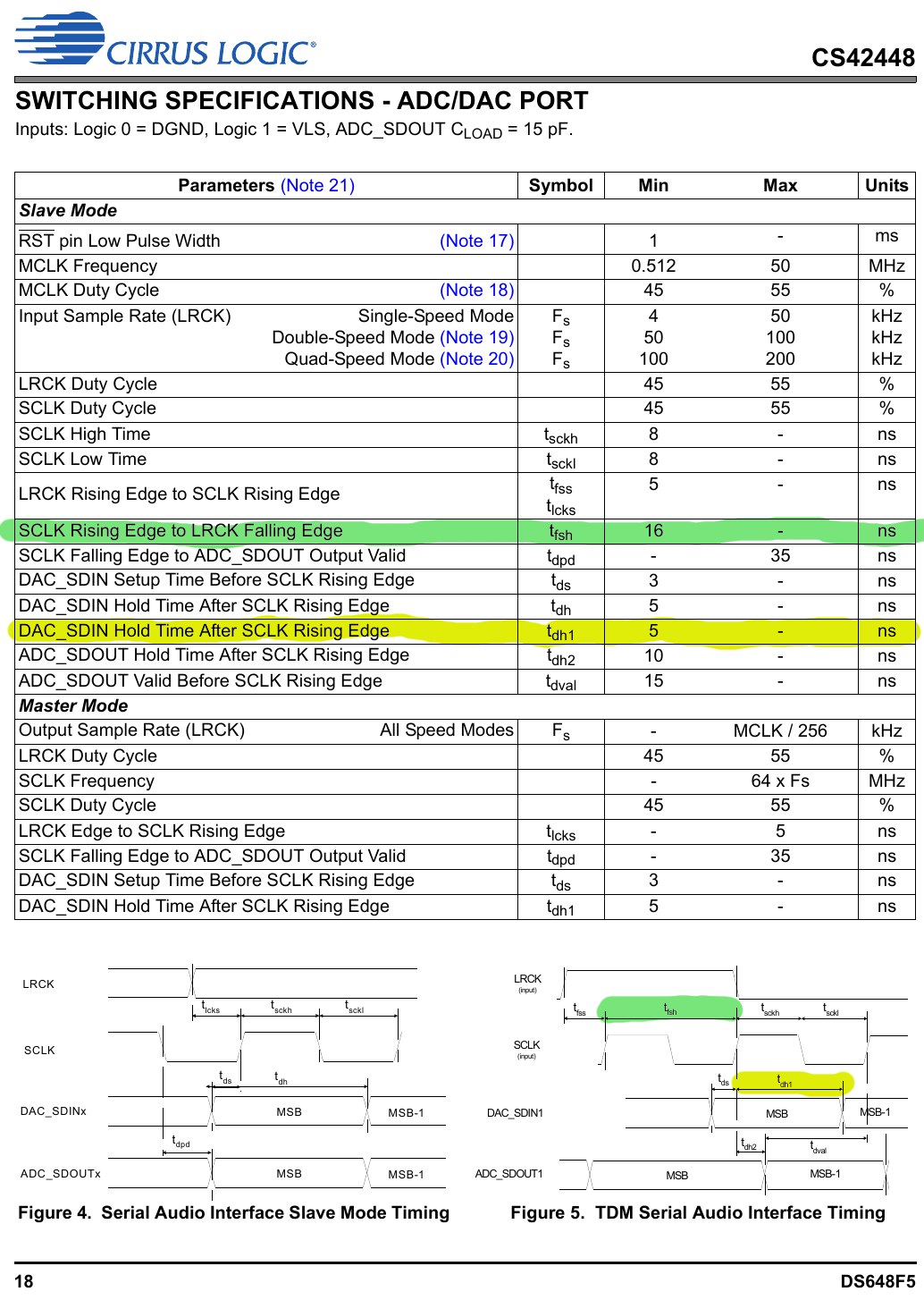

So what hold time are we supposed to have? I looked it up in the datasheets for the 2 TDM chips I've used so far...

Looks like CS42448 wants 5 ns hold time for data, but 16 ns hold time on the frame sync. Yikes! Looks like I'm going to need to delay the FS pulse to the next falling edge.

... minor rant: Whoever at Cirrus (maybe then Crystal?) drew this Figure 5 timing diagram really made it confusing by extending the Tdh time all the way to the next rising edge. I'm sure it was convenient (lazy?) and visually appealing not to have a gap between Tdh and Tsckh. But it visually implies LRCK (which I'm calling the frame sync pulse) needs to go longer, even though the spec says only 16ns. Even worse, visually it seems to suggest the end of LRCLK should go to the next rising edge of SCLK. Really wish whoever writes these datasheets would do better!

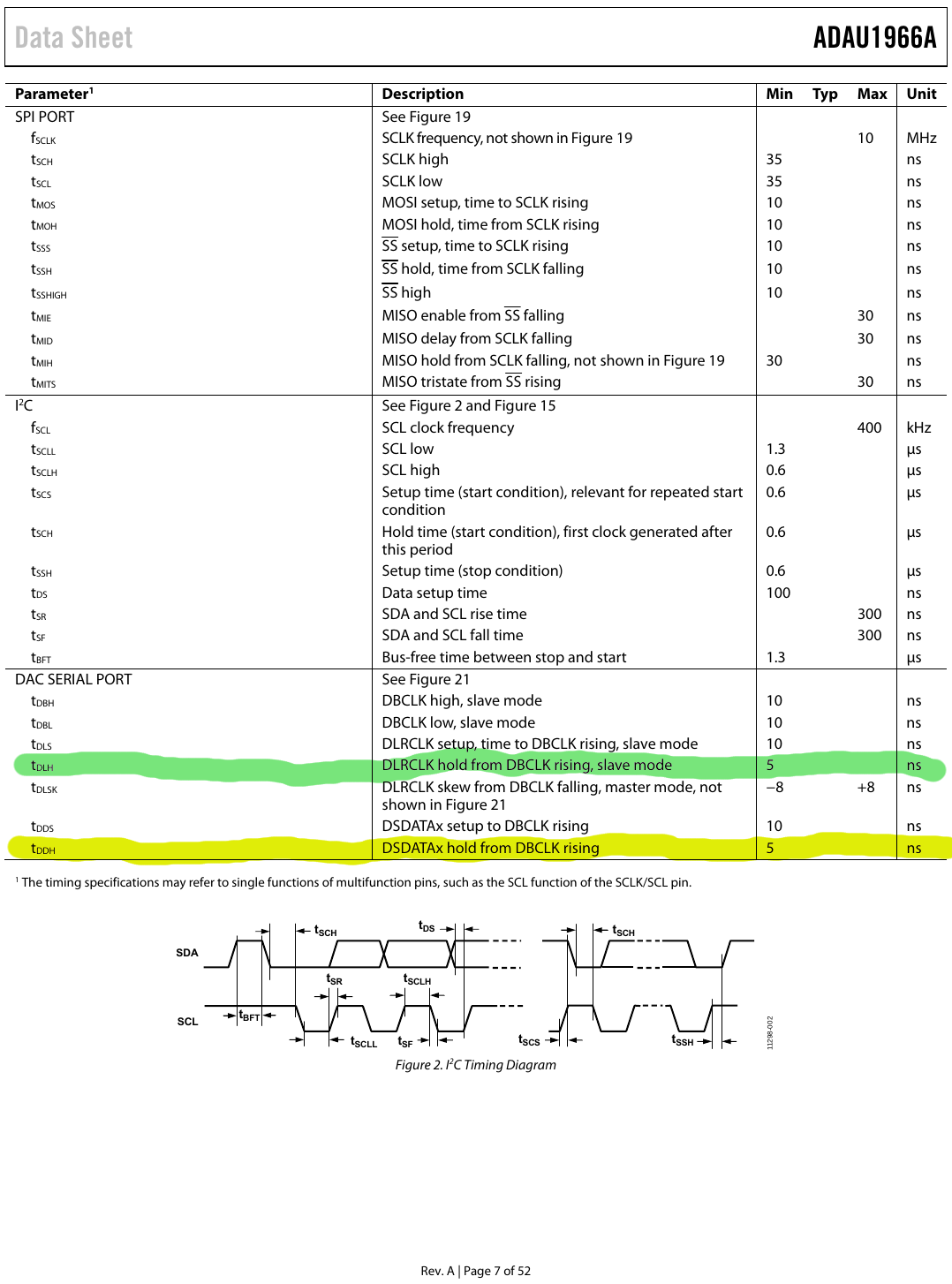

ADAU1966A seems to be a little easier, wanting 5 ns on both.

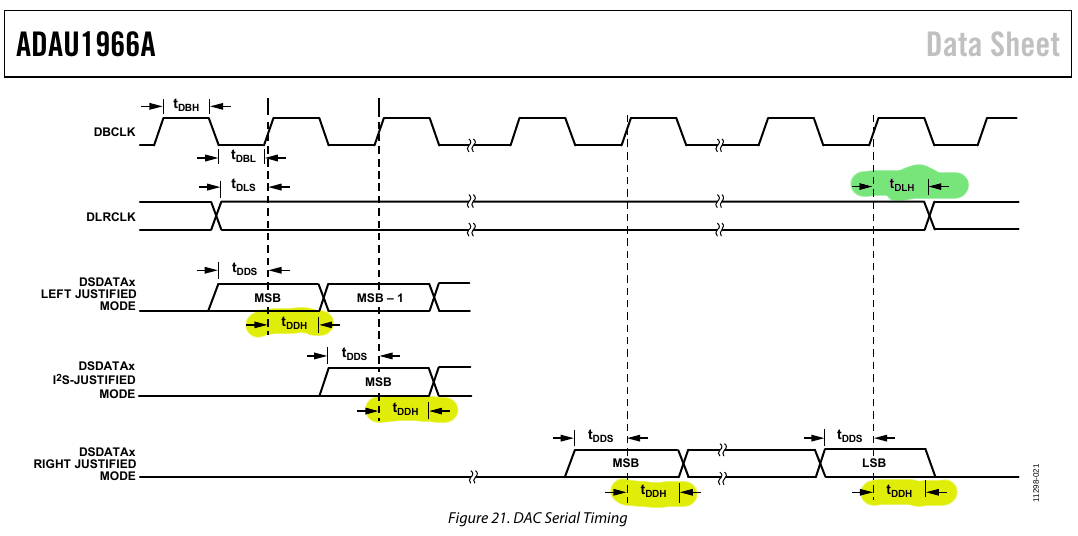

Analog Devices really shows how to compose a good timing diagram. The dotted lines from the clock edges to only the meaningful timing specs really helps communicate which things matter. Nice!

Analog Devices really shows how to compose a good timing diagram. The dotted lines from the clock edges to only the meaningful timing specs really helps communicate which things matter. Nice! Paul Stoffregen

Paul Stoffregen

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.