high level overview:

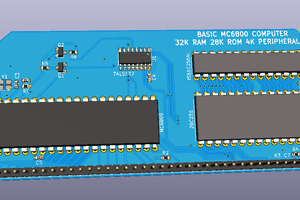

- main system board will be developed in a modular fashion

- modules will be developed in stages

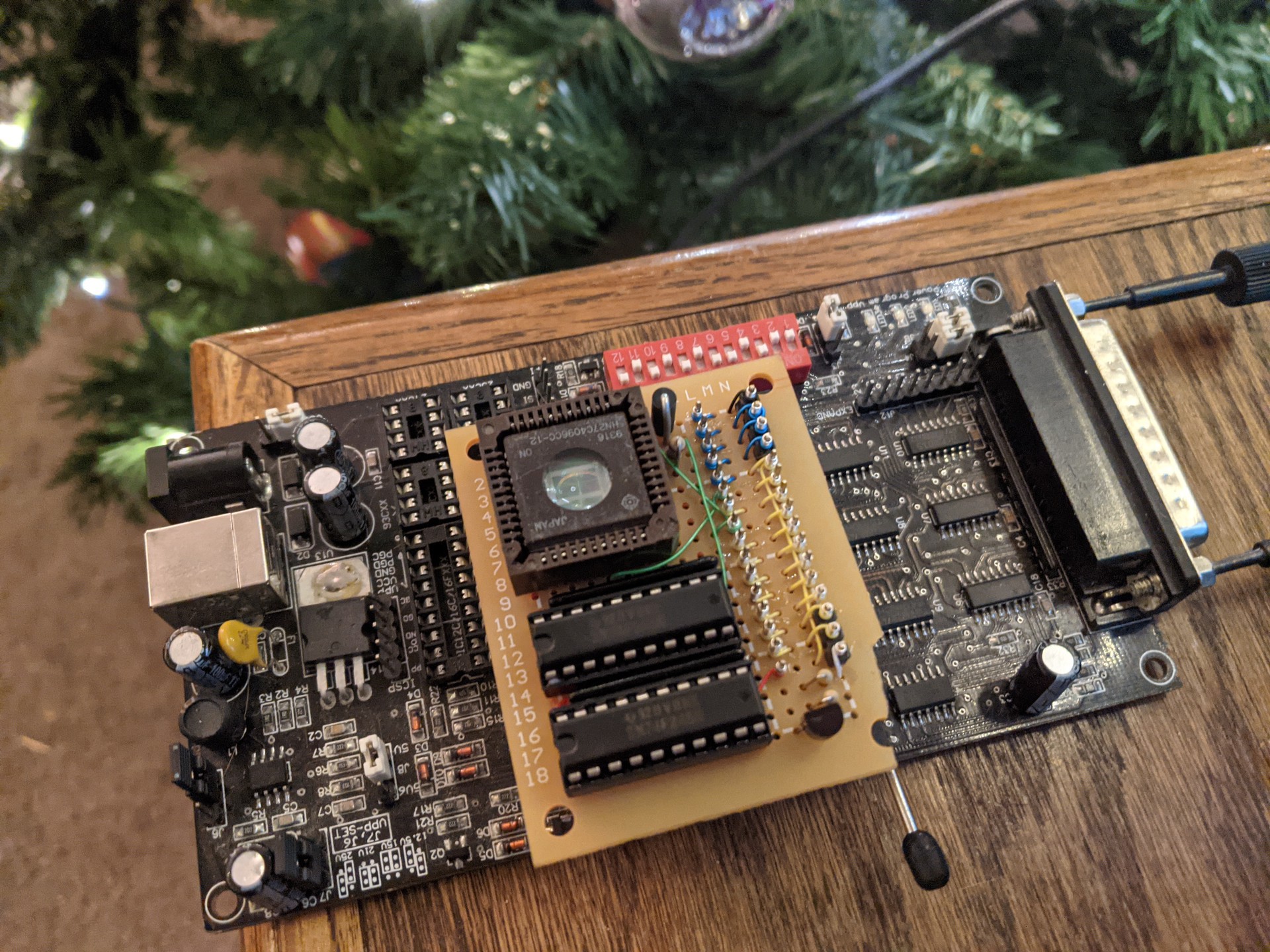

- first stage will be a wirewrapped prototype

- second stage will be a PCB with debugging headers for wirewrapping

- third stage will be implementation into an all-inclusive mainboard

- each module will serve a function (such as CPU initialization, bus arbitration, etc)

- each module will be documented so other hobbyists can replicate the effort

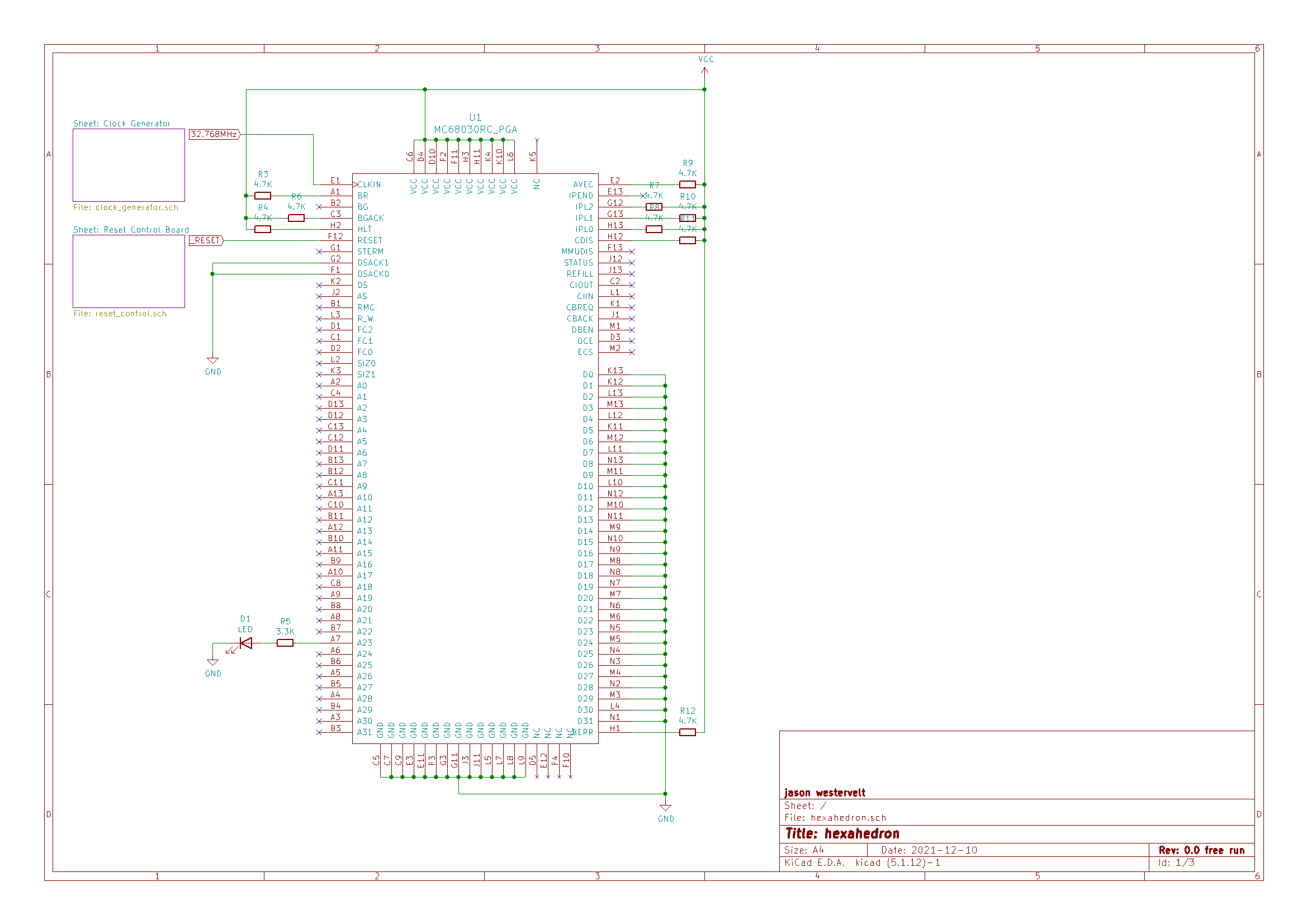

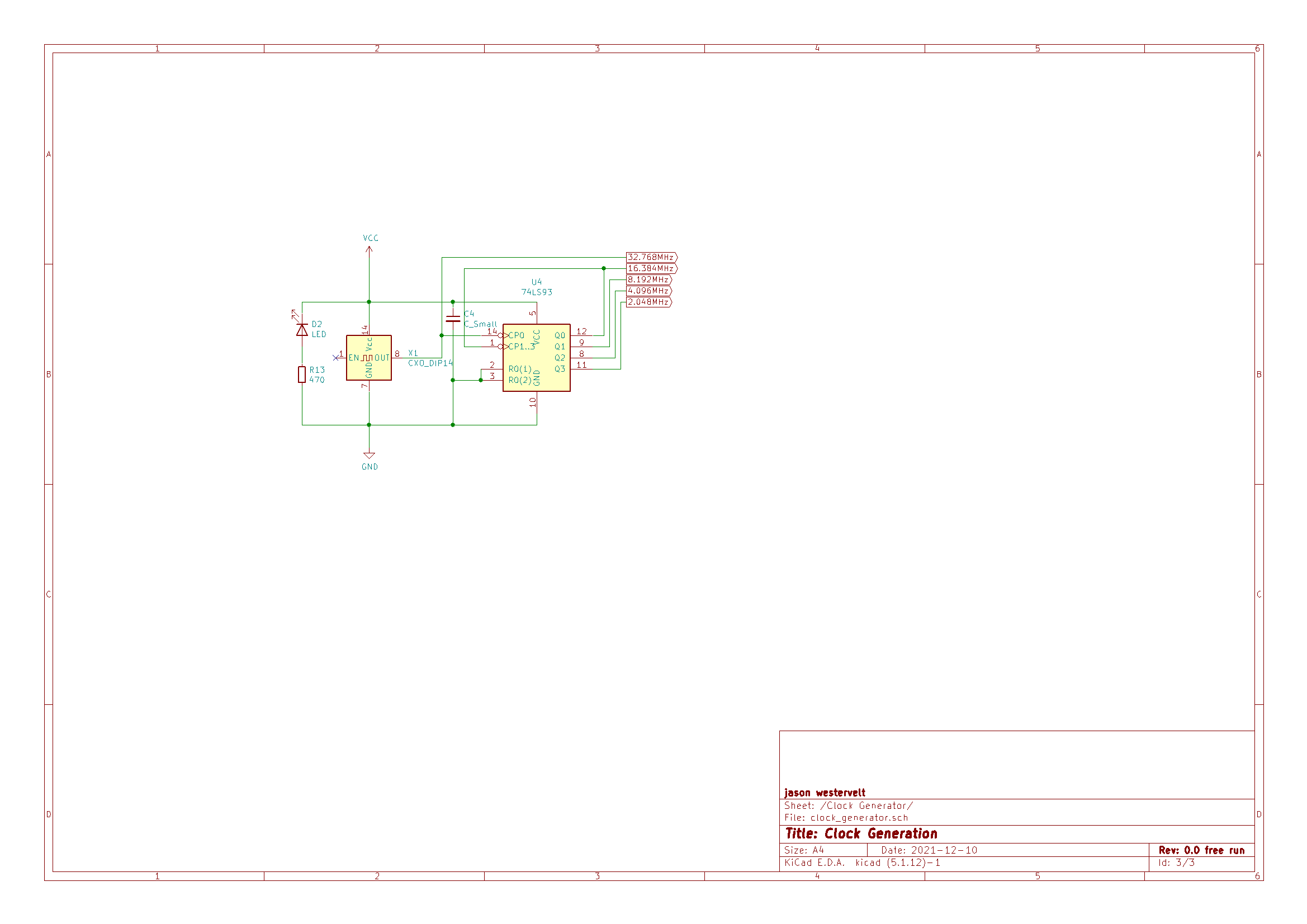

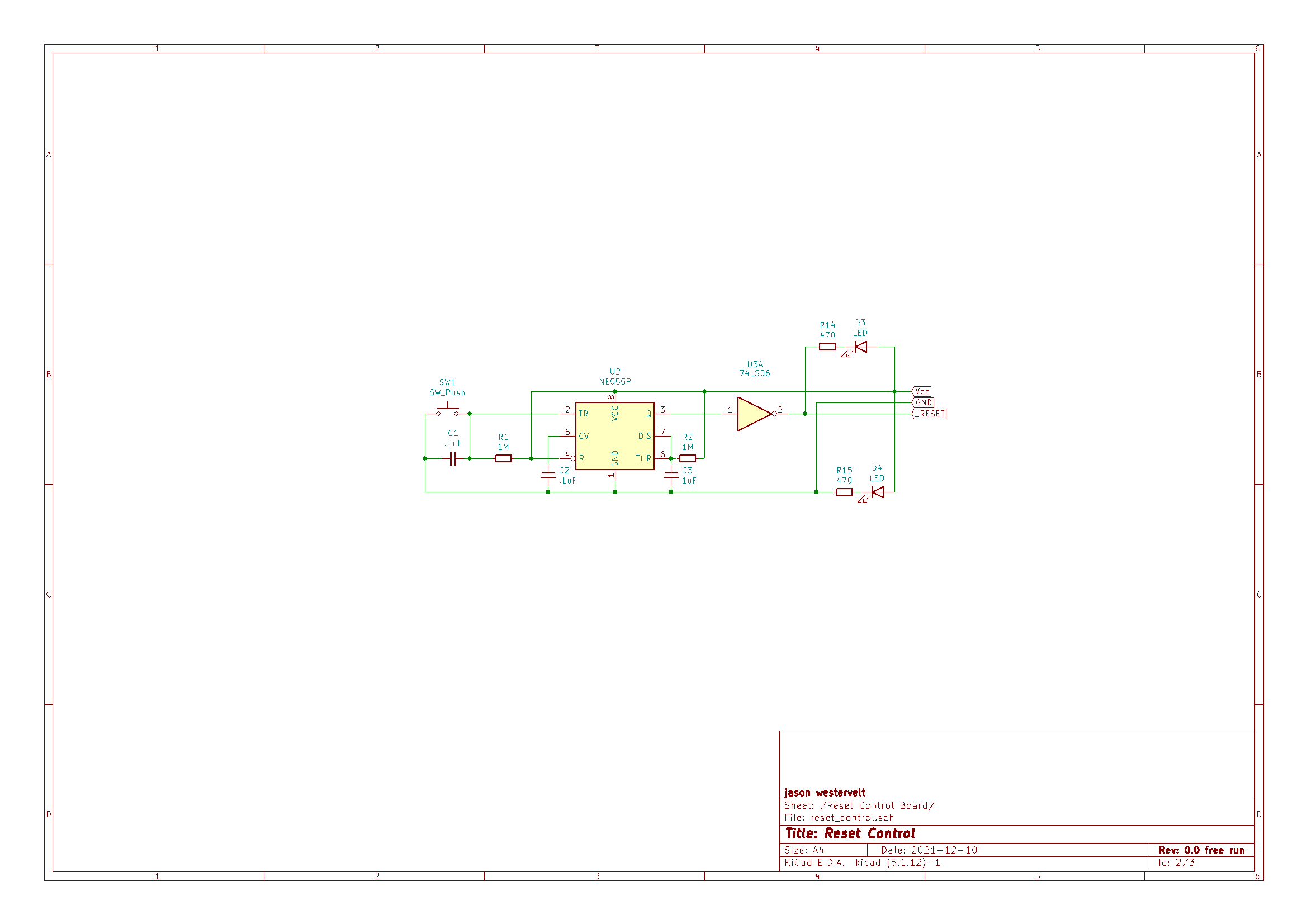

design decisions:

- controller board specs:

- VME bus card, 32bit

- MC68030 33MHz CPU

- MC68881 or MC68882 FPU (MC68881 currently on hand)

- MC68901 multifunction peripheral

- 32MB zero-wait state SRAM

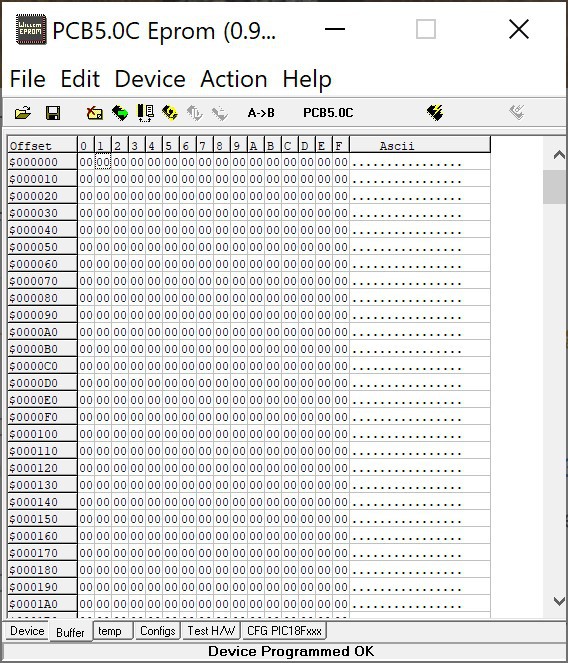

- 4MB ROM

- Both ROM and SRAM to utilize full 32bit data bus

- CPLDs for glue logic

- Utilize user-defined pins on the VME P2 connector for extra functionality

- ICSP

- CAN

- SPI / I2C

- PS/2 keyboard interface (probably using the N8042AH i have laying around)

in addition to the main controller board, i plan on building several peripheral boards:

- DRAM

- SCSI

- Sound (I have 4 MOS 6581 "Sid" chips laying around, could build a stereo synth card)

- Video (likely with an FPGA)

- Floppy disk controller

Arrow Westervelt

Arrow Westervelt

Gee Bartlett

Gee Bartlett

Benchoff

Benchoff

Jac Goudsmit

Jac Goudsmit

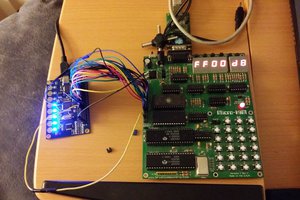

Very nice! I've started a 68030 project as well. The first step is indeed to have the D31-D0 at GND and see if the processor works.

I've been using MAX II chips for my FPGA as they also run on 5V.

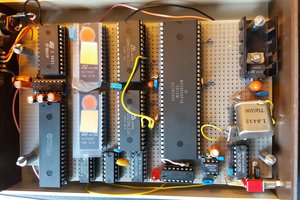

The current board has EEPROM, 4MB of SRAM and the 68901. And of course a 68882.

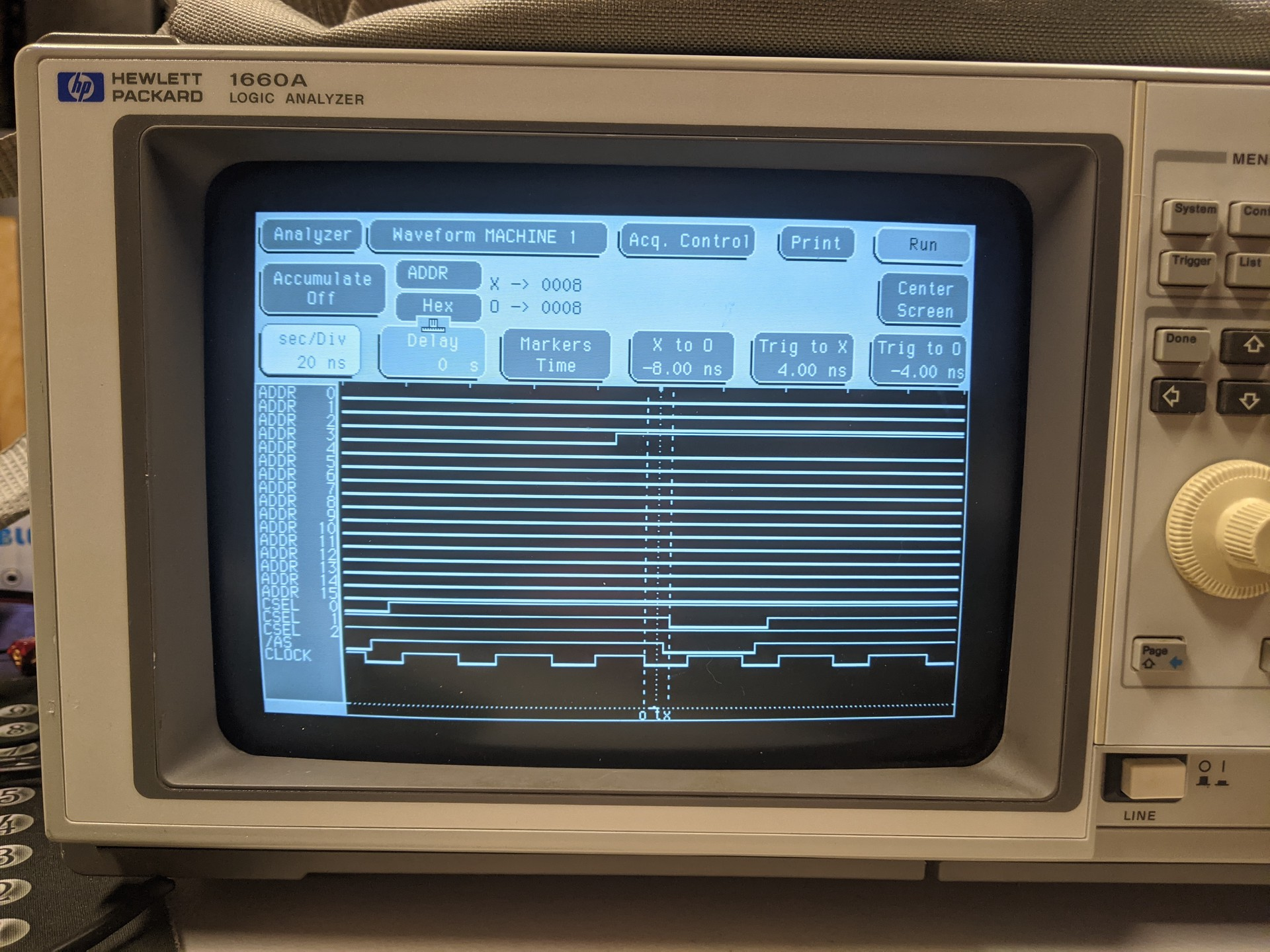

I've been using a TLA715 Logic Analyzer with a own made TMS203 processor probe to do all the hardware debugging. The TLA allows me with the TMS203 to see all the bus cycles including the instructions.