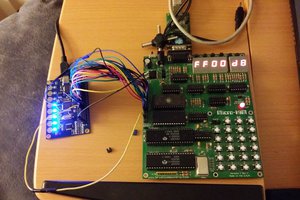

Target system features:

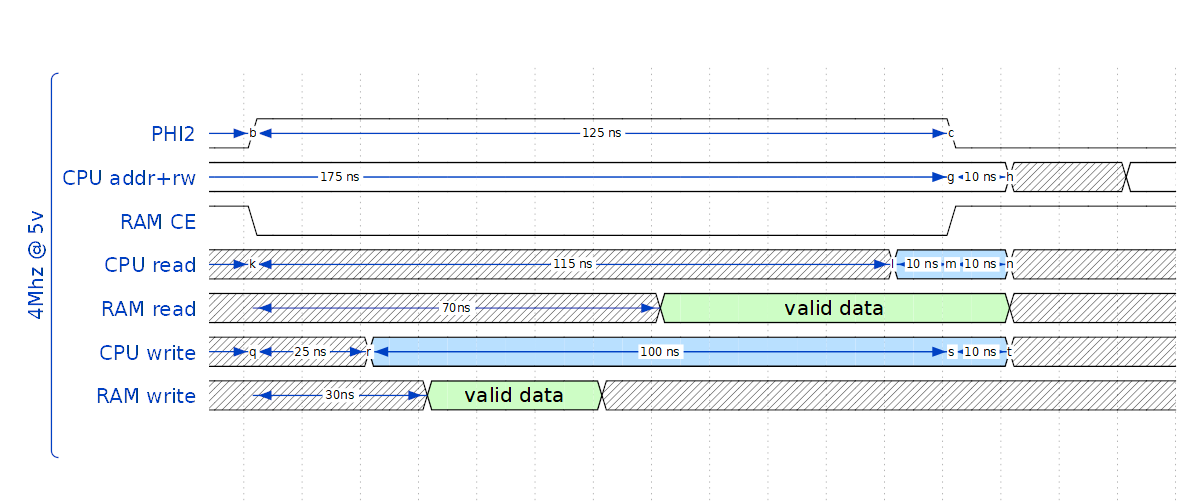

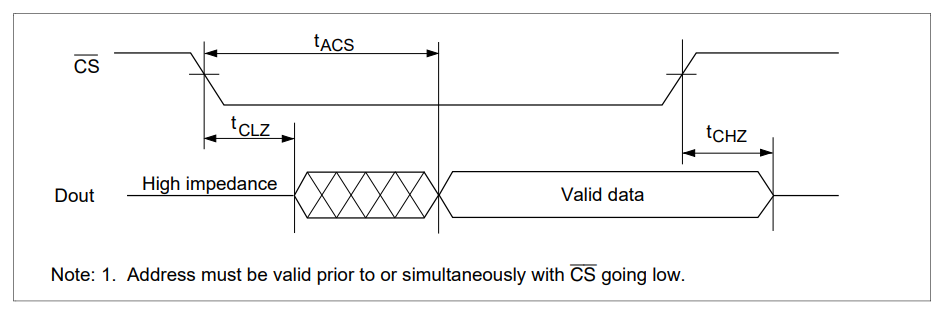

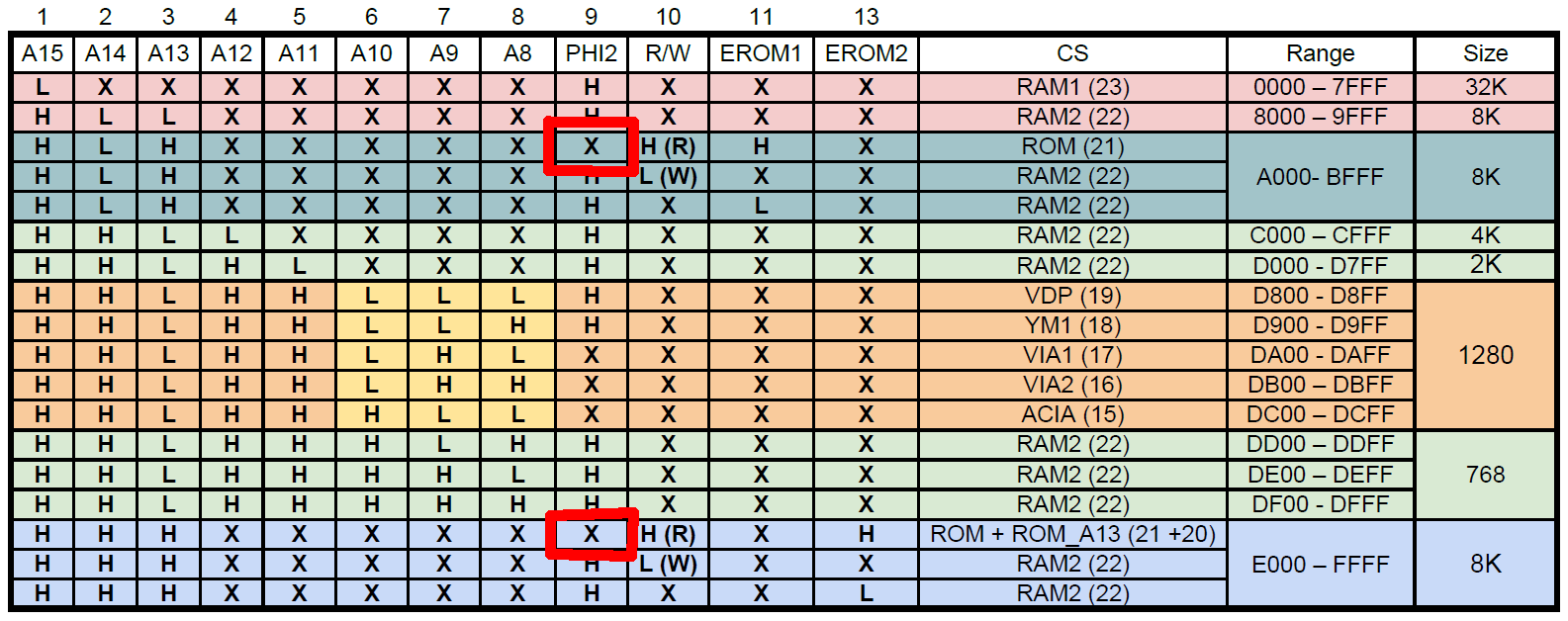

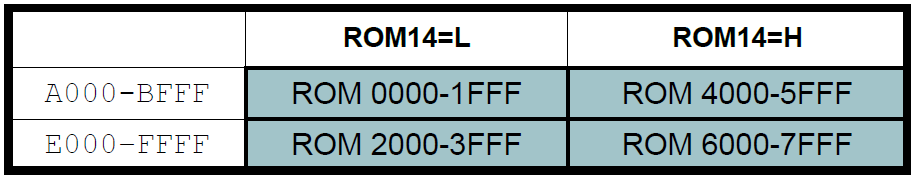

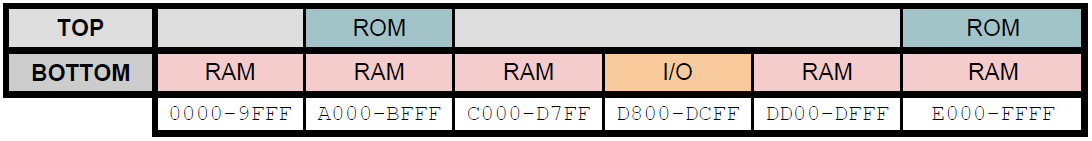

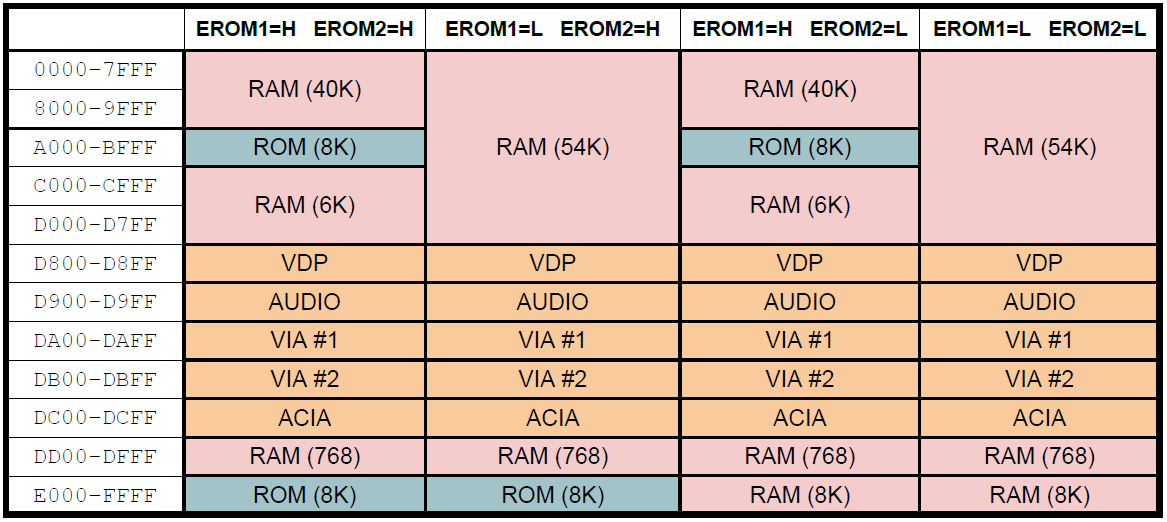

- 64Kb RAM (full addressable on write, visible on read banking out ROM)

- 32Kb ROM (not necessary for first firmware developing phase: full RAM operations)

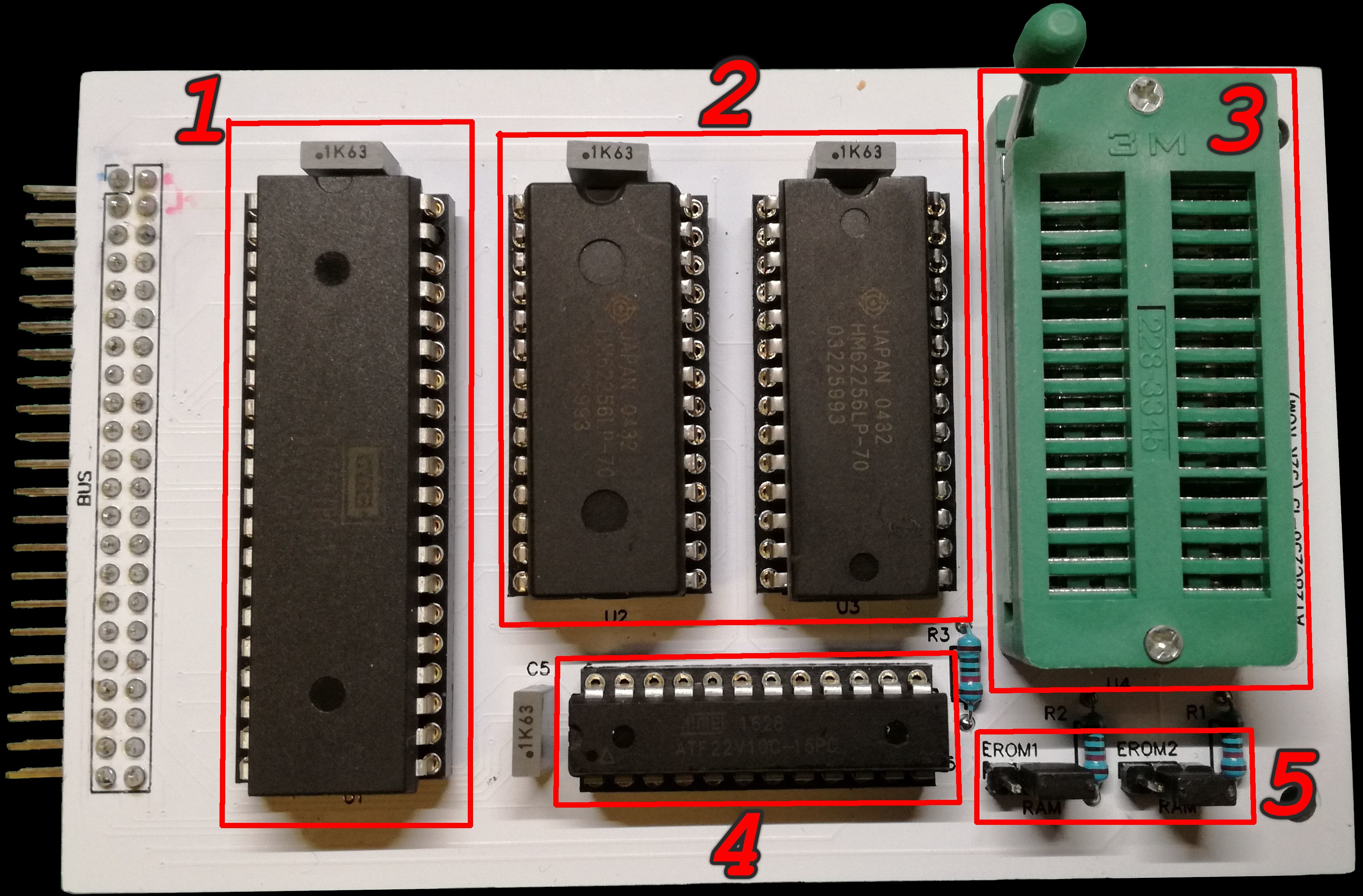

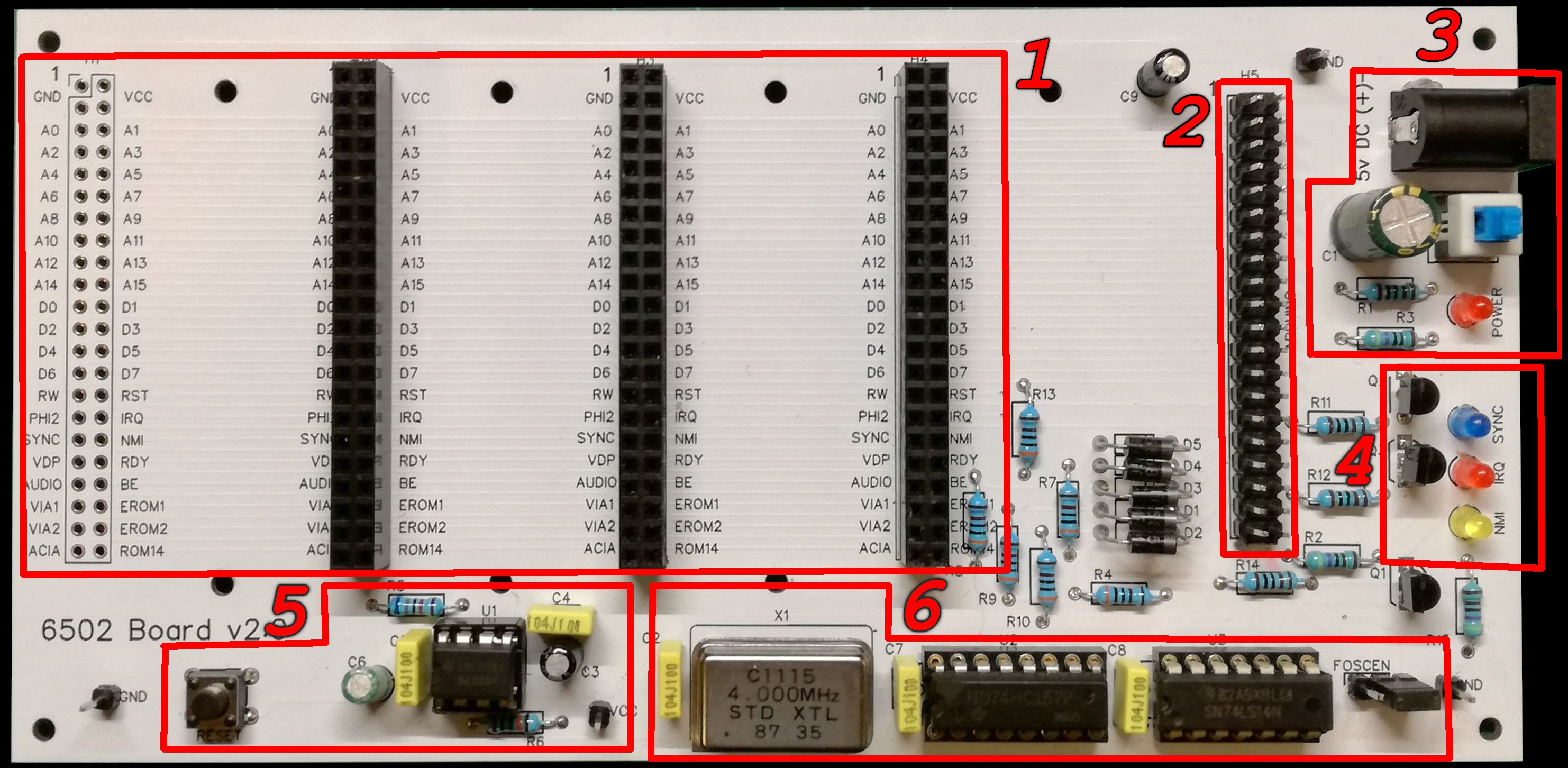

- programmable glue logic (PLD)

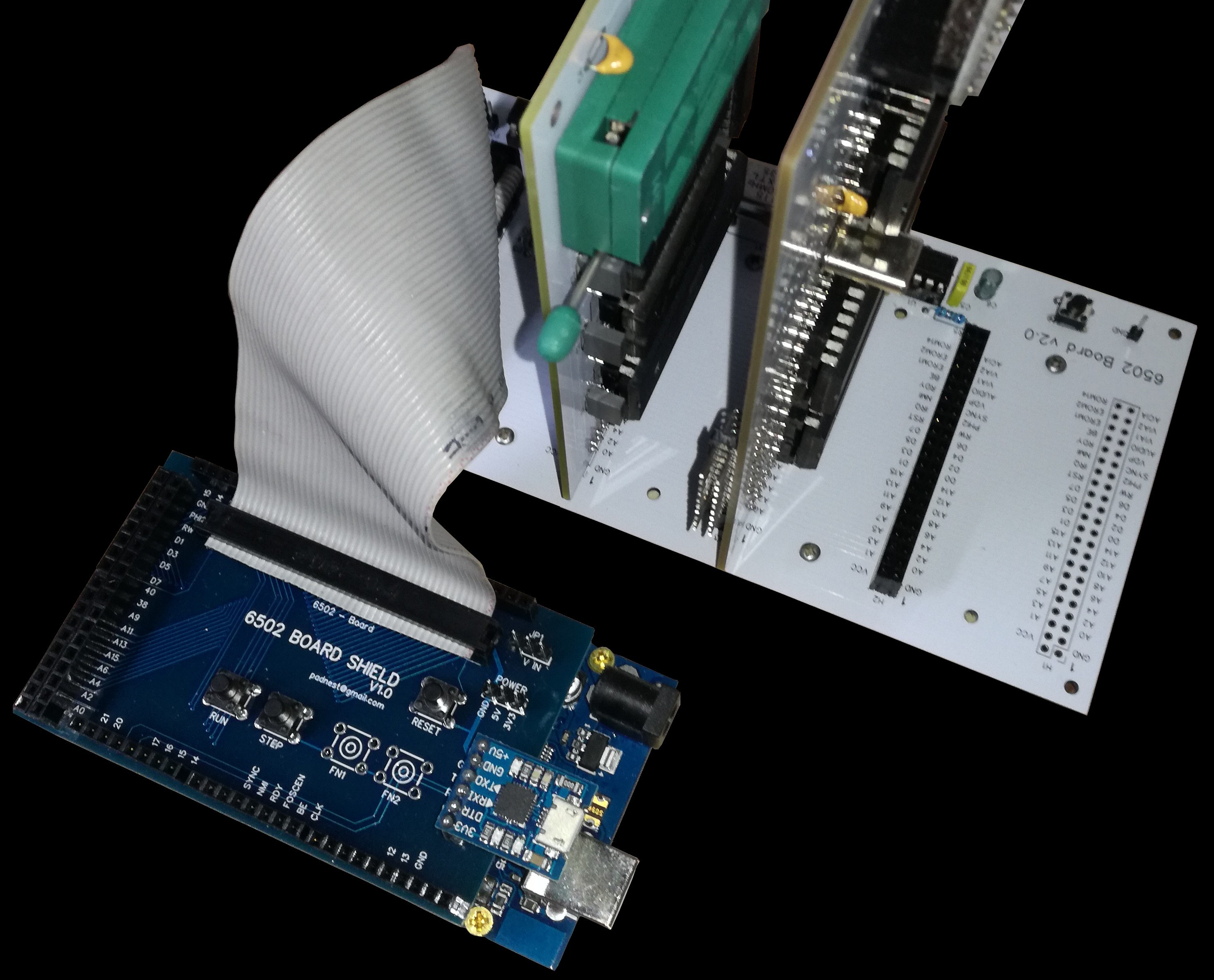

- modularity for CPU, I/O, video and audio controllers

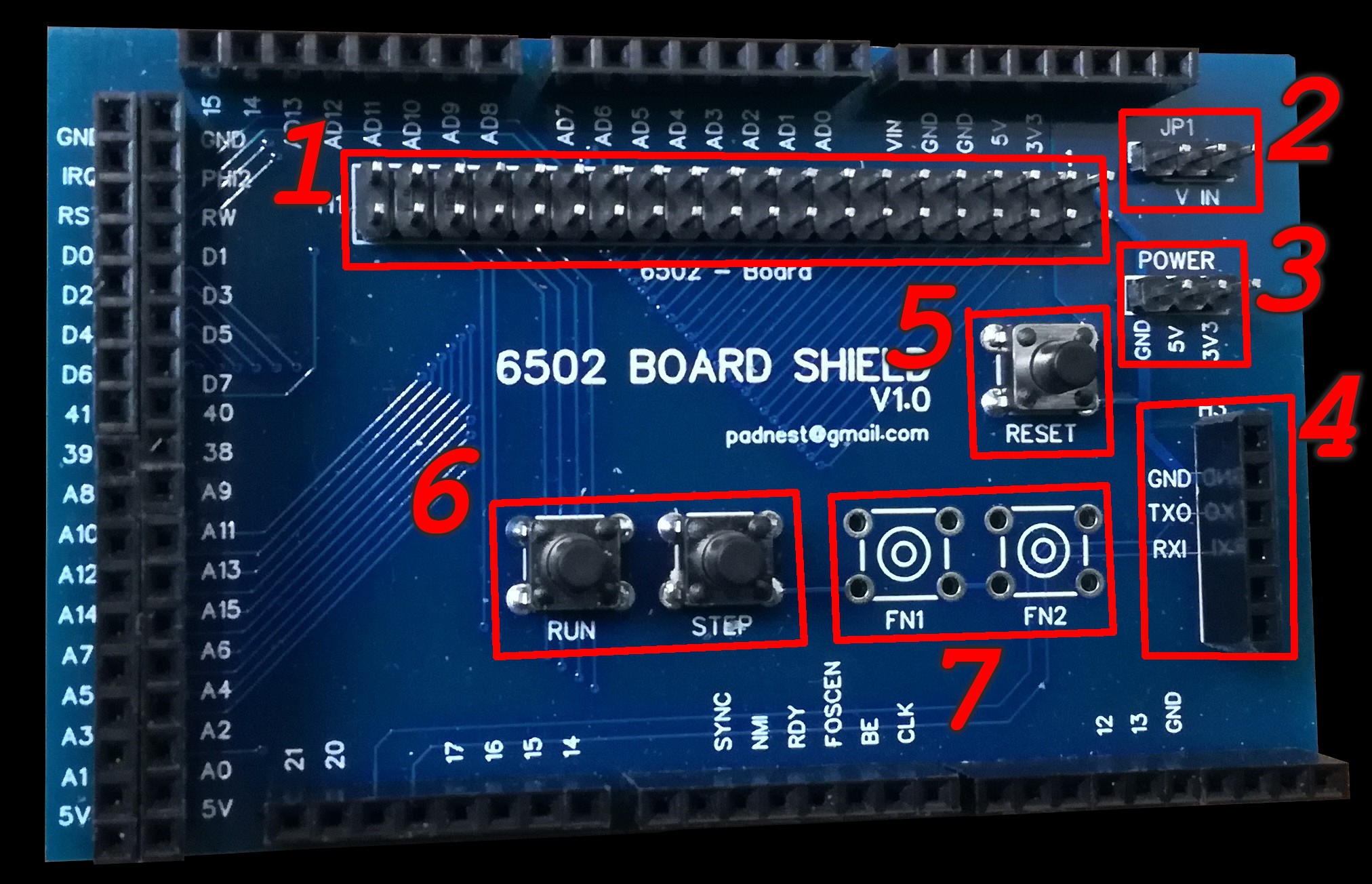

- arduino as debugger, memory inspector and injector, code loader, execution stepper

- 2 clock speeds switchable at runtime: slow (arduino driven) and fast (4 MHZ fosc)

- configurable breakpoints at slow speed (arduino controlled) to stepping execution code

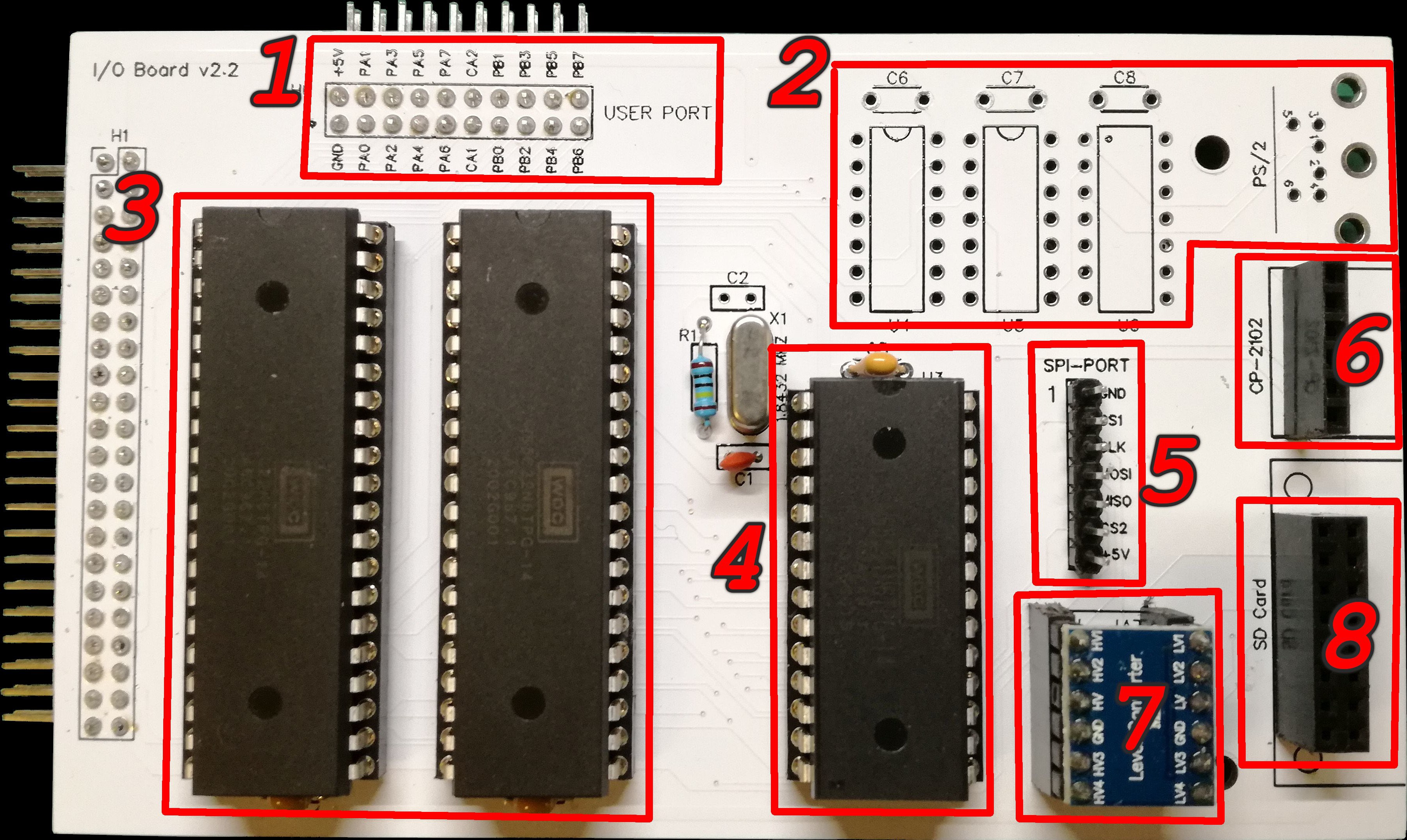

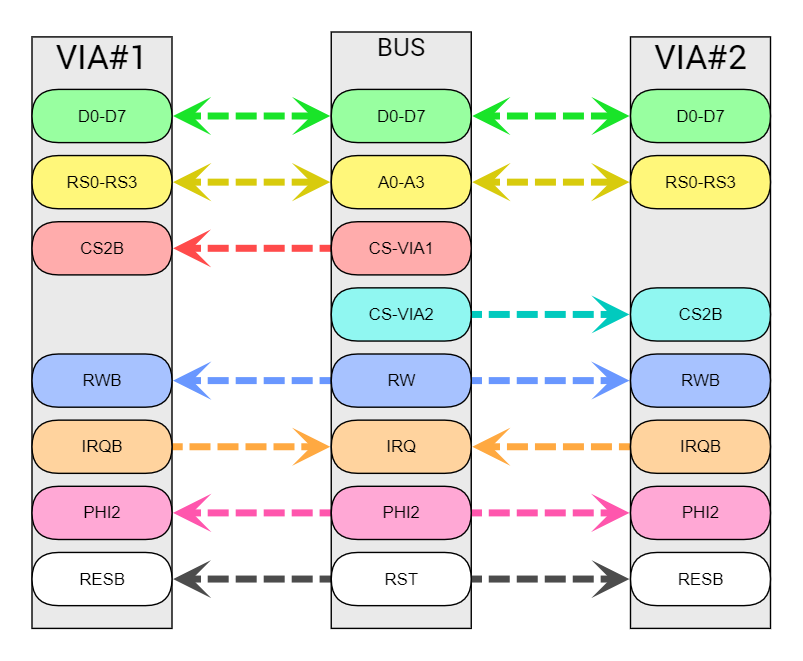

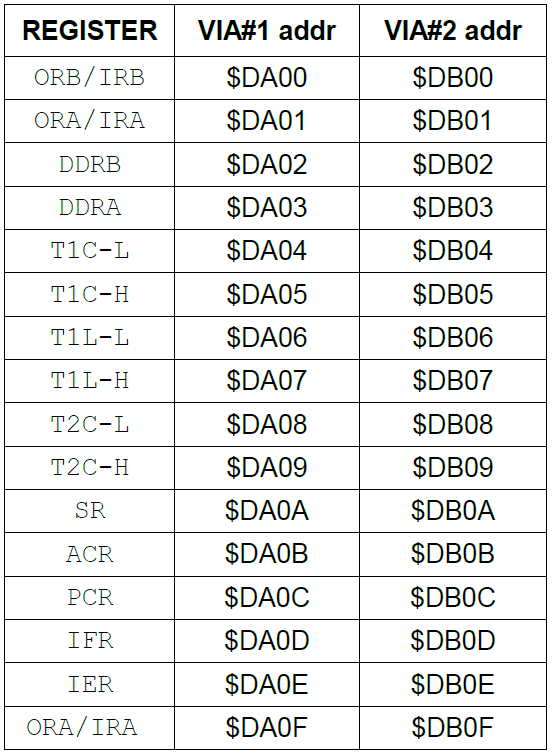

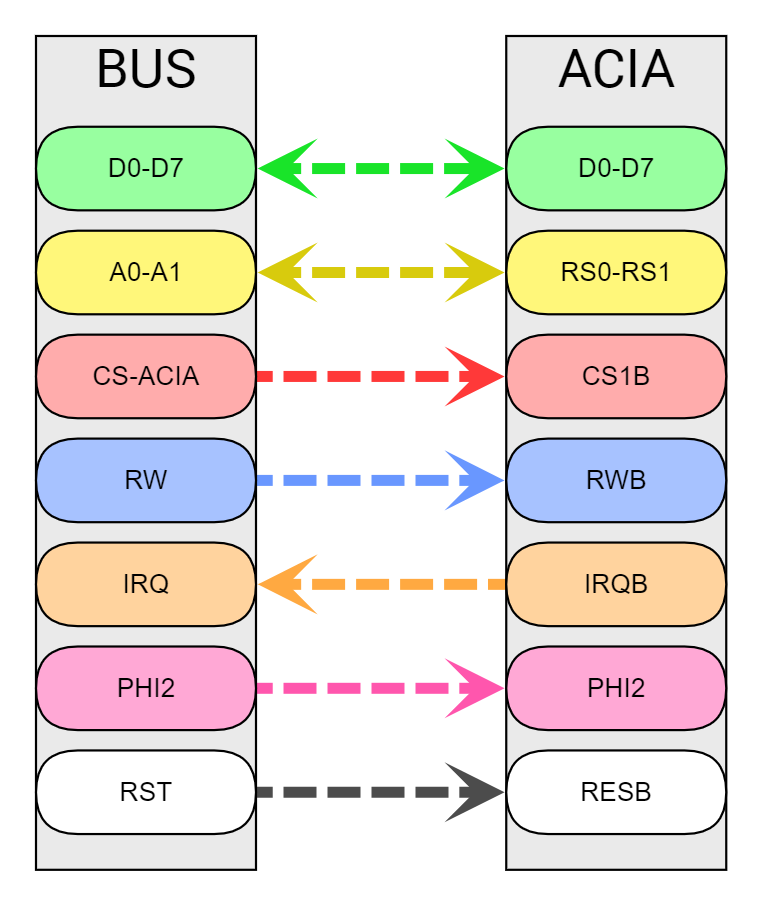

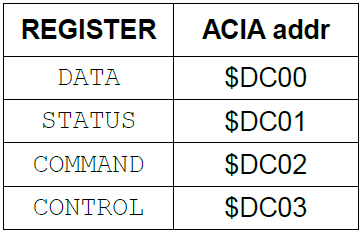

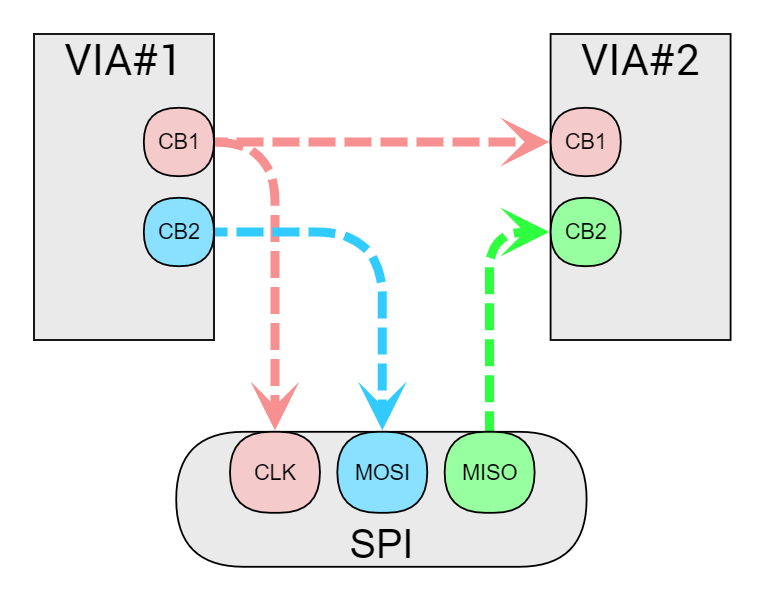

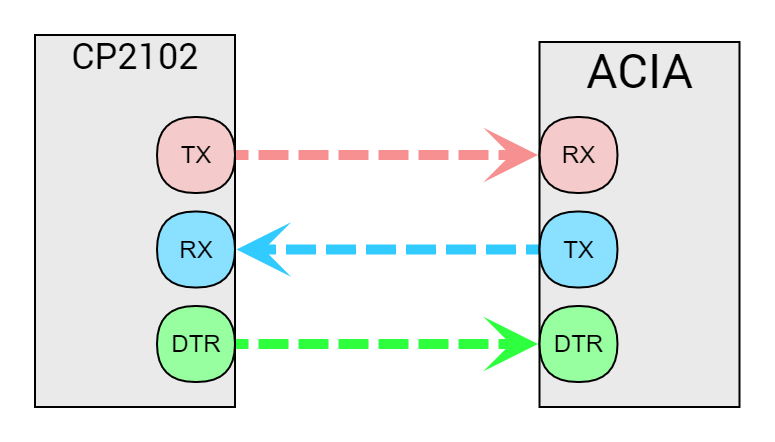

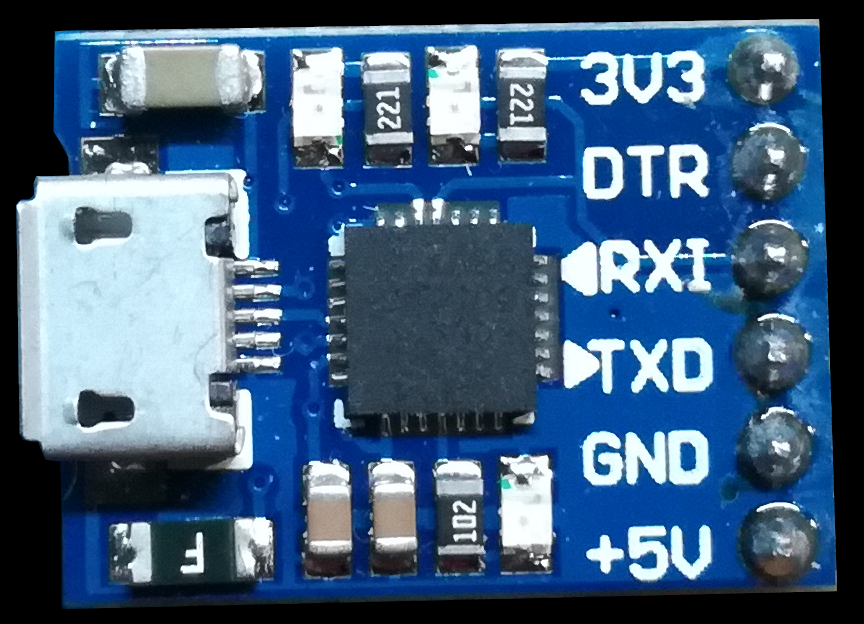

- SPI and serial I/O

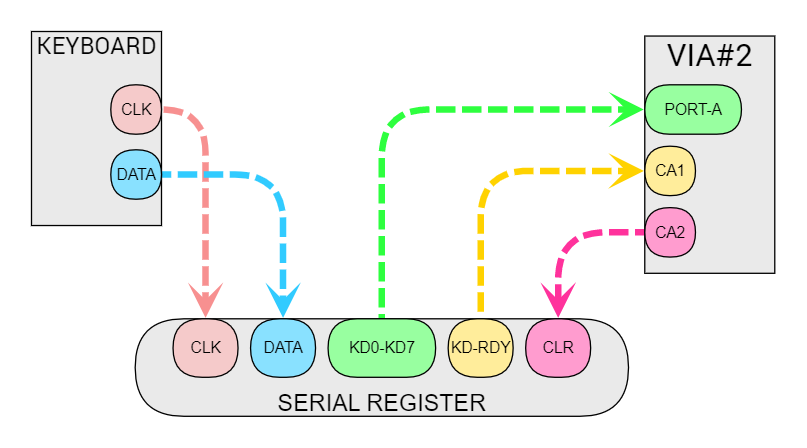

- PS/2 keyboard

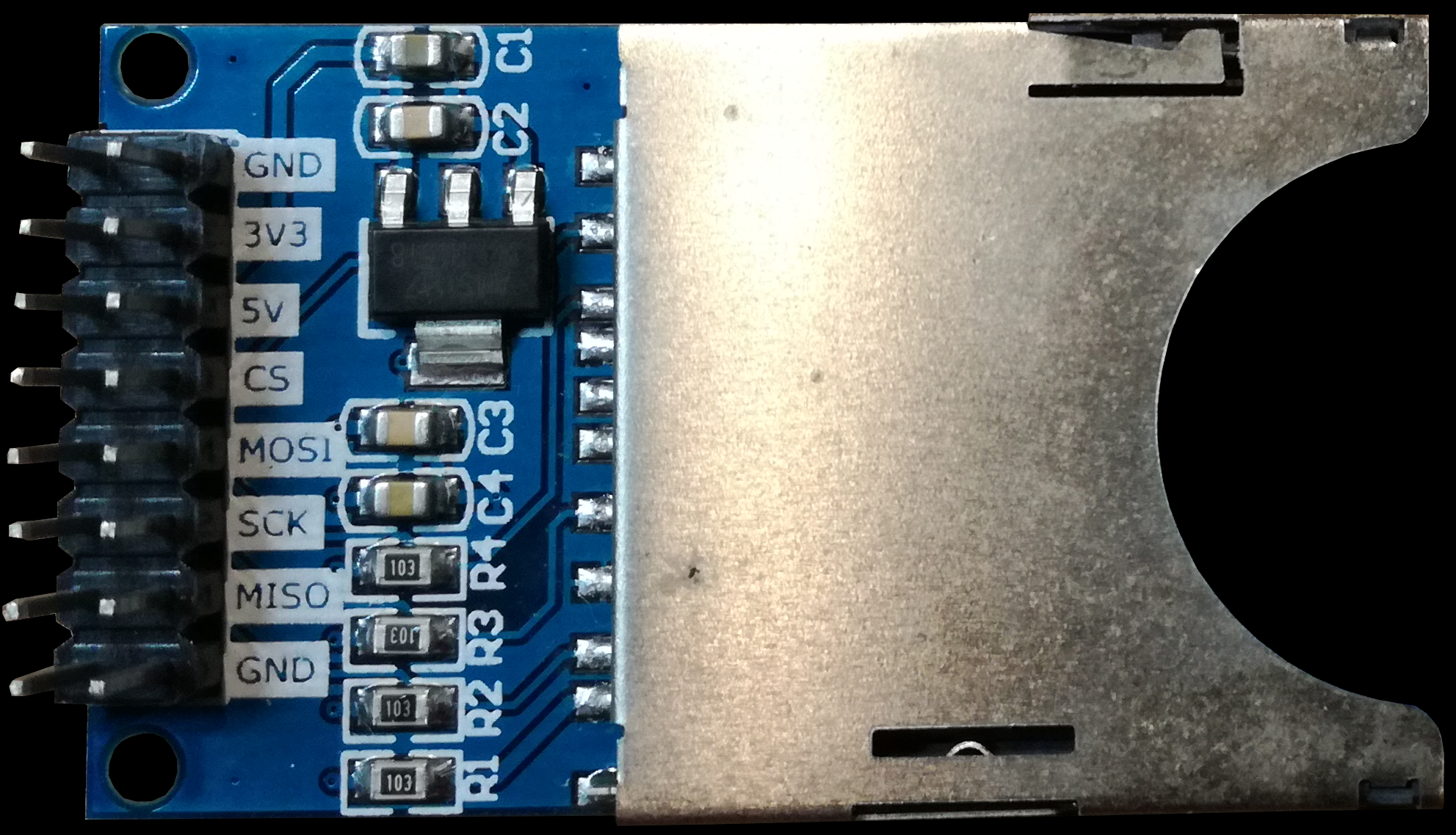

- SD card as storage device

Constraints:

- through-hole only components

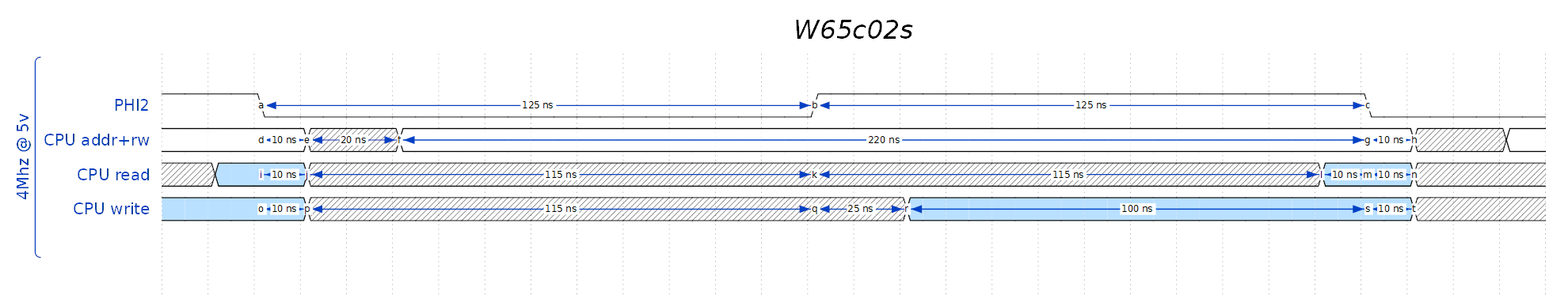

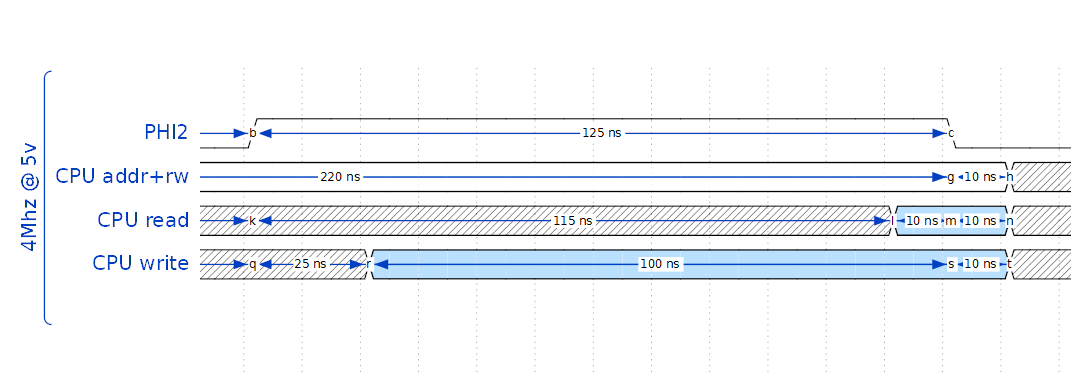

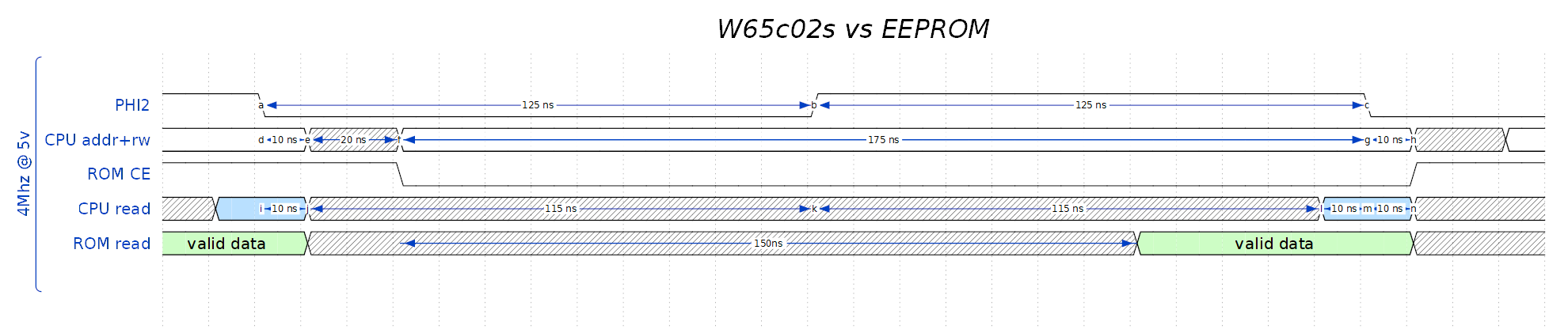

- 4Mhz CPU clock

- WDC W65C02S CPU

Software developing:

- cross IDE and assembler

- direct RAM programming (no need to remove and program the ROM for each code modification)

- stepping execution and breakpoints

padnest

padnest

Keith

Keith

Stephen Willcock

Stephen Willcock

Jac Goudsmit

Jac Goudsmit

Hi. I like this project a lot. Please, could you to show some part of the arduino's code to access to the VIAS's, or something else?