Jelly

** This is still a brainstorm, I'm a newbie in TTL circuits **

most updates at: https://github.com/agsb/jelly/tree/main

What is it ?

Jelly is a concept, a alternative computer with a diferent paradigm, not for performance but for design.

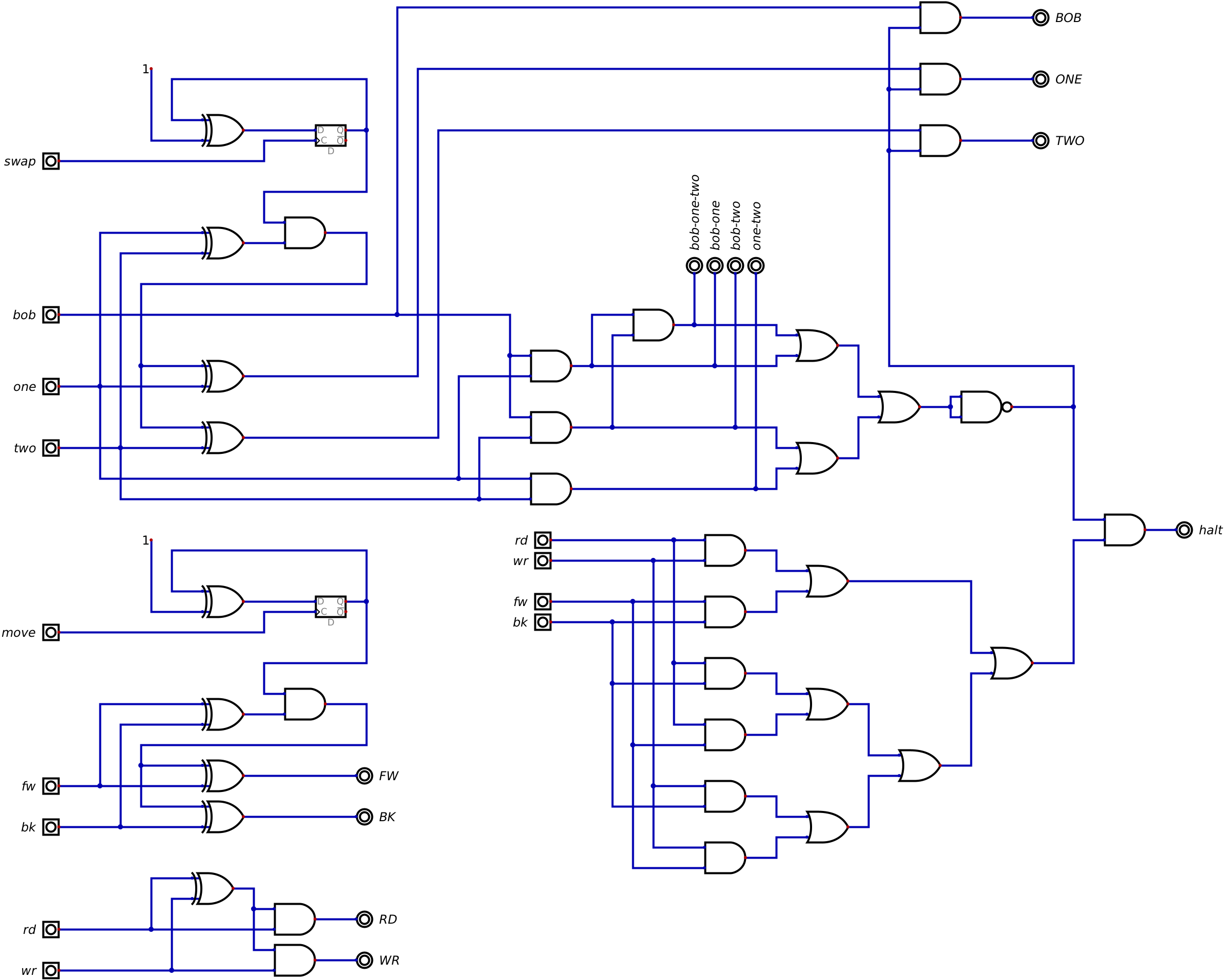

Jelly uses two ideal tapes, first for code (aka ONE), second for data (aka TWO) and a standart input and output device.

Any memory device could emulate a tape.

About op-codes

At first, lets resume the 16 opcodes for Jelly brainfunk;

| ascii | action | origin | details | |

| 1 | > | forward move tape one position | brainfu*k | only data tape |

| 2 | < | backward move tape one position | brainfu*k | only data tape |

| 3 | + | increment byte at tape position | brainfu*k | only data tape |

| 4 | - | decrement byte at tape position | brainfu*k | only data tape |

| 5 | . | output a byte at tape position | brainfu*k | from data tape into standart output |

| 6 | , | input a byte to tape position | brainfu*k | from standart input into data tape |

| 7 | [ | test if byte at data tape is zero, and forward code tape to matched ] | brainfu*k | allow 255 nested loops |

| 8 | ] | test if byte at data tape is not zero, and backward code tape to matched [ | brainfu*k | allow 255 nested loops |

| 9 | ! | halt | Jelly | end of code |

| 0 | = | do nothing | Jelly | nop |

| 10 | = | reserved | jelly | nop |

| 11 | = | reserved | jelly | nop |

| 12 | = | reserved | jelly | nop |

| 13 | = | reserved | jelly | nop |

| 14 | = | reserved | jelly | nop |

| 15 | = | reserved | jelly | nop |

| any | nop | jelly | nop |

Alvaro Barcellos

Alvaro Barcellos

Dave Collins

Dave Collins

6502Nerd

6502Nerd

teardownit

teardownit

Rue Mohr

Rue Mohr