-

V09 Nanocomp 6809 - Does it run Tetris?

01/30/2023 at 21:07 • 0 commentsThis is the latest video in the Nanocomp VGA Video Controller series showing how it is possible to run a Tetris like game on the 8 Bit 6809 Nanocomp built entirely on Breadboards.

-

V08 Part 1 & 2 Tidy up layout and fix minor timing issues

01/22/2023 at 14:53 • 0 commentsNext video in the series to tidy up the main Nanocomp breadboard layout and the video controller layout. Replace 4 logic chips with another Programmable Logic Device (PLD). Update the Nanocomp monitor to initialize the CRTC and load the character generator RAM from ROM at boot up.

And Part 2

Next video will get the Nanocomp running Tetris.

-

Nanocomp V6 and V7 VGA Timing, Cursor and 6 Chips to 1 PLD

12/13/2022 at 20:42 • 0 commentsUpdated the display timing to better fit and enable the cursor. Updated KiCad schematics in GitHub.

Design then simplified with 6 logics chips replaced with 1 Programmable Logic Device (PLD).

-

Version 5 Breadboard VGA video character RAM and video RAM

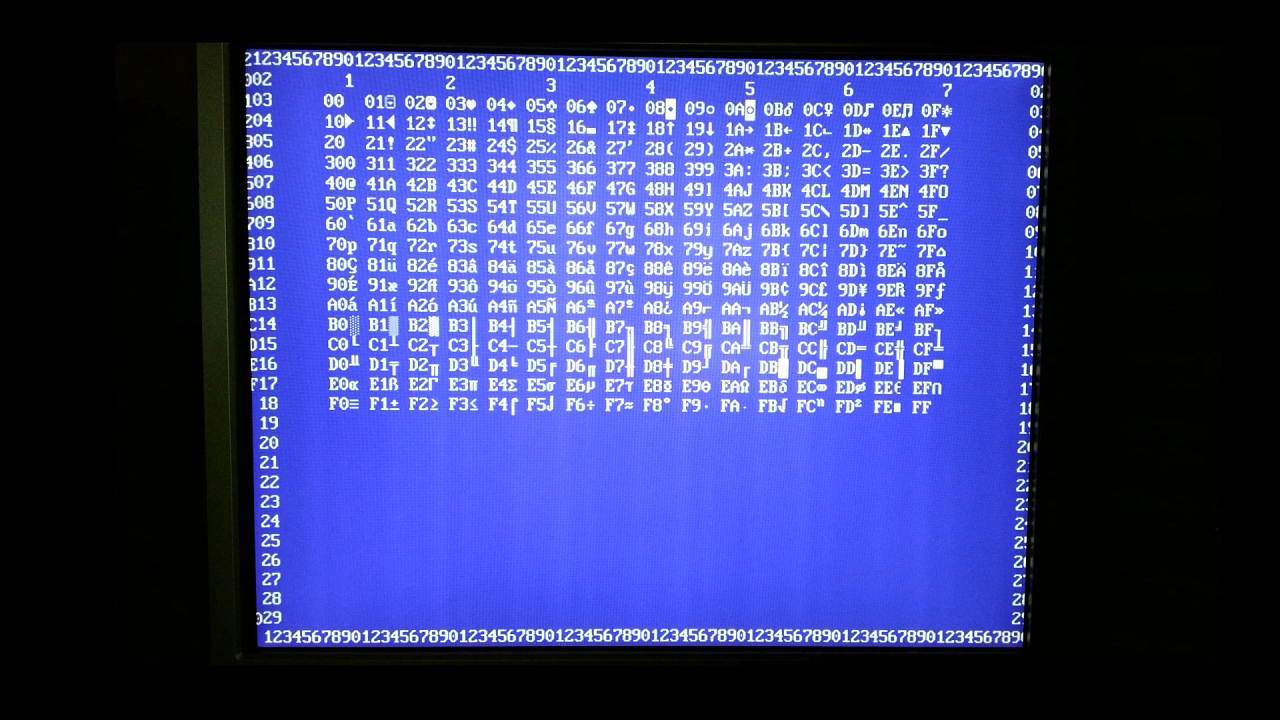

12/02/2022 at 22:02 • 0 commentsFurther updates to add configurable character RAM which allows fonts to by dynamically loaded and character raster images to be redefined for custom graphics shown below for a VGA 8x16 font.

Example image of the VGA characters in the default font

![]()

This is then extended in video 4 where the video RAM is added to allow up to 30 rows and 80 characters with hard coded foreground and background colours (later stages will add upto 256 colours from 262K palette).

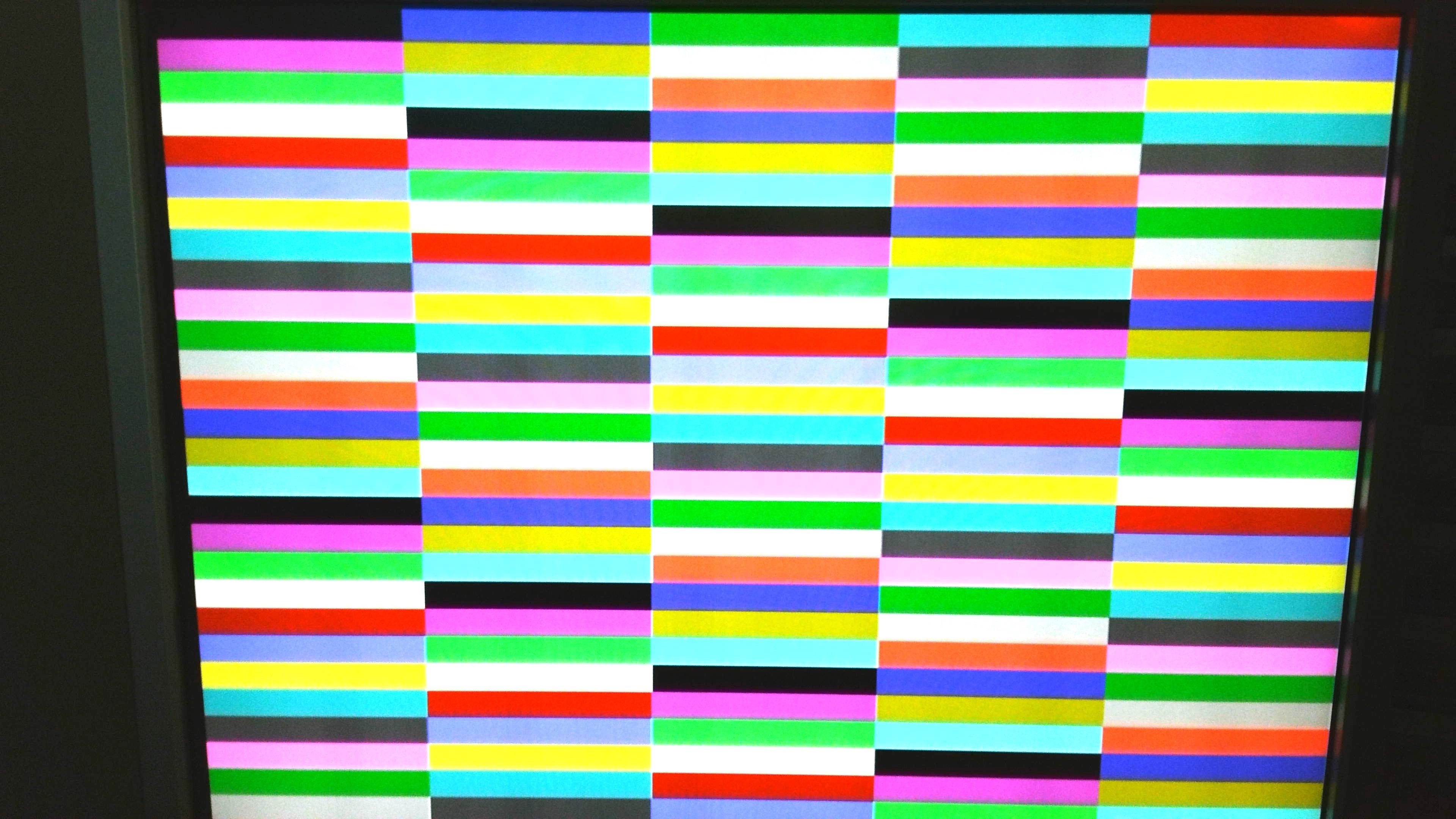

Example image from 20" LCD Monitor

![]()

Future updates to include 16 Colours foreground/background by character, 640x480 2 colour graphics and 320x200 256 colour graphics.

-

Version 5 Breadboard VGA video CRTC & Video DAC

11/23/2022 at 21:52 • 0 commentsThe next stage of the Nanocomp project. In Version 5 we are starting to add a VGA compatible video controller on breadboards to the project. The introduction video V01 explains the steps which will build the controller in stages. Some screenshots of an earlier version of the project included below too.

The second video starts to build out the video controller with the Motorola 6845 compatible CRTC to generate the Vertical and Horizontal Sync outputs and a simple resistor video Digital Analogue Converter (DAC) to generate VGA compatible Red Green Blue signals.

The image below shows the RGB inputs connected to the CRTC Memory Address lines to generate a test pattern showing the 16 colours generated by the simple resistor DAC.

![]()

V5 Schematic Diagram updated with initial video card details in Nanocomp6809V5.pdf in files section. KiCad files uploaded in GitHub

-

Version 4 PLD address decoder and 64K Memory Map

11/13/2022 at 23:11 • 0 commentsThe next update to the Nanocomp has been provided on YouTube and GitHub.

The first video discusses how to ensure reliable breadboard projects by making sure the power distribution to the project is good as possible. Many people reproducing breadboard projects such as those like Ben Eaters have difficult to trace problems with power, normally because voltages on some breadboards drop to below 4 Volts. The recommendations are then applied to the Nanocomp project.

With Version 4 the original design address decoder was replaced with an Atmel ATF22VL10 PLD (GAL) Programable Logic Device. This was first confirmed as working with the Original Memory map.

The final part shows how the original 32K Memory map of the original 1981 Nanocomp design was updated to use the full 64K address range of the 6809 processor. The Atmel ATF22VL10 PLD was updated for the next 64K memory map and the Monitor ROM updated to run from the top 32K of memory.

GitHub has been updated with the latest KiCad schematic, the PLD configuration files and the revised Monitor assembler source.

The next updates after this will be adding a VGA compatible video controller to the design over a number of iterations.

-

V3 Add Data, Address and Control Bus Buffers to protect/expand CPU

11/07/2022 at 21:17 • 0 commentsThe Motorola MC6809 datasheet states that the Data and Address bus signals can drive up to 4 LS TTL loads.

V1 and V2 of the Nanocomp design only have 4 chips consuming Data and Address bus signals from the CPU.

To support future expansion such as adding a video controller and video RAM will require buffers to drive the Data, Address and Control Bus signals (E Clock and R/W).

4 Buffer chips, Data Bus 1 x 74LS245, Address Bus 2 x 74LS541, Control Bus 1 x 74LS241 have been inserted onto a new breadboard between the CPU and the rest of the project.

The video of adding the bus buffer board is below.

The full Nanocomp Playlist shows creating the Breadboard computer from start to finish.Further developments are planned. Exact Version numbers may change.

Version 4 Will expand the address space used from 32KB (A15 was not used in the original Nanocomp) to 64KB and the accessible RAM will be expanded from 4KB to 32KB.

The full 8KB of the EEPROM will also be usable.

The address decoder will be replaced using an ATMEL ATF22LV10 Programable Logic Device (PLD or GAL) which will allow more complex rules to be configured without needing lots of logic chips.Version 5 will add a VGA compatible video card capable of 640x480 Text and basic graphics in 16 colours running on breadboards.

Version 6 will try and implement some form of Tetris type game (though without sound), so the response to "Does it run Tetris" can be yes! This spec of hardware will never be able to run Doom!

The documents, datasheets, ROM binaries, source and other files are all maintained in GitHub

To keep up to date Subscribe to the Breadboarding Labs Channel

-

Version 2.0 adds a serial port and updates Monitor to Save and Load SREC

11/03/2022 at 00:37 • 0 commentsVersion 1.0 of the Nanocomp 6809 re-produced the same design as the 1981 version so the original Monitor ROM could be used unchanged. The Cassette interface electronics was not re-produced as this would be obsolete with the introduction of a serial port connected to a modern PC over USB.

Version 2.0 of Nanocomp is possible as the original Monitor ROM has been disassembled in video 12 in the Nanocomp 6809 Playlist so that enhancements can be made to support a serial port.

The Motorola MC6850 is used to provide a serial port, with a dedicated clock with frequencies designed to divide down to common Baud rates (9600 Baud, 8 Bits, No Parity is used). Rather than using the RS232 serial standard which requires +/- 12V signals, a TTL to Serial USB adaptor is used to interface the MC6850 to the PC. The RealTerm terminal emulator is the used to test the serial ports and for loading and saving SREC program files.

Further developments are planned. Exact Version numbers may change.

Version 3 will add Data, Address and Control line buffer chips to allow expansion of the Nanocomp beyond the 4 LS TTL loads the 6809 supports. This will also expand the address space used from 32KB (A15 was not used in the original Nanocomp) to 64KB and the accessible RAM will be expanded from 4KB to 32KB. The full 8KB of the EEPROM will also be usable.

Version 4 will add a VGA compatible video card capable of 640x480 Text and basic graphics in 16 colours running on breadboards.

Version 5 will try and implement some form of Tetris type game (though without sound), so the response to "Does it run Tetris" can be yes! This spec of hardware will never be able to run Doom!

The documents, datasheets, ROM binaries, source and other files are all maintained in Github

To keep up to date Subscribe to the Breadboarding Labs Channel

-

Version 1.0 Nanocomp uses same Monitor as 1981 version

11/03/2022 at 00:13 • 0 commentsVersion 1.0 of the Nanocomp was built to re-use the original Monitor ROM (though copied onto a new EEPROM) and uses almost the same design.

There have been a few updates. The original RAM used 2 x 2114 1Kx4 bit Static RAM. These have been replaced with a modern 1278KB static RAM. In Version 1.0 we only use 4KB of the 128KB. The original EPROM required UV erasing so these have been replaced with more recent EEPROM such as the ATMEL 28C64B 8KB EEPROM.

The MC1413 Darlington driver chip was not available and was replaced with a ULN2803A Darlington Driver which has the added benefit of being TTL compatible, so it does not need the additional 5K6 resistors the original design had.

The 7442 BCD Decoder/Driver was not available and was replaced with the 74LS145 which is capable of driving higher currents as well.

The original crystal was about 3.5Mhz due to the RAM and ROM having slower 450ns access times. This is not necessary with the more recent chips so the speed was increased to 4Mhz.

The modern 7 Segment LED Displays have the E & F segments reversed compared to the 1981 design so this has to be considered when viewing the old schematics.

Videos 1-9 in the Nanocomp 6809 Playlist cover the construction of version 1.0

Videos 10, 11 and 12 cover the testing and exploring the Monitor, simple Machine Code programming and disassembling the original Monitor binary code into assembler source which can be re-assembled back to the same binary image,

Videos 13,14 & 15 cover Nanocomp Version 2.0 which includes a Serial Port and updating the Monitor Save and Load to/from tape to work with the serial port using the Motorola SREC text format for transferring executable code.

Nanocomp 6809 8 Bit Retro Computer on Breadboards

Wireless World Magazine in January and June 1981 published this design. Reproduced on solderless breadboards using the original Monitor ROM

Dave Henry

Dave Henry