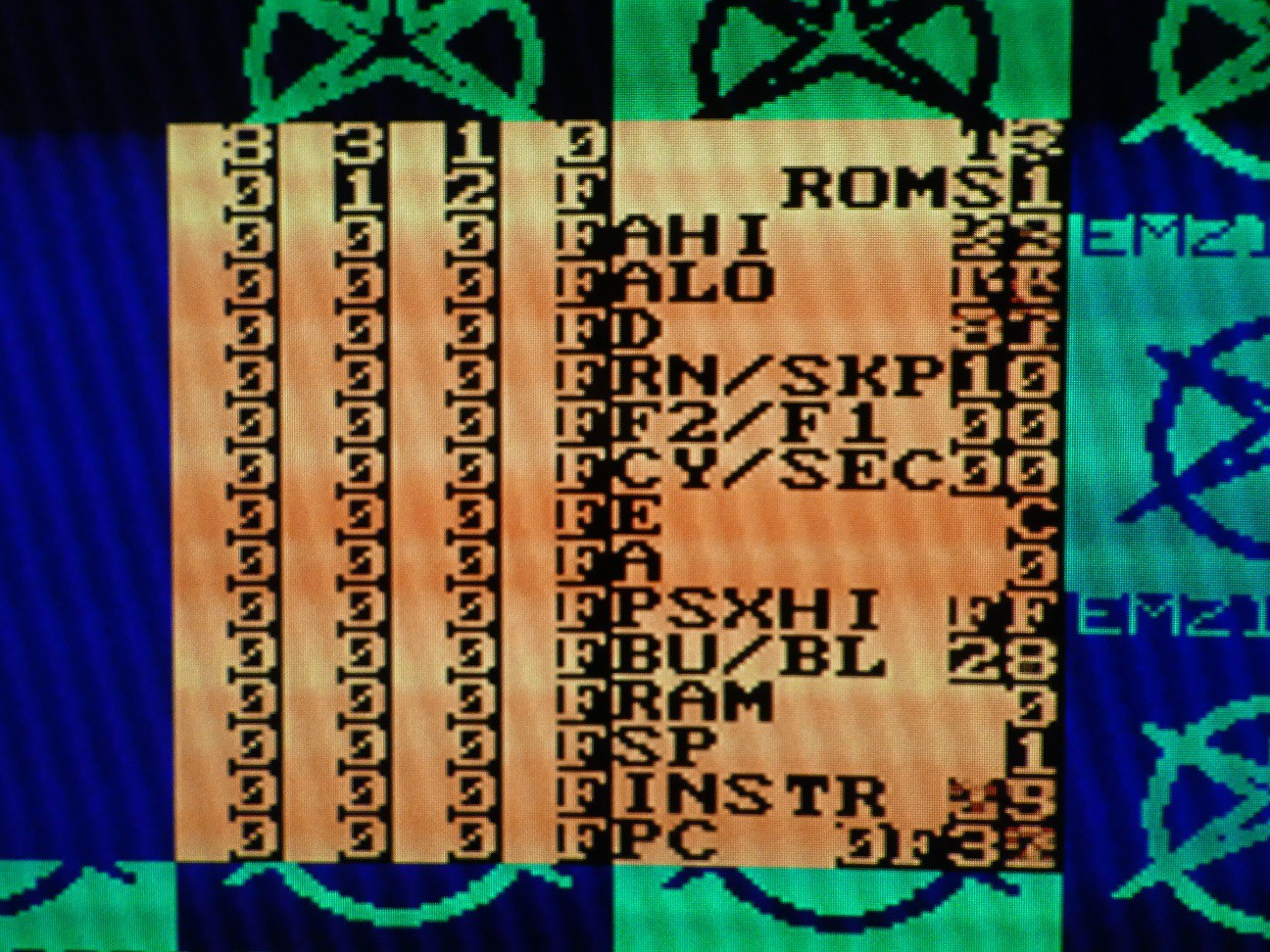

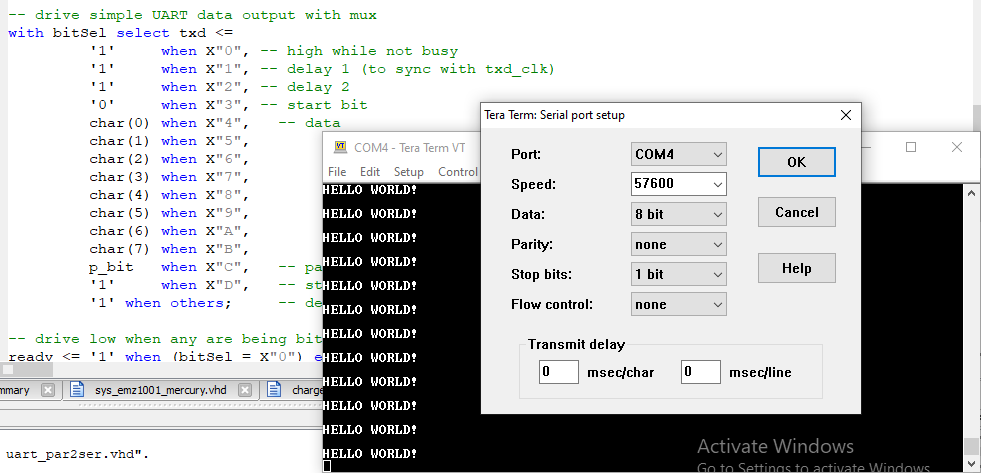

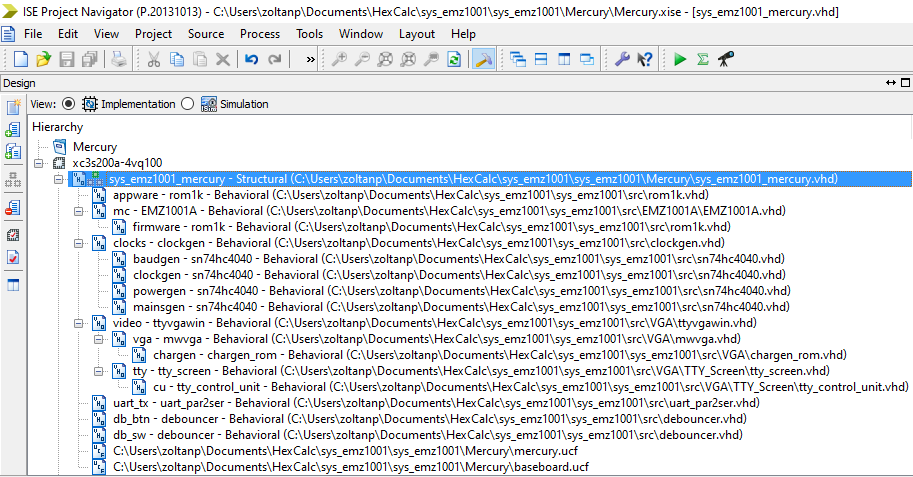

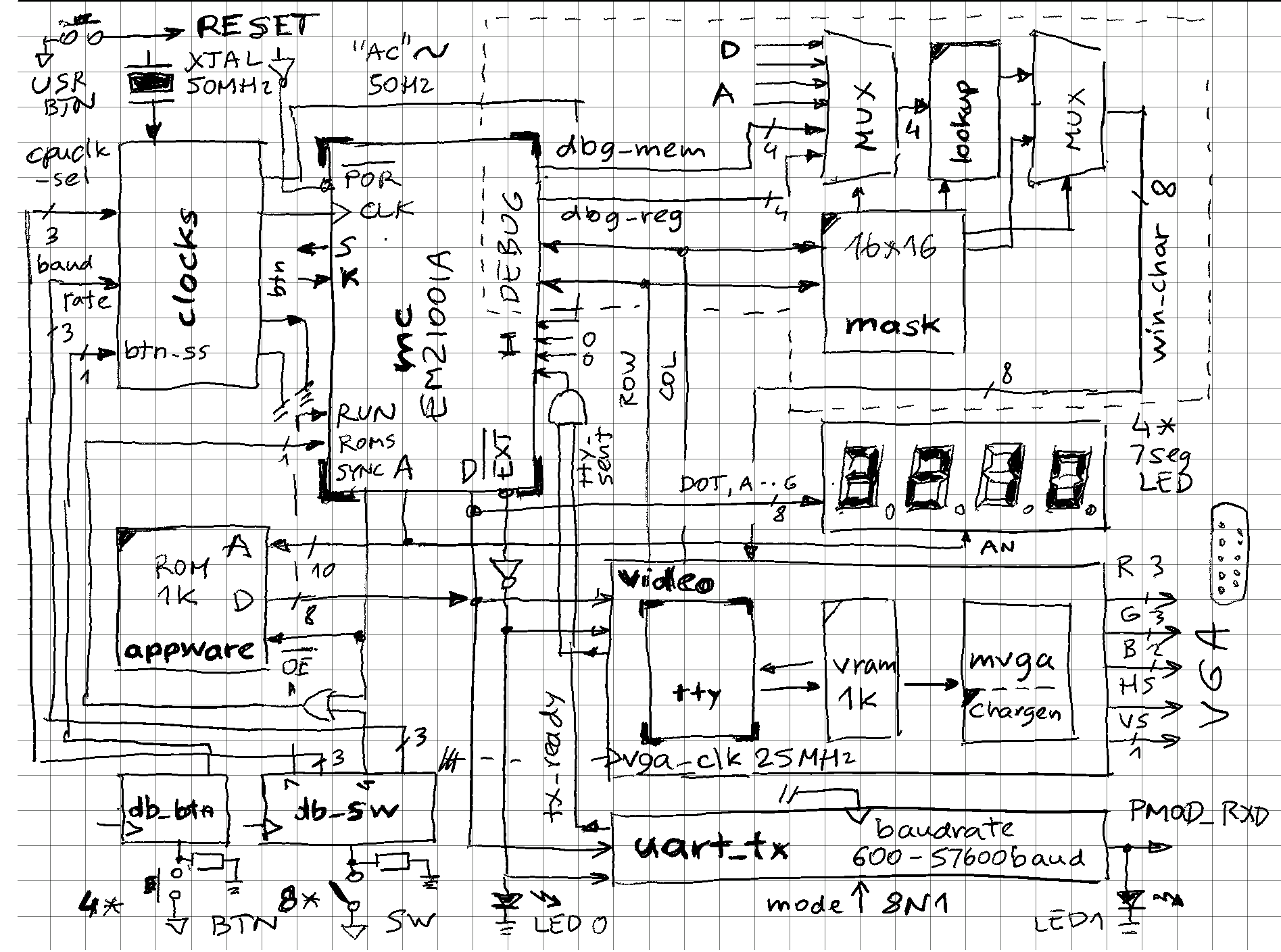

Demo video: Mercury FPGA board running a virtual EMZ1001A based system, which displays "Hello World" and Fibonacci sequence to VGA, UART and 7-segment LED

The development of this project is mostly done now, and the code posted on github is fairly stable and complete.

In upcoming weeks my focus will be on documenting the most interesting aspects of the design.

UPDATE 2022-12-16: Finished "System description" log entry

UPDATE 2022-12-18: Finished "Recreating a simple EMZ1001A assembler" log entry and uploaded demo video to YouTube

UPDATE 2022-12-19: Finished "Test code: Fibonacci sequence generator" log entry

UPDATE 2022-12-20: Finished "Test code: HELLo WorLd!" log entry (and updated previous one)

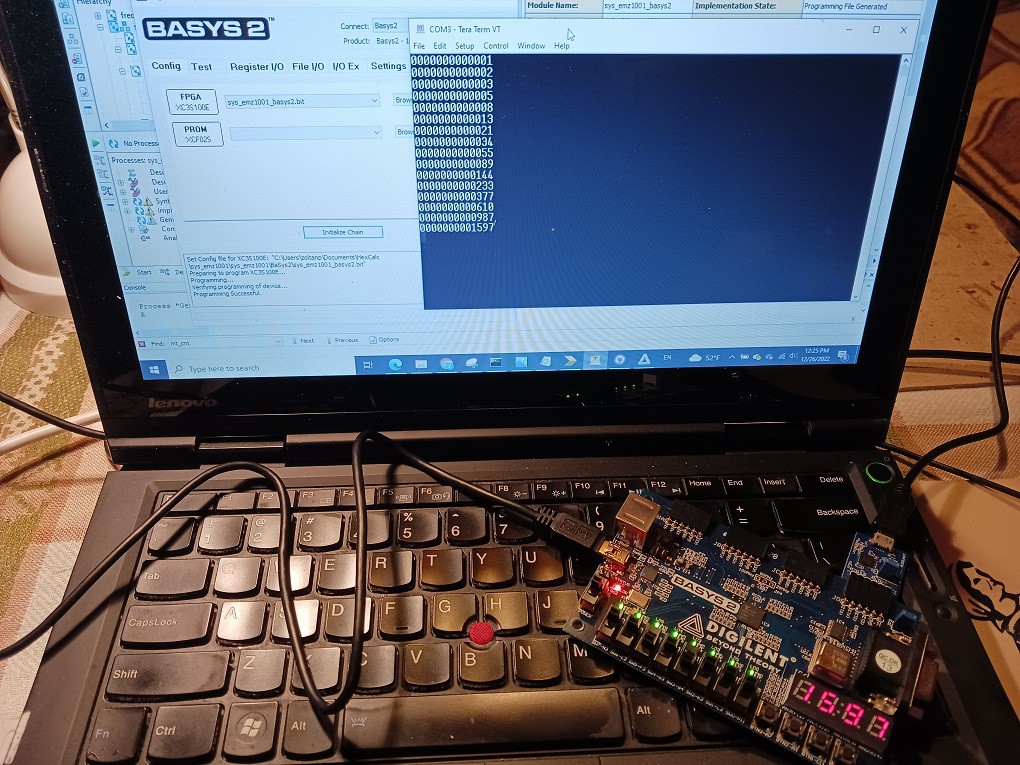

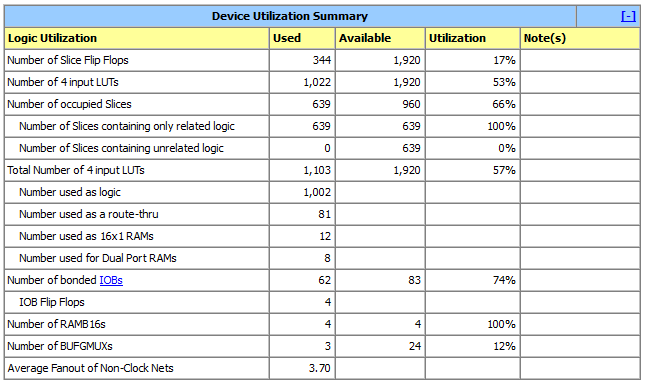

UPDATE 2022-12-26: Added "Running it on BaSys2 FPGA board" log entry

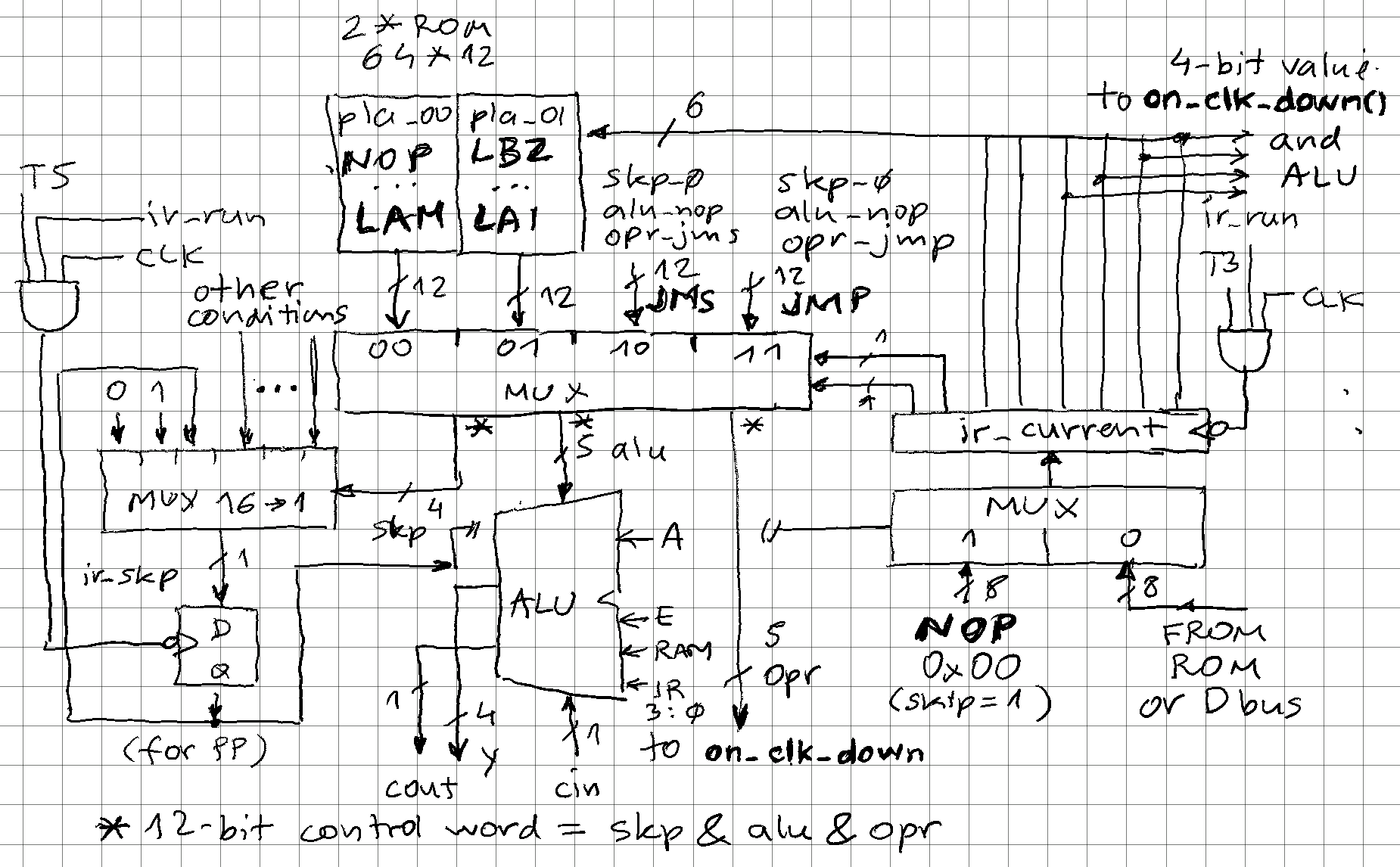

UPDATE 2022-12-26: Rewrote "Implementation in VHDL - instruction decode and control signals" log entry

UPDATE 2022-12-27: Added "Implementation in VHDL: RAM and lookup tables" log entry

zpekic

zpekic

Hi there, you certainly do come across strange fascinating beasts. Looking forward to reading the progress of this. 👍