La porte OU Exclusif est une sacrée histoire, comme on peut le voir sur ce petit bestiaire de topologies de XOR. Les configurations possibles sont multiples, selon les contraintes de fan-in et de fan-out. Des configurations à faible nombre de transistors existent mais reposent sur des transistors dont on peut contrôler les ratios donc les résistances, et jouent sur les rapports de transconductance, donc la consommation statique n'est pas insignifiante. On trouve aussi plein de versions sur https://www.vlsitechnology.org/html/cells/vsclib013/xor2.html.

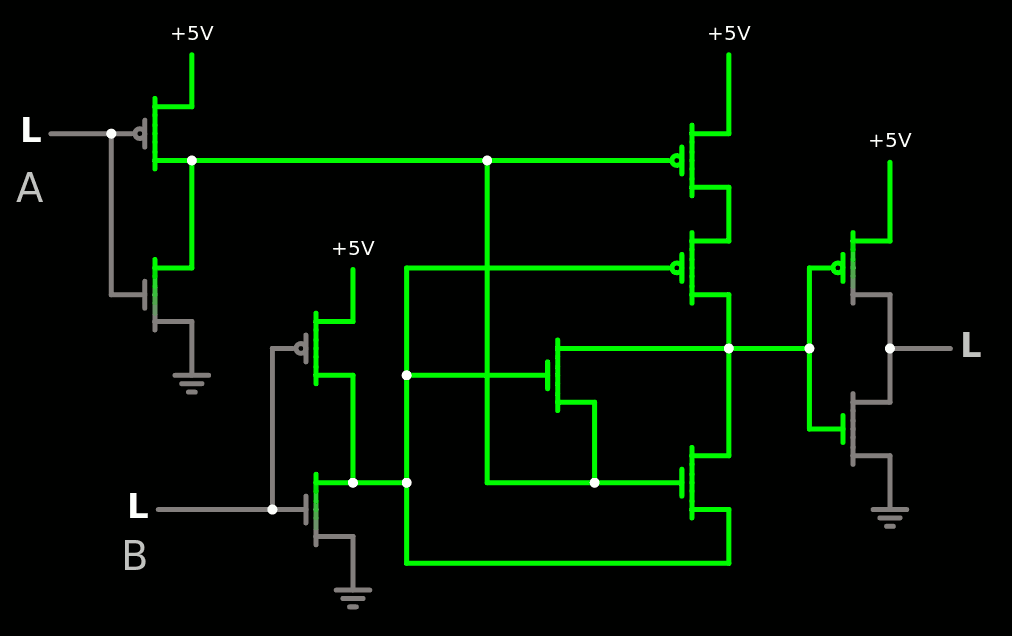

Pour le cas ci-dessous, tous les transistors sont considérés comme ayant le même ratio, ce qui permet à la cellule d'être portable sur un maximum de technologies et PDK.

Pour un fan-in de 1 et fanout acceptable, on s'en sort avec 10 transistors:

Les inverseurs d'entrée et de sortie ne sont pas optionnels, à moins que la cellule soit connectée directement à une cellule voisine dotée d'un inverseur de sortie. On pourrait faire une version XNOR avec un faible fanout en enlevant l'inverseur de sortie.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

je pense que nos circuits devrais être concus avec un fanin implicite de 1 ^^

Ca leur permet d'être générique, c'est au designer de s'assurer que le fanin soi correct.

Ainsi les inverseur des inputs pourrais être supprimer.

je comprend l'importance du fait d'avoir un inverseur sur les inputs, mais je ne vois pas de cas ou il pourrais ne pas y en avoir (dans un circuits cmos en tout cas).

Are you sure? yes | no

Faut vraiment faire un log à ce sujet :-P

Are you sure? yes | no

Du grand art !

merci !

Are you sure? yes | no

On en arrive en fait à la même chose que xor2v1x05 ou xor2v2x05 de la VSCLib https://www.vlsitechnology.org/html/cells/vsclib013/xor2.html donc rien de bien original :-)

Are you sure? yes | no