All the details, including all of my mistakes, are on www.blinkingcomputer.org. When I finish something big then I post it to a project log here.

The Blinking Computer

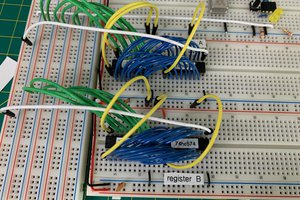

An educational 16-bit CPU made from < 1024 transistors with lots of LEDs that anyone can build and learn from

Tony Robinson

Tony Robinson

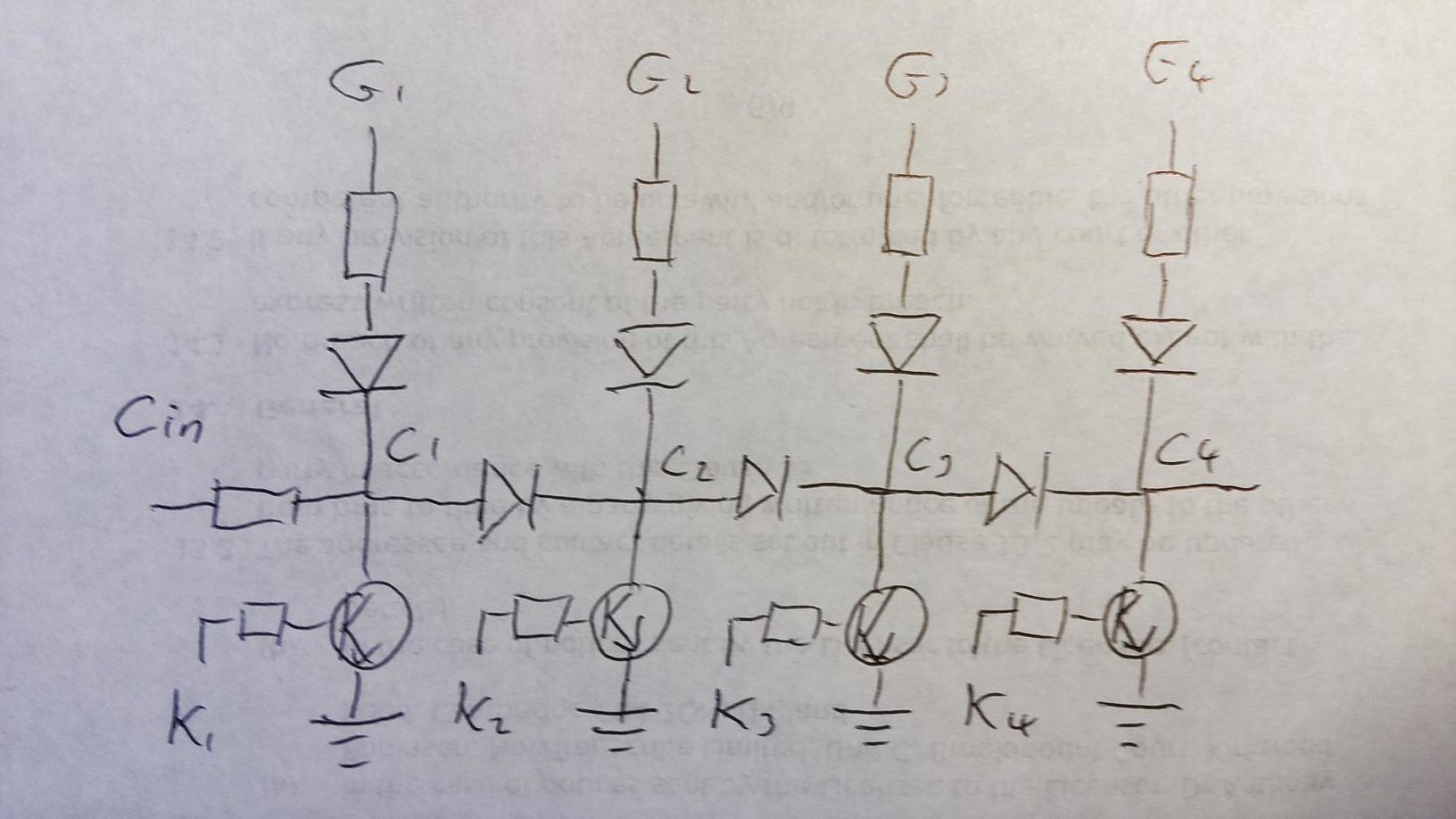

Generate, G, is high if both inputs are high. Kill, K, is high if both inputs are low. The carry goes in on the left, if K1 is high then the first NPN is on and the carry is grounded, if G1 is high then the carry out is high else the carry is propagated. That's pretty simple, I feel confident I can both get this implemented in a way that you can see the signal flow (as above) and thus be able to explain how this time-critical bit of a CPU works to all.

Generate, G, is high if both inputs are high. Kill, K, is high if both inputs are low. The carry goes in on the left, if K1 is high then the first NPN is on and the carry is grounded, if G1 is high then the carry out is high else the carry is propagated. That's pretty simple, I feel confident I can both get this implemented in a way that you can see the signal flow (as above) and thus be able to explain how this time-critical bit of a CPU works to all.

Blair Vidakovich

Blair Vidakovich

Jorj Bauer

Jorj Bauer

Matt Lacey

Matt Lacey

Brandon Reinhart

Brandon Reinhart

is possible to create emulator for non elektronics?