Oh so I messed with the Karnaugh map... Here's a proper set.

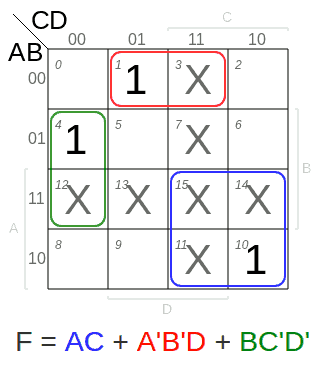

LSB:

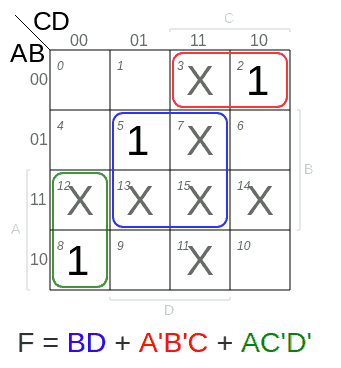

MSB:

By chance there are a couple of common terms, /A/B and /C/D.

The "good" aspect is that 5 of the 7 X turn to 1s so 3 of the unexpected or forbidden cases turn to mark 11, which also increases the avalanche to the PEAC level.

------------------------------------------------------------

In other words :

inputs:

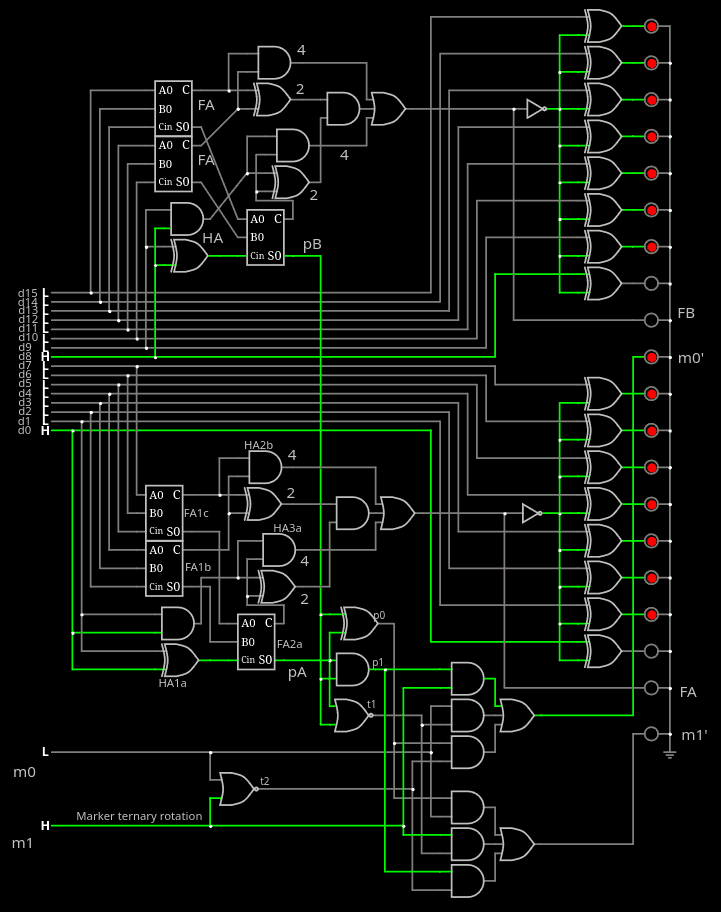

inputs: A0 = D A1 = C B0 = B B1 = A t1 := /B0./B1 t2 := /A0./A1 LSB := (A1.B1) | (t1.A0) | (t2.B0) MSB := (B0.A0) | (t1.A1) | (t2.B1)

Note : t1 & t2 can be pushed before,

- t1 is easy to compute early as m1 nor m0,

- t2 as pA nor pB.

The circuit : this time I made extra efforts to check each input. The complexity increased a bit but latency is still the same as the last version so OK.

Time to rererereredo the VHDL.

-----------------------------------------------------------

And it's a success ! get the source code here.

Number of PopC errors = 623472/1048576

Number of type errors = 39204

A good number of invalid data get transformed to mark=11 and thus flagged as "type errors".

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.