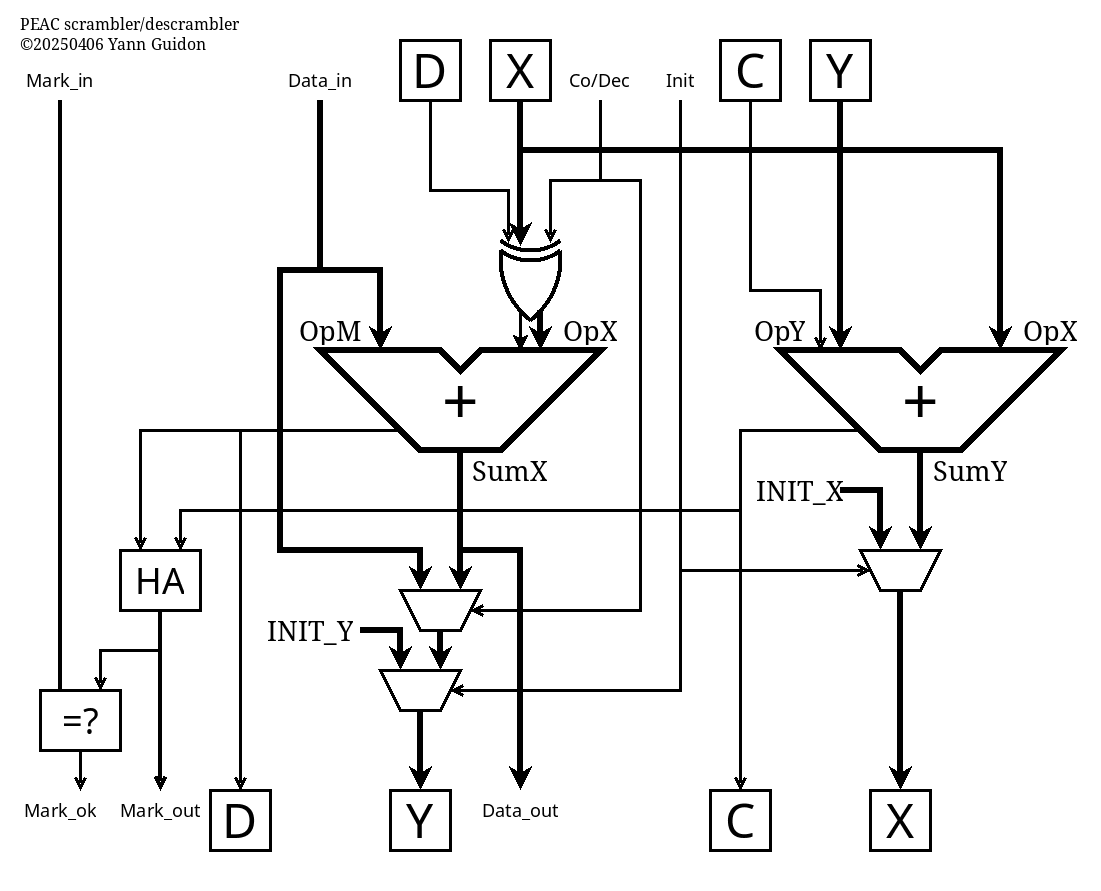

I'm reworking the PEAC scrambler and the result is a single unit that does both scrambling and descrambling.

The only meaningful difference is that SumX is available immediately on Data_out, without waiting for the register Y. This affects the timing, a little.

Of course, during synthesis, the optimiser can reduce the complexity when the Co/Dec signal is a constant.

And if the unit's function alternates, the X/Y/C/D registers should be placed outside, such that the controlling FSM can select the appropriate values for each cycle.

The last detail to check is the D value that might have to be XORed depending on the function. It still has to be tested. Stay tuned.

-------------

Rebuilding the test suite already shows the trouble that the immediate availability of SumX creates : it skips a step at the encoding stage. This shifts the timing : Data_out must be sampled before sending the clock pulse. I added a one-clock delay in the wrapper but I'll change the testbench's behaviour...

The mark's half adder is another head-scratcher, with its value shifted to the next cycle. It seems now that it's better in the same logical layer, even though it could increase the critical datapath's length a little bit.

So this is the new diagram:

The C/D/X/Y registers are now taken outside and must be managed by a suitable wrapper.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.