One way to strengthen the protocol for the control words, as mentioned in the last log 53. The last parity, is to implement a "sequence" for the control words. Since it is expected that the C/D bit will be altered, the goal is to reduce the damage when it happens, with the help of a counter.

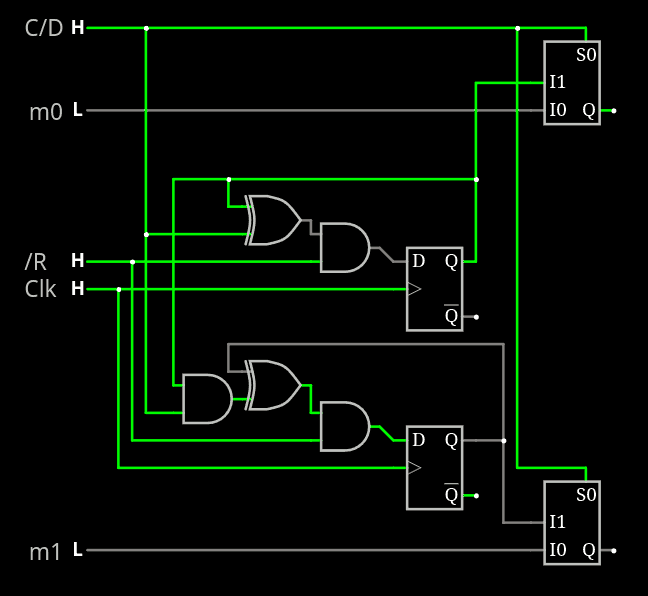

The mark bits m0/m1 are repurposed as a 2-bit counter, such that one, two or three consecutive errors will be caught right away. It reuses the comparator and adds the counter and a MUX to multiplex with the PEAC's carry outputs.

The counter is reset anytime the FSM sends a "burst" word that resyncs the PLL at the same time.

The circuit is pretty simple, as tried on CircuitJS:

Now, any D->C alteration can be detected immediately with 75% chances, on top of the parity (now 87% overall), as well as when any subsequent control word is transmitted. This more than supplements the job of the (single, lonely) parity bit.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.