Looking back at the whole Add/Sub duo's mysteries.

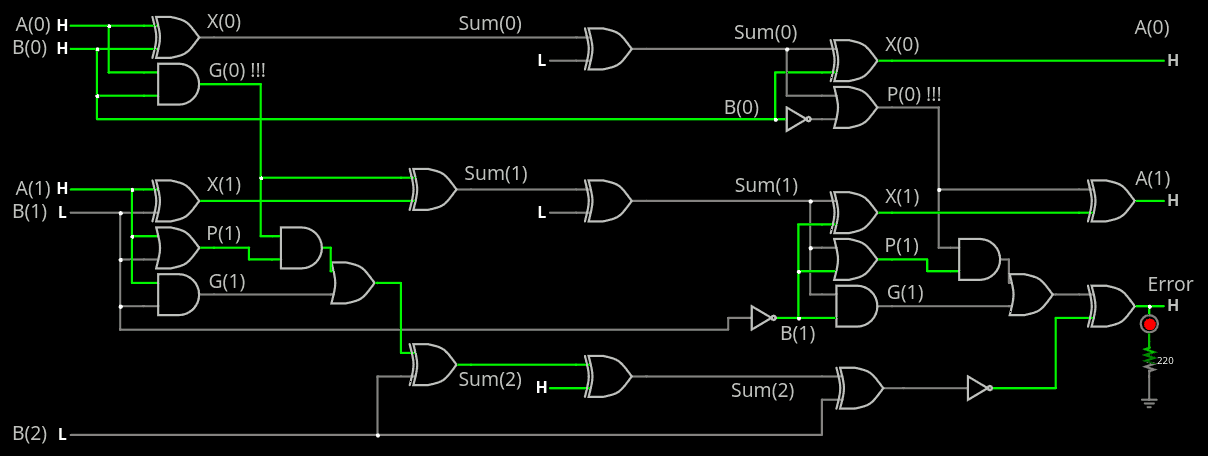

I reconstructed the whole circuit and realised a first thing : Add3 is not Sub3, as a Generate turns into Propagate : G(0) => P(0).

I annotated the concerned gates:

Turning Add3 into Sub3 is not just a copy-paste-addInverters operation.

Another important detail: B(2) is more resilient simply because it is one XOR away (only) from the error flag. Which means there is no point in trying to make the others more resilient, though S(1) is more susceptible than S(0) which is "further away". Go figure.

-------------------

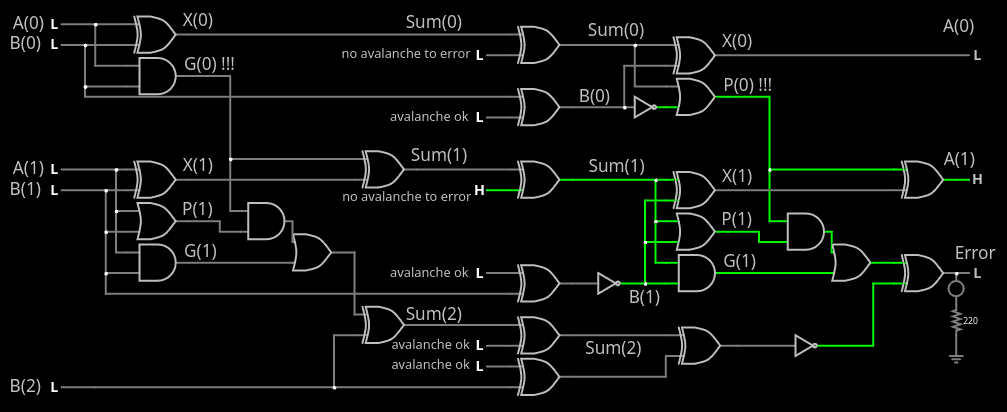

Adding more control inputs, I can explore the circuit deeper:

In the case of "single errors", there is a behaviour I hadn't seen yet, since I had only looked at alterations of S0/S1/S2:

- all changes of B (here, which corresponds to one Gray parity block) avalanche to the error flag

- OTOH only the S2 alterations trigger an error, while S0 and S1 do not.

(condition of test : all inputs A and B cleared...)

This is good because single-bit alterations of the main data block will trigger an error, meaning it's paradoxically more "protected" than the markers. WAT.

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.