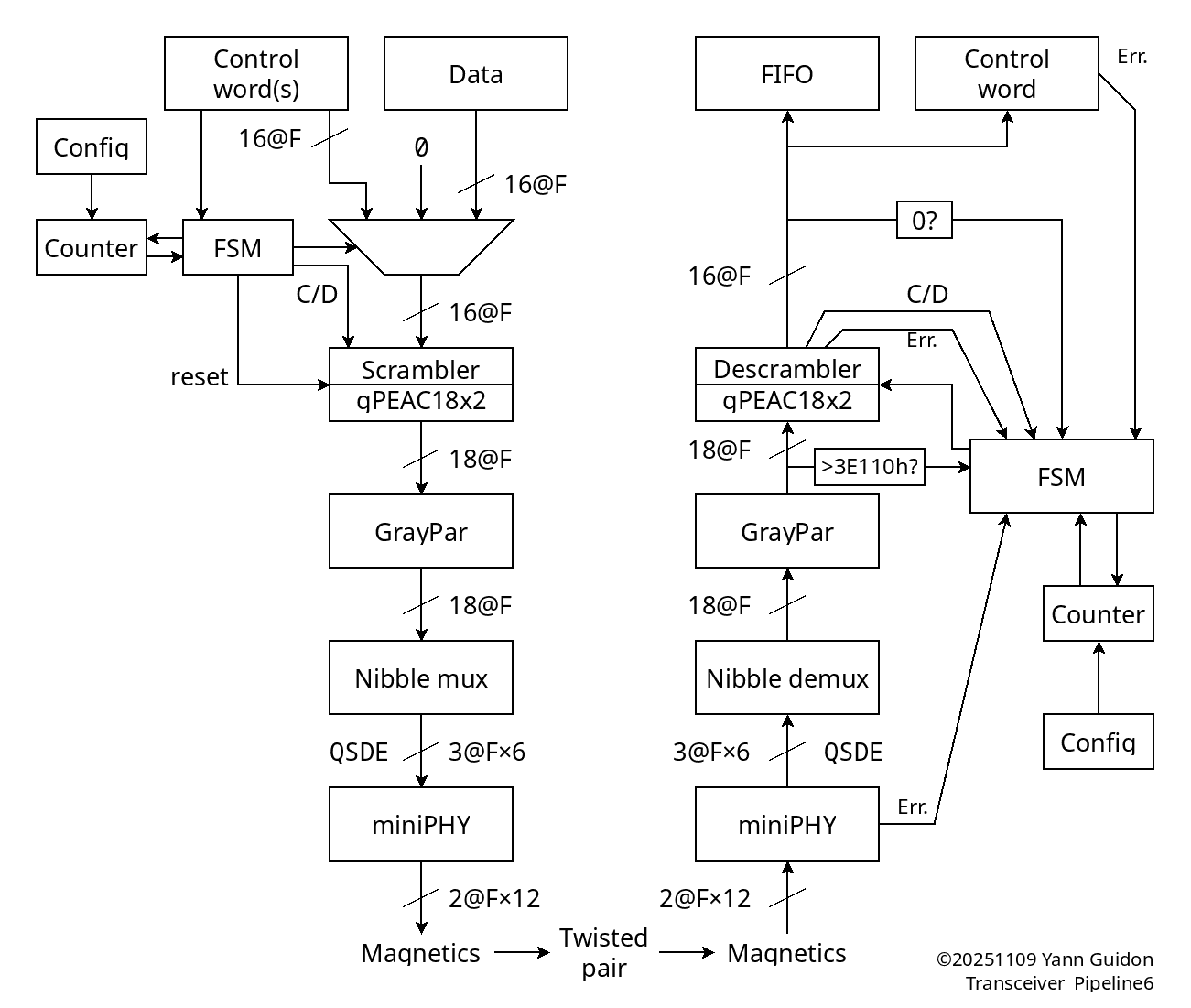

Version 6 of the transceiver pipeline is up on the main page:

There is the little addition of the post-GrayPar decoder, where the result is tested with the modulus. That's a small safety net but every percentage helps in the big picture. As stated in the previous log 96. Modular adder, it prevents invalid data from entering the gPEAC registers. It can also be run in parallel so the pretty long "carry chain" does not impact the clock frequency.

Log 34. PEAC treillis reminds that full error protection requires 2 "empty check words" so maybe the protocol should be extended by one empty word when C/D is toggled.

The current design opts for a separate gPEAC scrambler and descrambler, to keep scheduling simple. The emitter can work independently from the receiver. A singler-adder is chosen for bandwidths below 300Mbps if we can get a fast enough adder, but 4 cycles are now required for each word.

For a 100Mbps rate, each word is provided at 5.555MHz, so the 18-bit adder works at 22.222MHz. That's a 1/4.5 ratio instead of 1/9 but this really increases error detection.

The scrambler+Graypar+FSM+detectors around them form the "integrity layer". I imagine it could be recycled for other purposes, such as for onchip long-range communication or even inter-processor message passing, on a chip or a PCB. Data could then be sent as 9-bit or 18-bit parallel words without going through the nibble and miniPHY layers. A further transition minimisation can then be applied, for 7-bit wide words: each 18-bit GrayPar'ed word is cut into 3 sub-words, 6 bits each, and the popcount is easy and fast to compute. Then the result is time-differentially encoded (though the 7th bit keeps its toggle rate). That will be a log for later...

Yann Guidon / YGDES

Yann Guidon / YGDES

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.