Anacon-xC

Analog video console based on XMOS xCore with VGA/NTSC/PAL video output and PS/2 mouse/keyboard input. 32-bit scanline-based rendering.

Analog video console based on XMOS xCore with VGA/NTSC/PAL video output and PS/2 mouse/keyboard input. 32-bit scanline-based rendering.

To make the experience fit your profile, pick a username and tell us what interests you.

We found and based on your interests.

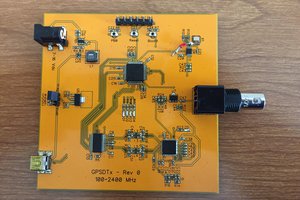

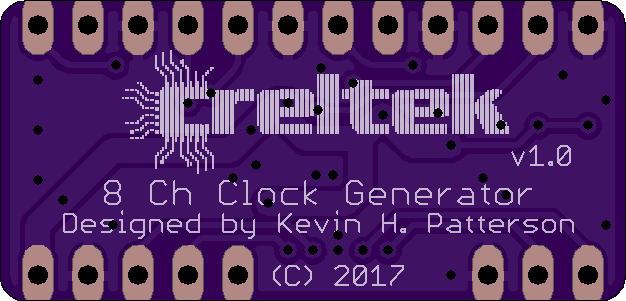

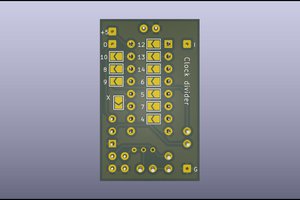

Creltek 8-Channel Clock Generator v1.0.zip8 Channel Clock Generator based on Silicon Labs Si5351A-B-GM. Eagle 7.5 files.Zip Archive - 52.93 kB - 03/10/2017 at 05:19 |

|

|

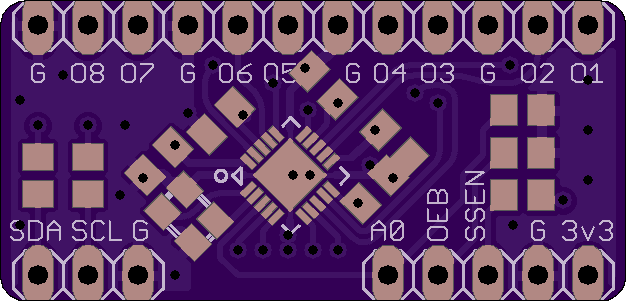

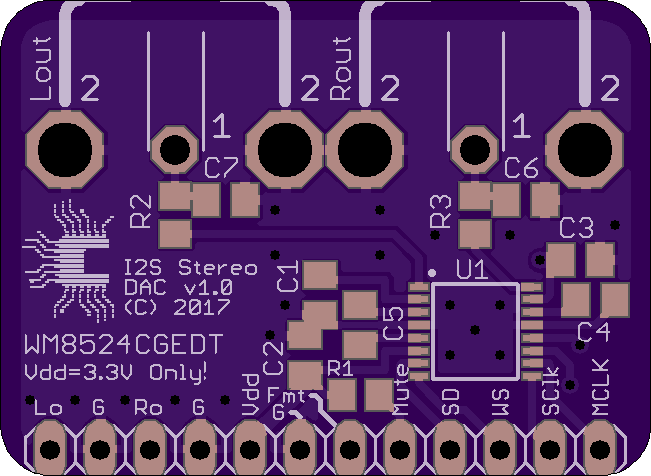

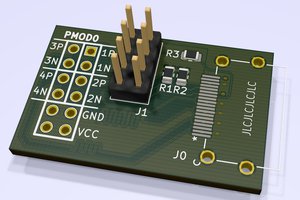

Creltek I2S Stereo Audio DAC v1.0.zipMini adapter board for Cirrus Logic WM8524CGEDT I2S Stereo Audio DAC. 24-bit, 106dB SNR. Eagle 7.5 Files. Dual RCA line-level outputs, which are also available on the pin header.Zip Archive - 68.23 kB - 03/06/2017 at 20:16 |

|

|

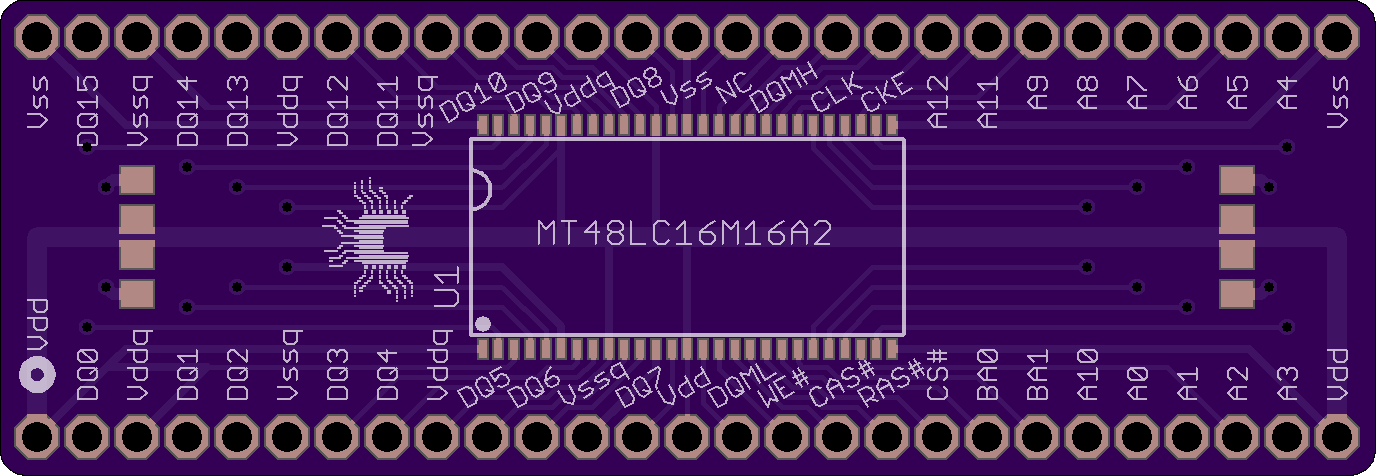

SDRAM TSOP54 Adapter v1.0.zipBreakout board for 54 pin TSOP SDRAM, suitable for MT48LC16M16A2. Eagle 7.5 Files. The header pads are designed to accept Mill-Max 311-93-164-41-001000 machined pin sockets, and allow them to seat deep in the board. The long pins on this model allow the adapter to be plugged into a solderless breadboard and still accept pins in the sockets on top. :)Zip Archive - 70.46 kB - 03/06/2017 at 04:33 |

|

The I2S Stereo DAC module is now available (pre-assembled) at Tindie.

Thinking about porting the Opus audio decoder... YEA, or NAY?

The I2S Stereo Audio DAC board based on Cirrus Logic/Wolfson WM8524 has been tested and functions perfectly. Yay!

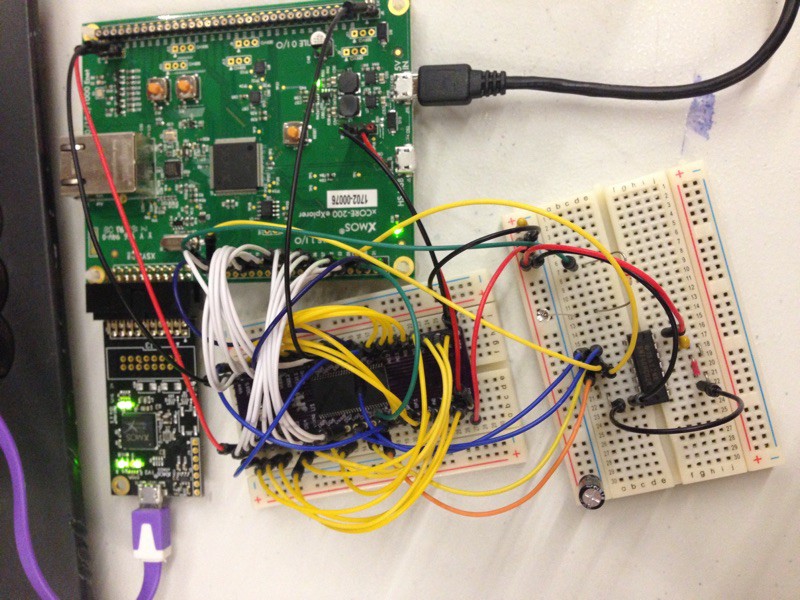

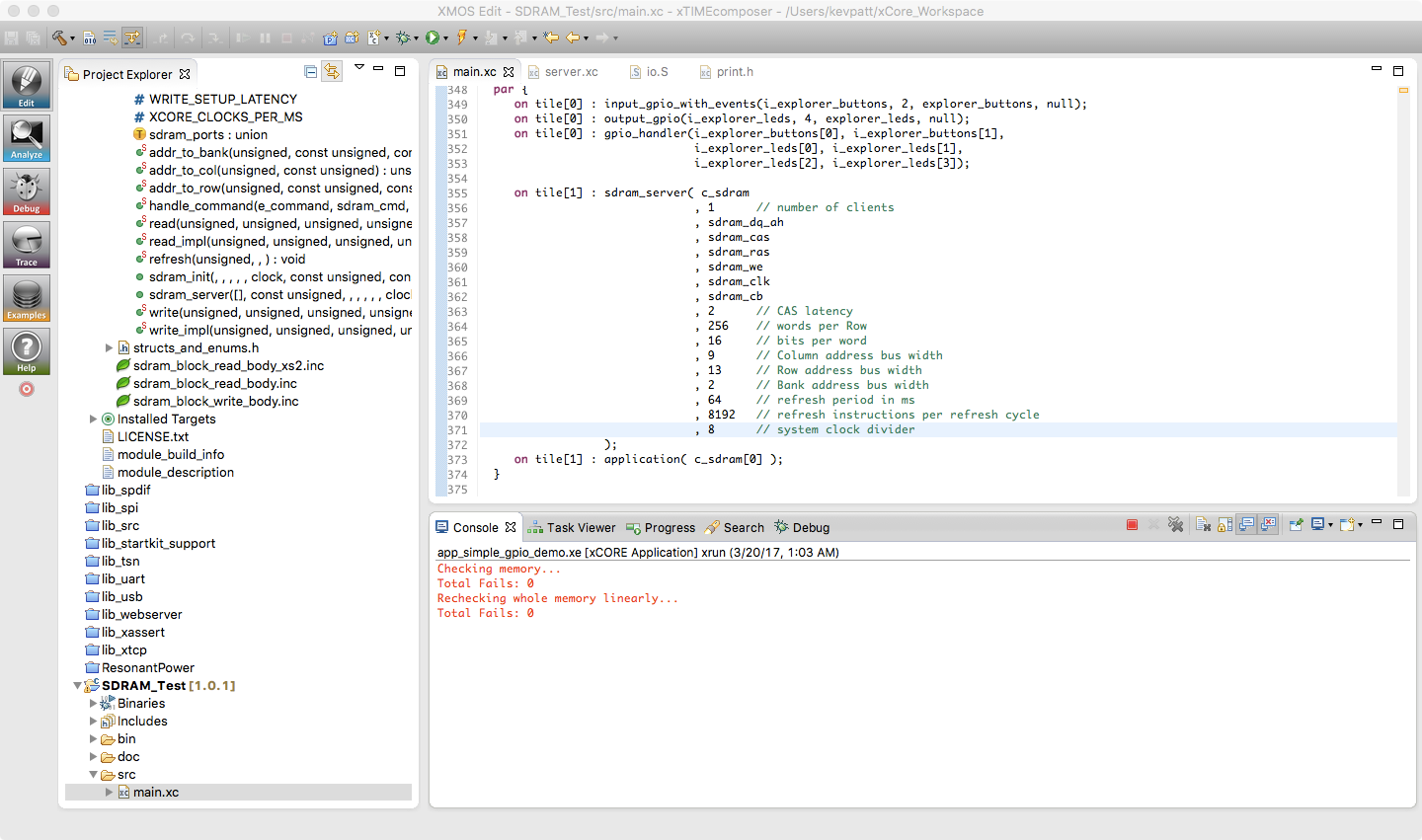

I tested it using my XCORE-200 explorerKIT and the lib_i2s 2.3.0 library in "i2s_frame_master" mode. Currently I'm running it using the following parameters:

Right now I'm just generating some nice sine waves at different frequencies, but the output looks (and sounds) very clean. Stereo separation is tested good as well.

Ported the Si5351 clock generator library from Adafruit today, and made a nice xC interface for it that links up with XMOS' lib_i2c. I can program arbitrary frequencies on all 3 outputs over i2c from the xCore mpu, no problem. I will publish this on git very soon, after a clean it up a bit more.

Right now I'm using the little 3-output board made by Adafruit, but I will be assembling one of my own 8-output boards soon to test as well. It should work fine with the existing code, and a few tweaks to enable outputs 4-8...

*YMMV

Spent several hours testing the SDRAM adapter board. Haven't had a chance to play with the I2S stereo DAC yet.

I did get the SDRAM to work with my XCORE-200 explorerKIT. However, it's definitely erratic. I'm able to write pseudorandom values to the entire 32 MB, and read them back successfully, but not 100% of the time, more like 90% of the time. My suspicion is that using a rats nest of jumper wires to a breadboard is not adequate with respect to the signal integrity required. But the library works, and I'm satisfied I know how to interface an SDRAM IC to the xCore.

Here are my thoughts on the "reliability" issues. Please note that I'm not complaining about XMOS :). I realize the pictured setup is a completely hacked-up arrangement that is probably way out of spec, and it's probably a miracle I got it to work at all. :P The following thoughts are here just for anyone who is curious or might have some ideas of their own to share.

Possible problems:

Oddly enough, I get pretty good results at certain clock dividers. I can run the pictured setup at div=8 (31.5 MHz), but no faster. HOWEVER, going slower (div=9, 10, etc.) doesn't seem to help! I even tried running at div=20 and 25, but everything slower is about 10-20% "reliable", compared to about 90% at div=8. I tried changing CAS to various numbers, no help. 2 works best at div=8, and 3 is marginally better at slower clocks... I also messed with "#define N (1)" in io.S, but changing it to 0 makes things almost totally unusable, even at very slow clocks (div=20, etc.).

Perhaps the most nagging issue is that I feel like I should be able to get this to work reliably at a slower speed (say 5 or 10 MHz). Perhaps there are some tweaks that I need to make to the library that I'm not aware of?

So, barring some miraculous insight that I'm yet to have, I'll probably end up designing a new (4-layer) board that incorporates both the SDRAM IC and an XMOS mcu on the same board, with impedance controlled traces, etc. Definitely a learning experience.

I've assembled the first copy of the I2S Stereo DAC and TSOP54 SDRAM Adapter boards. I plan to test them this weekend.

Got the clock generator board designed and ordered. This board is based on Silicon Labs Si5351A-B-GM, which can generate up to 8 independent channels of non-integer-related clock signals between 8 kHz and 160 MHz. They share a common clock domain too, so no relative drift between channels.

I plan to use this board to generate a variety of different clocks for the Anacon-xC project. This includes DAC pixel clock, I2S audio master clock and bit clock, NTSC/PAL encoder 4FSC clock, and in the future maybe even the XS-200 core clock as well (prob. 24 MHz).

For an example of how this would work: The xCore chip would send out a desired pixel clock frequency over I2C. The Si5351 would output this clock to both the video DAC and a 1-bit input on the xCore mcu. Falling edge of the clock would trigger the xCore to output 24-bit RGB data on a buffered port (using that input pin for clock), and the DAC would load the data on the rising edge. This makes it easy to select use any arbitrary pixel clock frequency, and take full advantage of xCore port buffering. Right now I'm burning a fair number of CPU cycles in the pixel output loop just doing the fractional division of the block clock to get an approximate desired pixel clock. Using an external clock allows us to program in a more "event driven" mode, where the external clock is an event, rather than generating all these events ourselves in code. Timers and port timestamps help a LOT, but when the clock frequencies are very high even a little overhead starts to add up.

The board includes all necessary support circuitry including the required crystal (25 or 27 MHz). All programming is done over I2C. Adafruit has an Arduino library for the 3-channel version of this chip which I can probably modify. Silicon Labs also has a little Windows app that can generate the right register values based on your choice of desired frequencies.

Board format is wide DIP style, and should fit nicely on a solderless breadboard. Although I only used 2 layers in the design, I took some care to route signals and power in a sane manner considering the potential frequencies involved.

Eagle 7.5 files for this board are available in the project files section.

Almost done designing an 8-channel clock generator based on Silicon Labs Si5351A-B-GM. This board will be in a wide DIP form that can plug into a solderless breadboard. Control is via I2C, and up to 8 independently programmable frequencies from 8 kHz to 160 MHz can be generated. (PLL is driven by an on-board crystal.)

Got a mini adapter board designed and ordered for the Cirrus Logic WM8524CGEDT I2S Stereo Audio DAC. 24-bit, 106dB SNR. Dual RCA line-level outputs, which are also available on the pin header.

BTW, this DAC runs directly on a single 3v3 supply. It has a built-in charge pump and bias servo to output true 2V line-level signals without using external coupling capacitors. This also eliminates the "pops" commonly encountered when these devices are powered on or off. Cool! :)

Eagle 7.5 files for this audio DAC board are available in the project files section.

Got an SDRAM breakout board ordered with OSH park today, so at some point I'll try out the SDRAM library (on XS-2, likely). I have an MT48LC16M16A2TG-6A:GTR (256 mbit, 16 bit ifx) to put on it. The "header" holes in this PCB are large because they are designed to allow "deep seating" of special machined socket strips with long pins that extend through the PCB. This allows the PCB to be plugged into a solderless breadboard as well as exposing a set of pin sockets on the top for connecting extra leads or components, allowing it to be used without the breadboard if desired. I'm using Mill-Max part number 311-93-164-41-001000.

Eagle 7.5 files for this breakout board are available in the project files section.

Create an account to leave a comment. Already have an account? Log In.

Become a member to follow this project and never miss any updates

Ken Yap

Ken Yap

kodera2t

kodera2t