-

Integrating AI into the hardware workflow

07/20/2025 at 15:13 • 1 commentLike the introduction said, AI can't do anything from within Altium or KiCAD. Perhaps if they ever develop an MCP server, it will be possible. Another possibility might be plugins that provide a create/move/route functionality.

As for right now, the typeCAD (or atopile) method of schematic-as-code is a promising approach to hardware design. It very clearly is a large jump from what is traditionally done, and there is 0 support for this from the major hardware providers, so gaining any traction will be difficult.

But I do think this small experiment showed that AI can do parts of the job. There were many ways to accomplish this particular task, and I was told by multiple LLMs several times, that the multi-IC approach was not the simplest way. I'll leave the results to the community to evaluate, though.

![]()

Some people will find this much more comfortable, others will hate it. More options are always better, though. Using code, all the typical tools become available: git, version control, and easy review. AI can deal with and understand it far better. This code will create an entire KiCAD project on each run, the PCB, and schematic, a BOM, run ERC, and write documentation. It can also do power analysis for you every time, much like a CI/CD pipeline might check a repo on every commit. There are plugins that will package the project for JLCPCB and run spice simulations.

From within VS Code, Cursor, or Kiro, you can take advantage of easy access to vast information. All the LLMs can search through all the information of a project, all the datasheets (with limitations), and come up with answers. You can simply ask it to find where in the datasheet it says x or y, or ask it to implement the entire reference design. Then, implement another IC's reference design and connect the two together.

-

Making the board

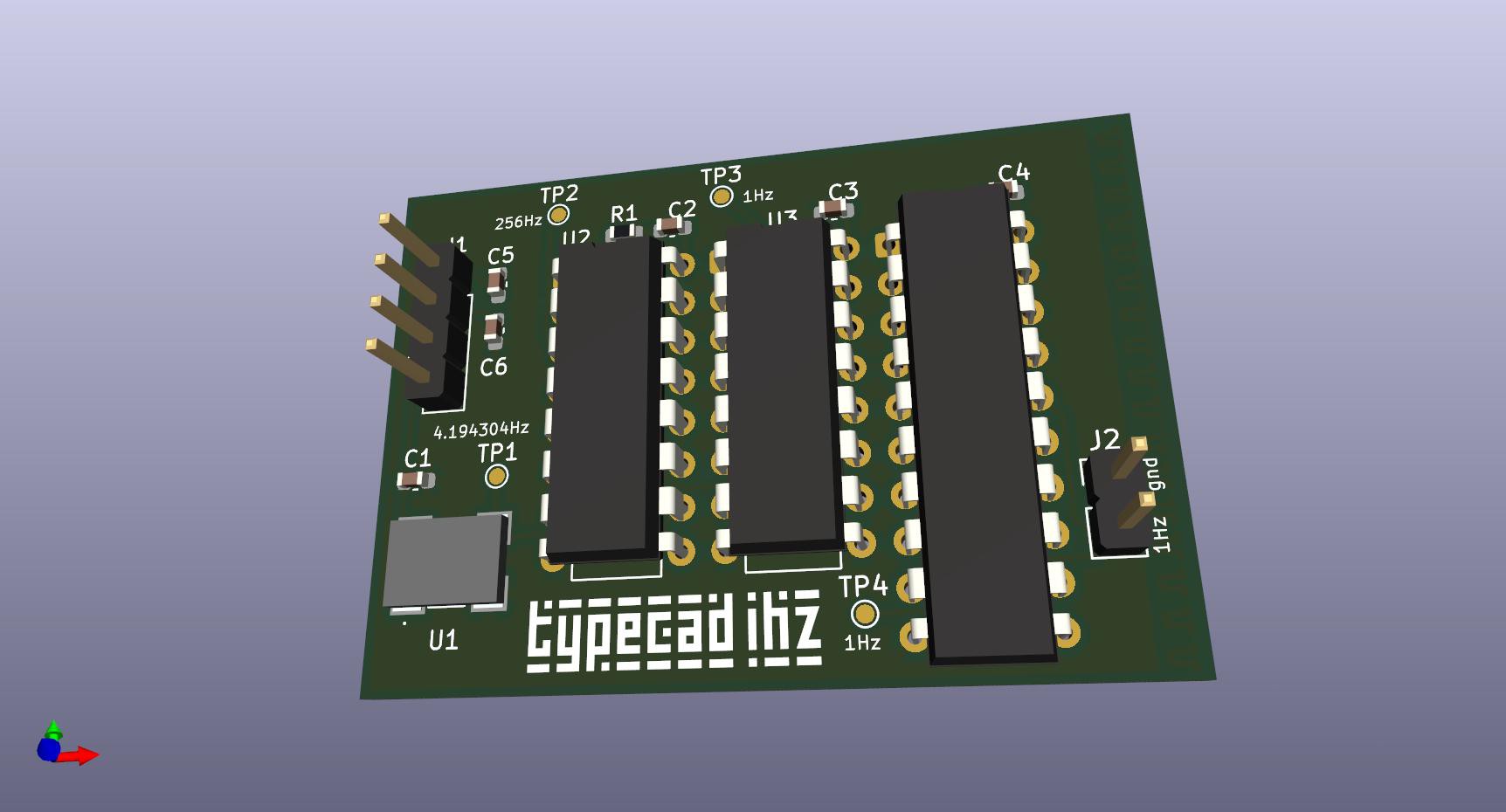

07/20/2025 at 14:42 • 0 commentstypeCAD code turned the components into a KiCAD PCB. All that was left to do was position the components and connect everything.

A couple of minutes later, and this is the result.

![]()

![]()

It could use some vias and maybe the traces could be routed better, but that's what it is for now.

-

But does it work?

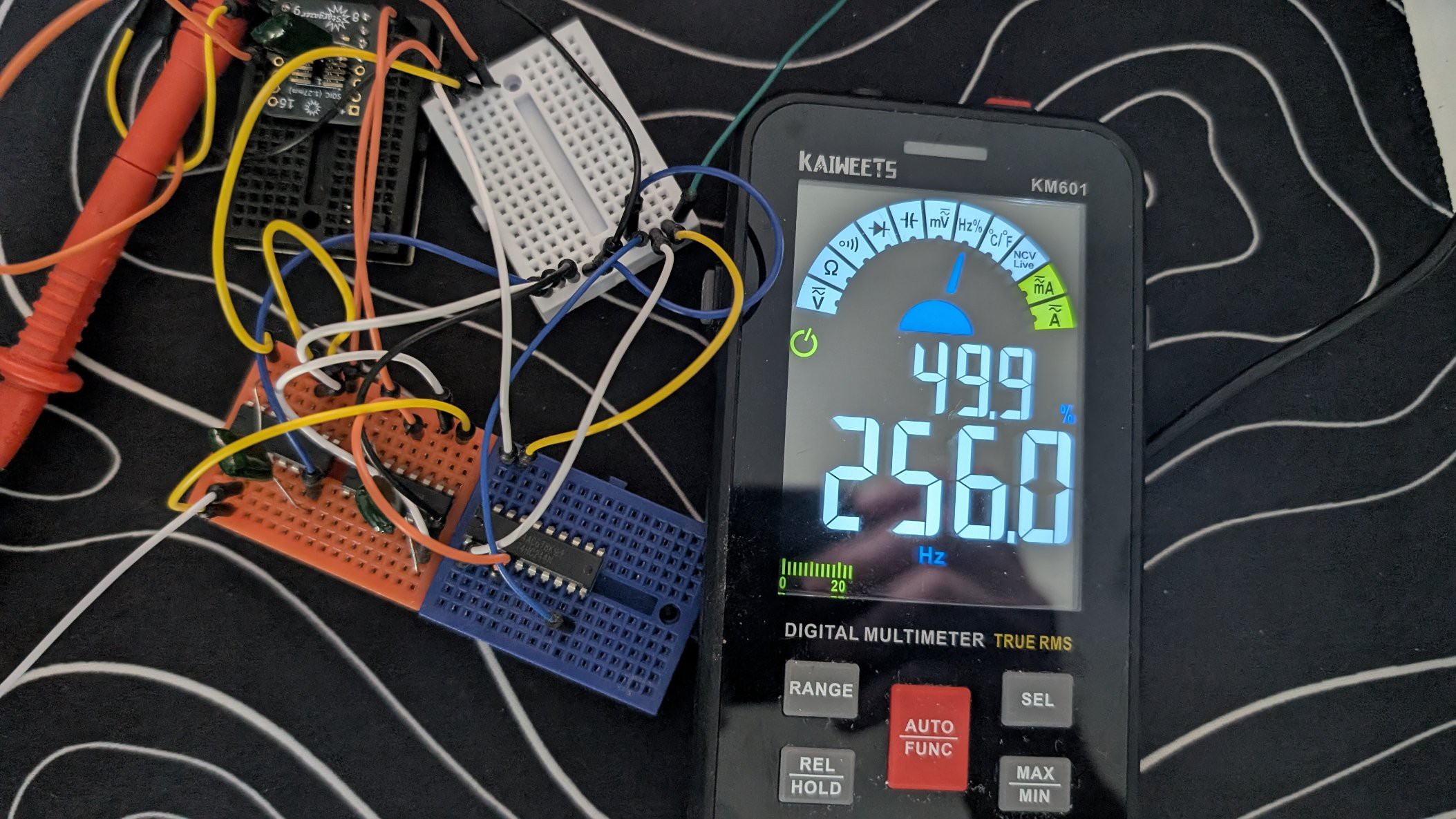

07/20/2025 at 14:31 • 0 commentsWhen the components arrived, I mounted the TCXO onto a breakout board and put it together on breadboards section-by-section.

TCXO 🡒 74HC4060N

![]()

After I remembered to pull up the RESET pin, it worked. My MM measured 256.00.

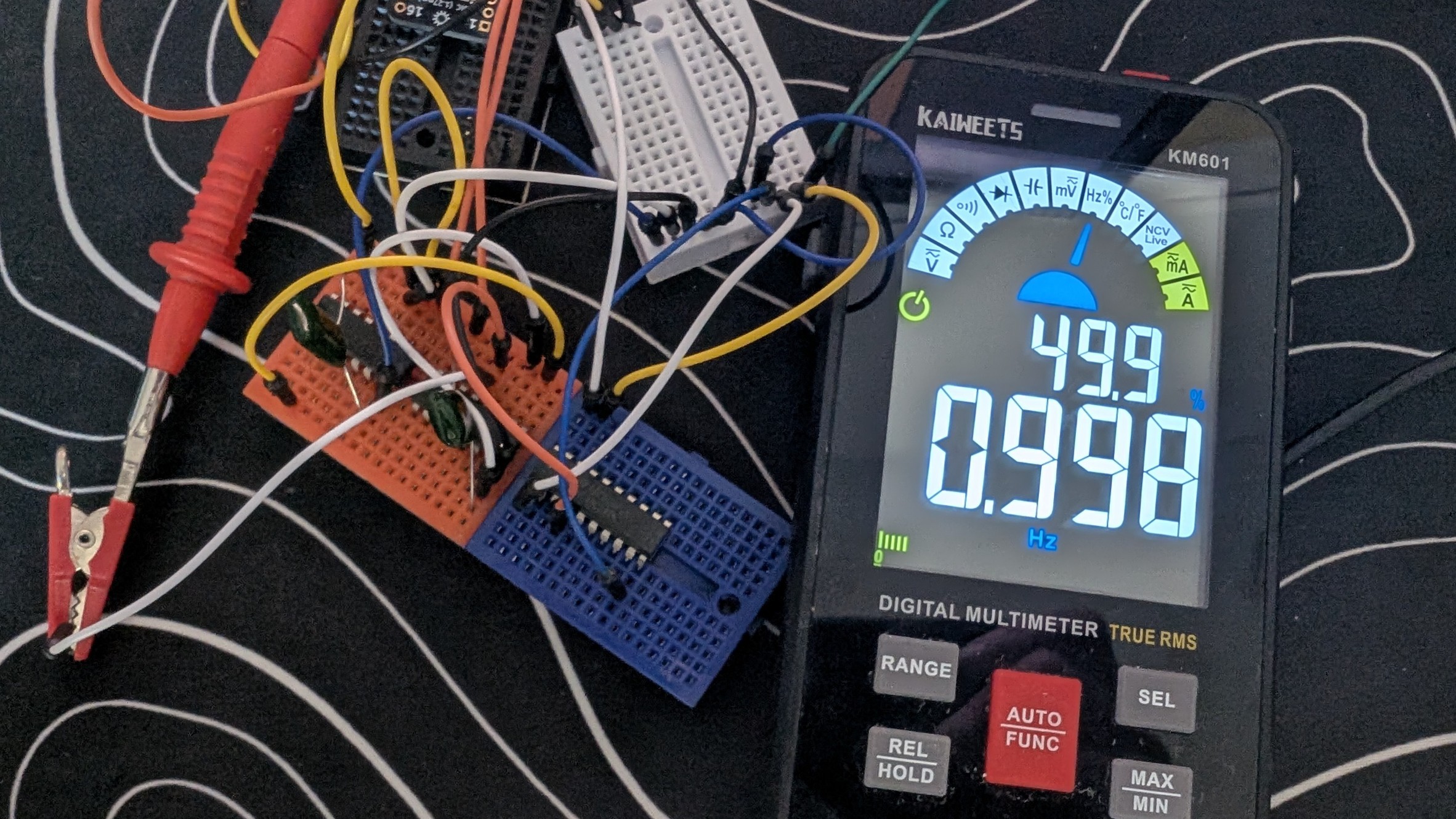

74HC4060N 🡒 74HC4040N

![]()

This one was confusing. The datasheet pinout doesn't match any of the symbols I could find. The typeCAD code also had issues with this. It provided the correct pin names, but not the correct pin numbers. After matching the typeCAD pin name to the datasheet name, I got the pin number and there I got 0.998 - 0.999 Hz.

74HC4040N 🡒 74HC244N

![]()

The same issues came up for this as well. The symbol was different than the datasheet. The typeCAD code had the correct pin names, so matching names to pins provided a nice driven 0.998 Hz signal that would light an LED.

Thoughts so far

At this point, it works. AI designed a 1 Hz blinking LED with very little input and guidance from me. The issues with the pin number vs pin names would have come up for me as well. The particular components that were used didn't seem to match the more common pinouts for these old components.

I did prompt the LLM 'validate U3 against [datasheet]' using the newly developed typeCAD MCP Server. Since LLMs can't read PDF files, it needs to be converted to text and that process doesn't result in easily understandable text:

- tables don't retain their lines or other formatting

- pictures are not extracted and 'viewed' by the LLM

- datasheets don't always have text that explains the pins names/numbers/functions

All of the above combined can make for some less-than-useful datasheets in terms of being understandable by LLMs. This is a great route to go down for future MCP server improvements though.

-

Making the circuit

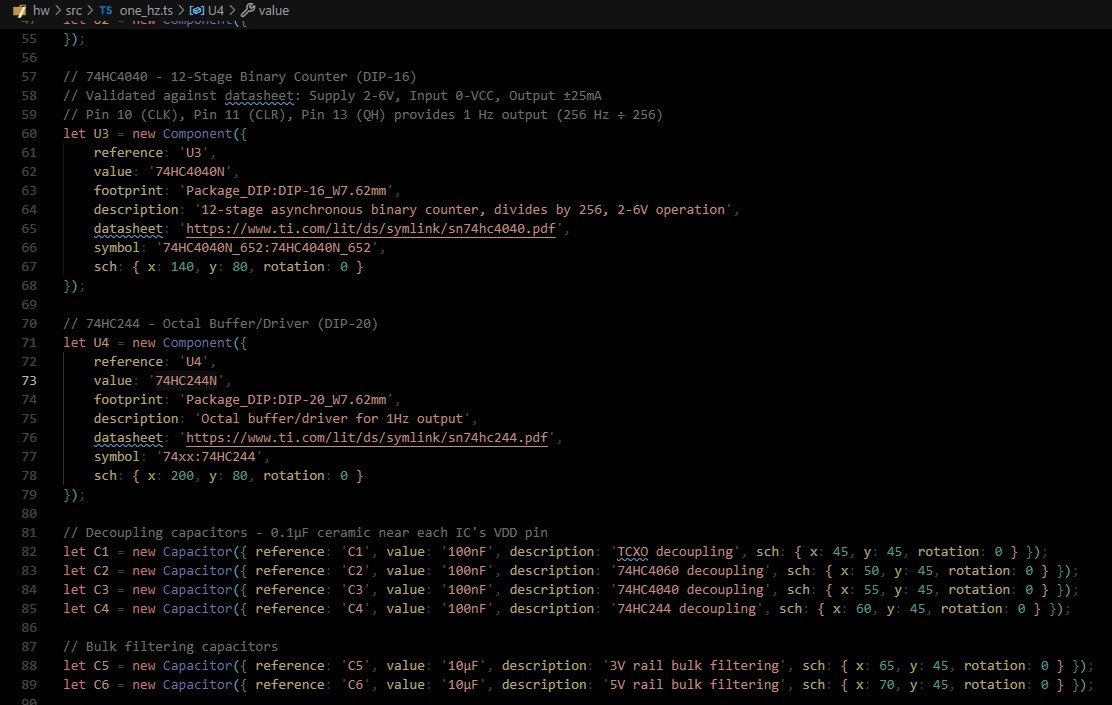

07/04/2025 at 18:32 • 0 commentsI copied the circuit description into Cursor and used Claude Sonnet 4.0 with the following prompt.

Create a typecad circuit according to the following description. Use @typecad.json @website.json for reference.

[circuit summary from last post]

I'll create a new TypeCAD circuit file for the 1Hz pulse generator based on your description. Let me first examine the existing files to understand the structure and then create the new circuit.

Read typecad.json and website.json

Now I'll create the new 1Hz pulse generator circuit file based on the description provided. I'll create a comprehensive circuit that implements the exact specifications:

one_hz_pulse_generator.ts+219•9

Now I need to fix the Testpoint components by removing the unsupported description property:

one_hz_pulse_generator.ts+7-7

[working...]

Perfect! I've successfully created a new TypeCAD circuit file one_hz_pulse_generator.ts that implements the complete 1Hz pulse generator according to your specifications. Here's what the circuit includes:

Key Features Implemented:

Components:

- TCXO (U1): SIT8008BI-82-30E-4.194304 (±25ppm, 3V supply)

- 74HC4060 (U2): 14-stage binary counter (DIP-16) - divides by 16,384

- 74HC4040 (U3): 12-stage binary counter (DIP-16) - divides by 256

- 74HC244 (U4): Octal buffer/driver (DIP-20) - buffers 1Hz output

- Connectors: Power input (4-pin) and 1Hz output (2-pin)

- Testpoints: 7 testpoints for debugging and verification

- Passives: Decoupling capacitors and reset resistor

Power Supply:

- Dual power rails: 3V for TCXO, 5V for logic ICs

- Proper decoupling: 0.1µF ceramic capacitors near each IC

- Bulk filtering: 10µF electrolytic capacitors for each rail

Frequency Division Chain:text Apply to one_hz.ts 4.194304 MHz → ÷16,384 → 256 Hz → ÷256 → 1 Hz

Connections:

- TCXO: Enable pin to +3V, output to 74HC4060 clock

- 74HC4060: Reset pins tied through 10kΩ resistor to GND

- 74HC4040: Reset pin to GND, clock from 74HC4060 Q14

- 74HC244: Enable pins configured, buffers 1Hz output

- Unused inputs: Properly tied to ground to prevent floating

Testpoints:

- TP1: TCXO Output (4.194304 MHz)

- TP2: 74HC4060 Q14 (256 Hz)

- TP3: 74HC4040 Q8 (1 Hz unbuffered)

- TP4: 74HC244 Output (1 Hz buffered)

- TP5: +5V Power Rail

- TP6: +3V Power Rail

- TP7: Ground Reference

The circuit follows all the critical wiring notes from your specification, including proper decoupling, reset strategy, unused input handling, and signal integrity considerations. The file is ready to be built and will generate a complete KiCAD netlist for the 1Hz pulse generator.

Claude guessed at the footprint for the TCXO. After that was fixed, the file built with no issues. I opened the generated kicad_pcb file, and the parts were there, ready to be placed and routed. I decided I didn't want all the test points; I didn't like the connectors it chose, but other than that, it appears to be correctly created. AI did the entire schematic portion of this project.

The typecad.json and website.json files referenced in the prompt are JSONified documentation to teach the LLM how to use typeCAD. They are attached to this project in the Files section.

Code Additions

I added additional code to create a schematic. I also added PCB layout information for the components. The vast majority of the code remained unchanged, and the additions were for extra features, not strictly required for a working PCB design.

-

The initial prompt

07/04/2025 at 15:32 • 0 commentsFor the initial prompt, Gemini 2.5 Deep Research was used.

Research ways to create a circuit that measures 1hz as accurately as possible. it should pulse every 1 second as accurately as possible. Provide a bill of materials, detailed pin connections, and accuracy calculations for a variety of circuits. Create UML/mermaid charts for the signal path/conditioning. Prioritize accuracy, then component count. Keep the cost around $30. Only use discrete components or TCXOs, no microcontrollers/FPGA or similar. A target for accuracy is ~500ppb.

After a few minutes, it presented a very long and detailed research paper. Skimming through the notes and thinking it left, it had a hard time working within the constraints given. Initially, it wanted to use a 32k crystal, but found it to be too inaccurate. It was able to search sites like Digikey and Mouser for potential components and none were found that would work at ~500ppb. It then switched to a TCXO method.

This way seemed to be a lot more workable. It quickly figured out that the chosen crystal frequency is a power of 2, and it can be easily divided down with binary math and discrete components.

To achieve a precise 1 Hz output through binary division, the TCXO's frequency should ideally be a power of 2. For example:

- 4.194304 MHz (2^22 Hz): This frequency divides perfectly to 1 Hz after 22 stages of binary division.

- 16.777216 MHz (2^24 Hz): This frequency requires 24 stages of binary division to reach 1 Hz.

High-speed CMOS (HC/HCT series) binary counters, such as the 74HC4060 (14-stage) or 74HC4020 (14-stage), are suitable for dividing these MHz frequencies due to their higher maximum clock frequencies compared to the older CD4000 series. Multiple counters can be cascaded to achieve the required total division ratio. For instance, to divide 2^24 Hz down to 1 Hz:

- A 74HC4060 (14-stage) can divide the 2^24 Hz input by 2^14, resulting in 2^10 Hz (1024 Hz).

- A second 74HC4020 (14-stage) can then divide the 1024 Hz input by 2^10 (using its Q10 output), yielding the final 1 Hz signal.

This approach seemed quite reasonable. After considerable part-searching, a 4.193404 MHz crystal, in stock, at a reasonable price was found. It wasn't nearly as accurate as Gemini had hoped for, ±25ppm, but that was the only available part. Other power-of-2 frequencies were just as difficult to locate (either due to availability or cost), so ±25ppm it is.

During this process, there was some back-and-forth. It was brought up that this whole thing could easily be done with a microcontroller or FPGA. Also that 1 hz oscillators do exist and could be used here.

The result

Eventually, this is what was decided on and planned.

1Hz Pulse Generator - Complete Wiring Diagram

4.194304 MHz→÷16,384→256 Hz→÷256→1 Hz

TCXO

4.194304 MHz ±25ppm

Pin Function Connection 1 Enable +3V 2 GND GND 3 Output → 74HC4060 Pin 10 4 VDD +3V 74HC4060 (DIP-16)

14-Stage Binary Counter

Pin Function Connection 1 Q12 N/C 2 Q13 N/C 3 Q14 → 74HC4040 Pin 10 4 Q6 N/C 5 Q5 N/C 6 Q7 N/C 7 Q4 N/C 8 VSS GND 9 OSC OUT N/C 10 OSC IN ← TCXO Pin 3 11 RESET GND (via 10kΩ) 12 RESET → Pin 11 13 Q1 N/C 14 Q2 N/C 15 Q3 N/C 16 VDD +5V 74HC4040 (DIP-16)

12-Stage Binary Counter

Pin Function Connection 1 Q8 → 74HC244 Pin 3 2 Q6 N/C 3 Q5 N/C 4 Q7 N/C 5 Q4 N/C 6 Q3 N/C 7 Q2 N/C 8 VSS GND 9 Q1 N/C 10 CLOCK ← 74HC4060 Pin 3 11 RESET GND 12 Q9 N/C 13 Q11 N/C 14 Q10 N/C 15 Q12 N/C 16 VDD +5V 74HC244 (DIP-20)

Octal Buffer/Driver

Pin Function Connection 1 1OE GND 2 1A1 GND 3 1A2 ← 74HC4040 Pin 1 4 1A3 GND 5 1A4 GND 6 1Y4 N/C 7 1Y3 N/C 8 1Y2 1Hz OUTPUT 9 1Y1 N/C 10 VSS GND 11 2Y1 N/C 12 2Y2 N/C 13 2Y3 N/C 14 2Y4 N/C 15 2A4 GND 16 2A3 GND 17 2A2 GND 18 2A1 GND 19 2OE +5V 20 VDD +5V Power Supply Connections

Rail Components Current +3V TCXO (Pins 1, 4) ~2mA +5V 74HC4060 (Pin 16) 74HC4040 (Pin 16) 74HC244 (Pin 20) 74HC244 (Pin 19) ~3mA GND All VSS pins All unused inputs Reset pins Return Recommended Test Points

- TP1: TCXO Output (Pin 3) - 4.194304 MHz

- TP2: 74HC4060 Q14 (Pin 3) - 256 Hz

- TP3: 74HC4040 Q8 (Pin 1) - 1 Hz unbuffered

- TP4: 74HC244 Output (Pin 8) - 1 Hz buffered

- TP5: +5V Power Rail

- TP6: +3V Power Rail

- TP7: Ground Reference

Critical Wiring Notes

- Dual Power Supply: Requires both 3V and 5V rails

- Decoupling: Place 0.1µF ceramic capacitor near each IC's VDD pin

- Reset Strategy: 74HC4060 reset pins tied together through 10kΩ resistor to GND

- Unused Inputs: All unused 74HC244 inputs tied to GND to prevent floating

- TCXO Enable: Pin 1 must be connected to +3V for continuous operation

- Signal Integrity: Keep clock traces short and direct

- Ground Plane: Use solid ground plane for digital circuits

Component Specifications

- TCXO: SIT8008BI-82-30E-4.194304 (±25ppm, 3V, SMD)

- Counters: 74HC4060N, 74HC4040N (DIP packages)

- Buffer: 74HC244N (DIP-20 package)

- Capacitors: 0.1µF ceramic (×4), 10µF electrolytic (×2)

- Resistor: 10kΩ (reset pull-down)

typeCAD 1Hz -AI designed hardware

Making a 1 hertz timer circuit with typeCAD and AI

typecad

typecad