"I still have the parts for your DDC118 booster pack, do you have any assembly instructions?"

"throw that old PCB away"

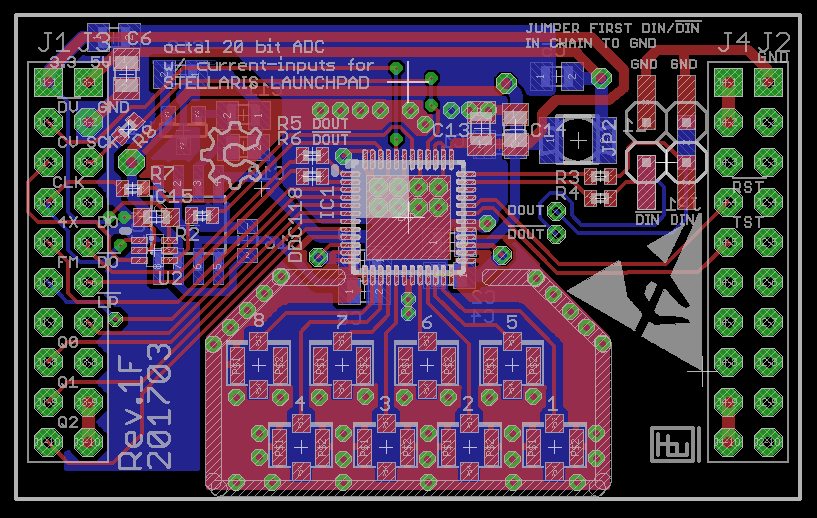

Here's the new one. Guess I'll find out tomorrow that those u.fl connectors are spaced too closely or that the diff pairs have a polarity twist somewhere.

new minor revision:

- has proper footprints for U.FL connectors. They feel right for the job, right now I don't care much about the added capacitance due to coaxial cable

- tidies up passives

- actually spells out the channel numbers at the connectors and signal names near the pin headers ;-)

- removes LDO

- introduces differential DIN / DOUT

- introduces series termination resistors

- has 2x1 receptacle and 2x2 pin header for stacked daisychaining (first board has GND jumpers, all except for the base board omit R5/R6 in favor of a pair of wires that re-route DOUT/!DOUT, last board is unmodified (not pretty, but I couldn't be bothered to go 4-layer at this point

- introduces NC7SZ175 SC70-6 single UHS D-type flipflop which synchronizes CONV transitions to CLK_4X rising edge within < 5ns as per requirement (ds: sub-10ns for best performance), since I don't want to ensure these stay synchronized no matter what the Timer/Counter configuration I'll sync it in hardware. Will have to investigate beating anyway (+/- 0.5 clock cycles = 200-250ns w.r.t. 100µs-10ms integration time...)

- not yet given up on shields

- short circuits at the corners to avoid power-up when board is in wrong orientation (avoids killing the expensive IC)

"todo":

- see if moving SPI clock (not in sync with converter) up past the REF3040 (U1) changed anything

- not too excited about those digital traces running across the reference buffer. DOUT/!DOUT now diff routed to cancel capacitively coupled possibly async (w.r.t. ADC clock) bitstream, async SPI clock trace relocated, rest of the signals are static

- build 2 new boards and use a full 16 pixel sensor. Oh boy...

____

edit: had a few hours of sleep, found mistakes and fixed them ;-)

helge

helge

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.