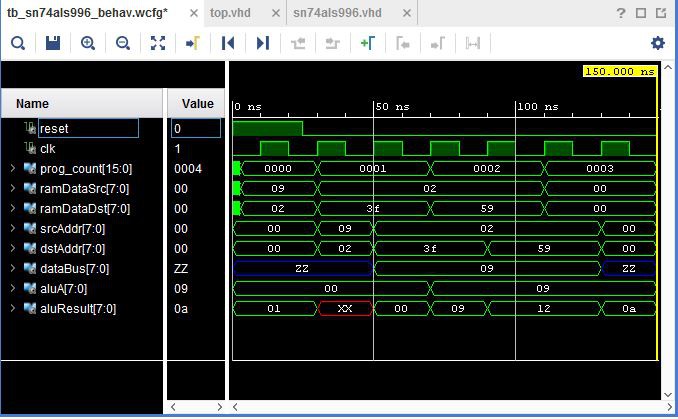

So I put together my RAM module in VHDL modeled after a generic SRAM. I was thinking of using an AS6C62256 from Alliance Memory. After a good bit of slugging it out with my VHDL code, I have a program counter connected to two RAM modules with registers on their outputs for the Source and Destination locations. I have a load register, ALU A register, and my ALU all hooked up to my data bus.

So I have my testbench loading a 3 line test code into the RAM which 1) writes a constant into the load register, 2) transfers from the load register into the ALU A register, and 3) adds the value in the ALU A register to the load register. And it works! (maybe a glitch or two still) It's a good start. I'm doing one-line VHDL address decoding for now, but I imagine I will eventually put them into EEPROMs. Next I'll finish the ALU output register and fix some glitches.

Discussions

Become a Hackaday.io Member

Create an account to leave a comment. Already have an account? Log In.

very nice !

Are you sure? yes | no