-

Cores Now In DesignLab Format

10/11/2015 at 21:46 • 0 commentsI've ported the Wishbone cores so they are compatible with the Papilio DesignLab IDE. They are currently located in my GitHub repository at https://github.com/joesugar/DesignLabSketchBook within the libraries subdirectory.

-

The Good And The Bad

09/26/2015 at 14:45 • 0 commentsSo I updated my Ubuntu distribution and now the ZAP IDE I used for Papilio development no longer works. The good news is it finally gave me the impetus to move to the DesignLab IDE.

Nice thing about DesignLab is that it integrates directly with the Xilinx tools and allows you to link the FPGA code and sketches into a single project. Bad thing is, now I have to go back and port all the Wishbone cores I've produced to this point to work with DesignLab.

There was a learning curve but I finally came up with a workflow that allows it to be done quickly and consistently. Now it's time to get it done.

This also means a change in the repository. I'll leave the old code in place for historical purposes but will be establishing a new repo to hold the cores as DesignLab libraries. This is a better way of doing it anyway since now they won't be tied to a specific build.

-

Finally, an update.

09/02/2015 at 00:21 • 0 commentsIt's been a while since I've updated this project. Not that I've forgotten about it, I've just had some trouble deciding on a direction for it.

The original idea was not to produce a specific product but to create VHDL blocks for signal processing and generation. But what good are the blocks without a project showing how to use them?

So now if you go the project repository you'll find the master branch and a number of development branches. The master is a fork of the ZPUino project and contains the blocks developed to date in the contributions directory. However, they are not integrated into the core. The development branches are dedicated to the individual blocks (or groups of blocks developed together), containing a project with integrated blocks and ZPUino sketches showing how they're used.

Blocks that have been integrated so far include:

WM8731 - A block used to read and write from a WM8731 audio coded, the same codec used on the Arduino audio codec shield. It includes integration of the OpenCores I2C block and an asynchronous FIFO used to go between the ZPUino and WM8731 clock domains.

PSK - A block used to produce a PSK31 audio signal. It includes a CORDIC block with supporting files and a numerically controlled oscillator (NCO). You can find more information on this block at https://ceworkbench.wordpress.com/2014/06/01/a-pks31-beacon-in-an-fpga/

-

WM8731 Control Block Completed

10/20/2014 at 23:57 • 0 commentsFinally got the vhdl block for controlling the WM8731 codec completed. Tested it by feeding audio into the A2D and looping it back to the D2A, and it sounds pretty good.

The code has been pushed to the repository. Time to start working on some transmit/receive hardware.

-

Playback on the WM8731

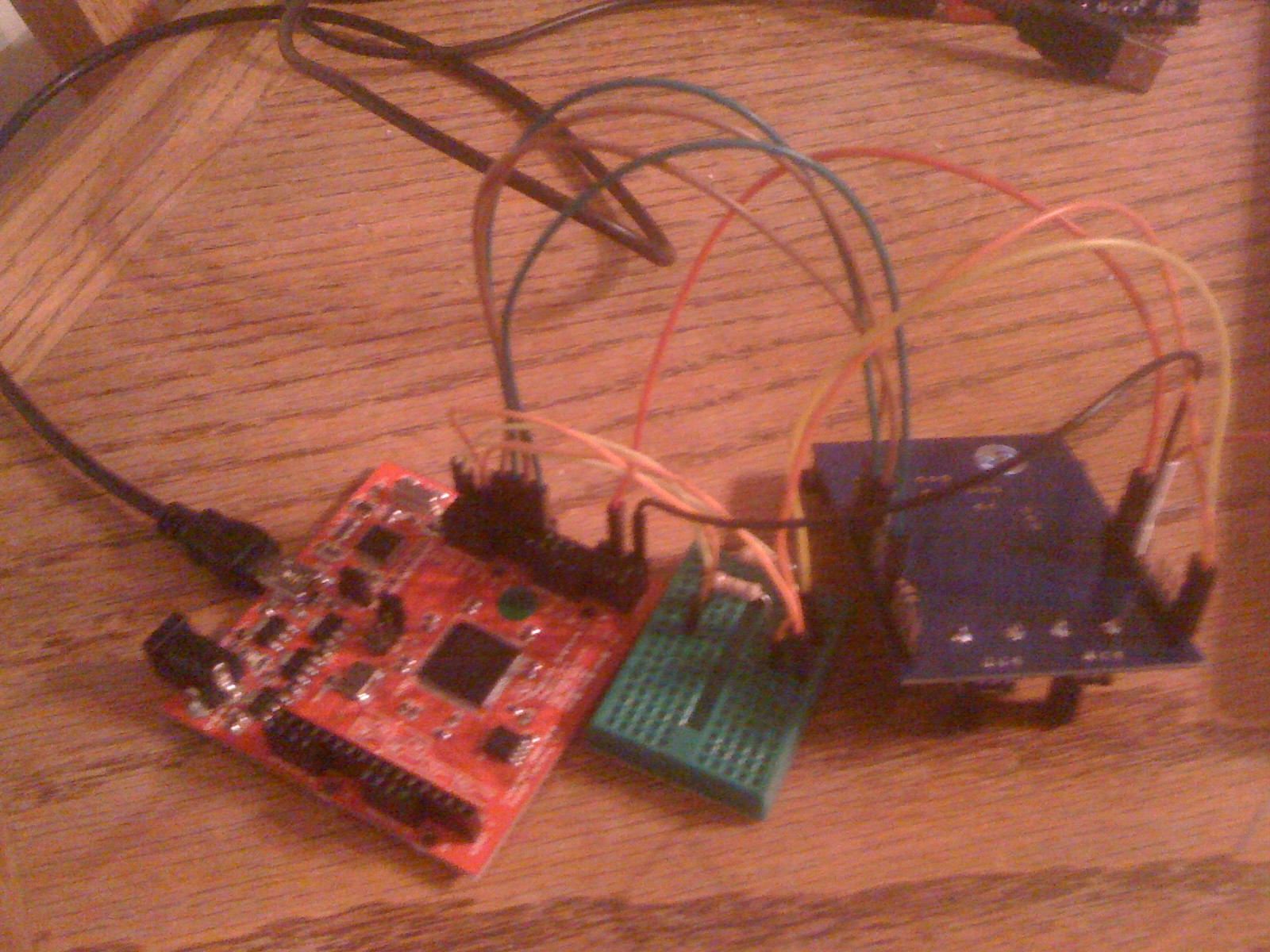

10/15/2014 at 22:57 • 0 commentsI finally got the blocks going for playback on the WM8731. Between getting the asynchronous FIFO and I2C blocks working and writing the Arduino code, it took longer than anticipated but hopefully I've learned from my mistakes and updating the WM8731 block to read the D2A will go faster.

Right now it's still a lot of wires and breadboard but I'm planning on pushing updates to the WM8731 block and an Arduino example sketch to the repository tonight.

-

Beginning to Integrate the WM8731 Codec

09/28/2014 at 01:09 • 0 commentsI've been working on a block to interface with the WM8731 audio codec. The protocol used to send data to the chip is straightforward but I ran into a problem I didn't anticipate. The codec board I'm using (an Arduino Audio Codec shield) has it's own oscillator and no easy way to synchronize it with the Papilio oscillator. This makes it difficult to create clocks with the proper timing to send data to the codec.

The solution I decided upon is to feed the CLKOUT signal from the WM8731 back to the Papilio and use it to create the sample and data clocks. However, this means the the audio data going between the Papilio to the WM8731 is crossing clock domains. The accepted solution to this is to use an asynchronous FIFO between the domains, so I've spent the last week getting one to work to my satisfaction. Now it's time to start working on actually sending data to the codec.

-

First Steps

09/19/2014 at 13:05 • 0 commentsI finally decided to start work using the ZPUino Hyperion variant for the LogicStart MegaWing to take advantage of the HQVGA driver. Also, there are other peripherals on that board I may take advantage of later (e.g., high-speed A2D) and Mike Field has made available a free book (Introducing the Spartan 3E FPGA and VHDL) for learning VHDL with the LogicStart MegaWing that can be used for reference.

I've integrated the I2C driver into the ZPUino code and pushed it up to the repository. There are a few idiosyncrasies to using it whose resolution I've described I2C for the ZPUino. Also, I had to make a couple of changes related to bus widths but nothing significant.

The next step is to start integrating an audio codec driver. I decided to use the Wolfson WM8731. This is the chip used in the Arduino Audio Coded shield so libraries exist to access it from an Arudio-like environment. Also, I've already run across some examples in vhd/verilog so I won't have to start completely from scratch.

-

Getting Started

09/15/2014 at 22:45 • 0 commentsI'm currently working on all the stuff needed to get the project off the mark, like gathering up files, setting up the repository, etc.

I'll try to provide or point to instructions for integrating the blocks and building the ZPUino project but this definitely won't be a configure; make; make install type of project.

A GitHub repository has been set up for the project at

https://github.com/joesugar/sdr_in_an_fpga.git

but it's empty now so give it a few days.

A fork of the original ZPUino project that will be used as the basis for this project can be found at

Software Defined Radio (SDR) In An FPGA

Building blocks for creating a software-defined radio (SDR) in an FPGA

joesugar

joesugar