-

Getting back to it.

04/24/2016 at 05:08 • 0 commentsI have been away for a while. In that time I have started using a different computer. I don't know how much is recoverable from the old one.

I now have the Altera and Xilinx platforms on my laptop.

I re-did some of the VHDL. I found that the character ROM is too larg to fit into the CPLD chip I am using (EPM240) so that will make the timing difficult.

Anyway I have been playing and here is a pic of the start of the TRS-80 screen layout. Each character cell is a different color -

![]()

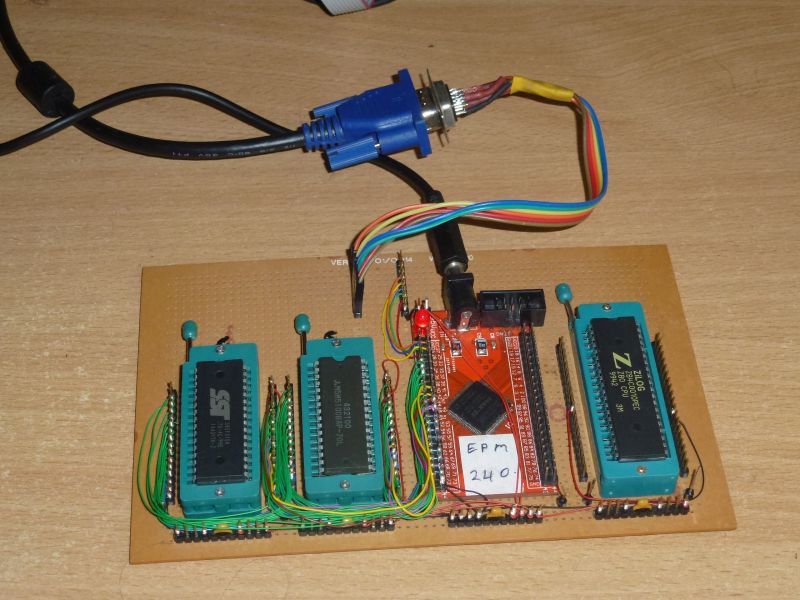

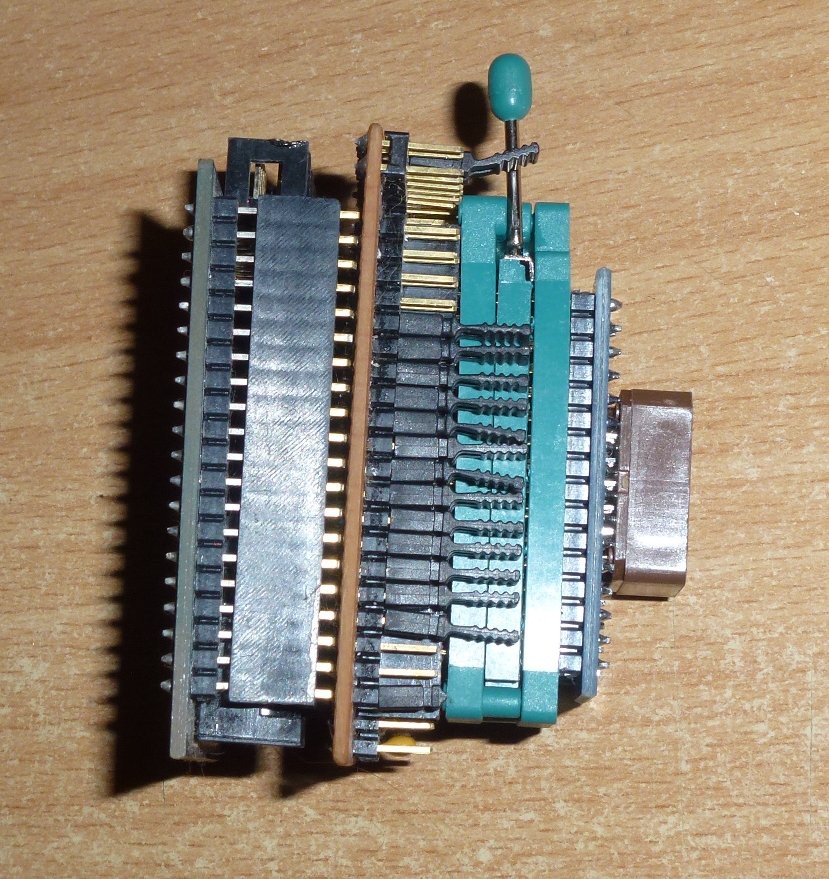

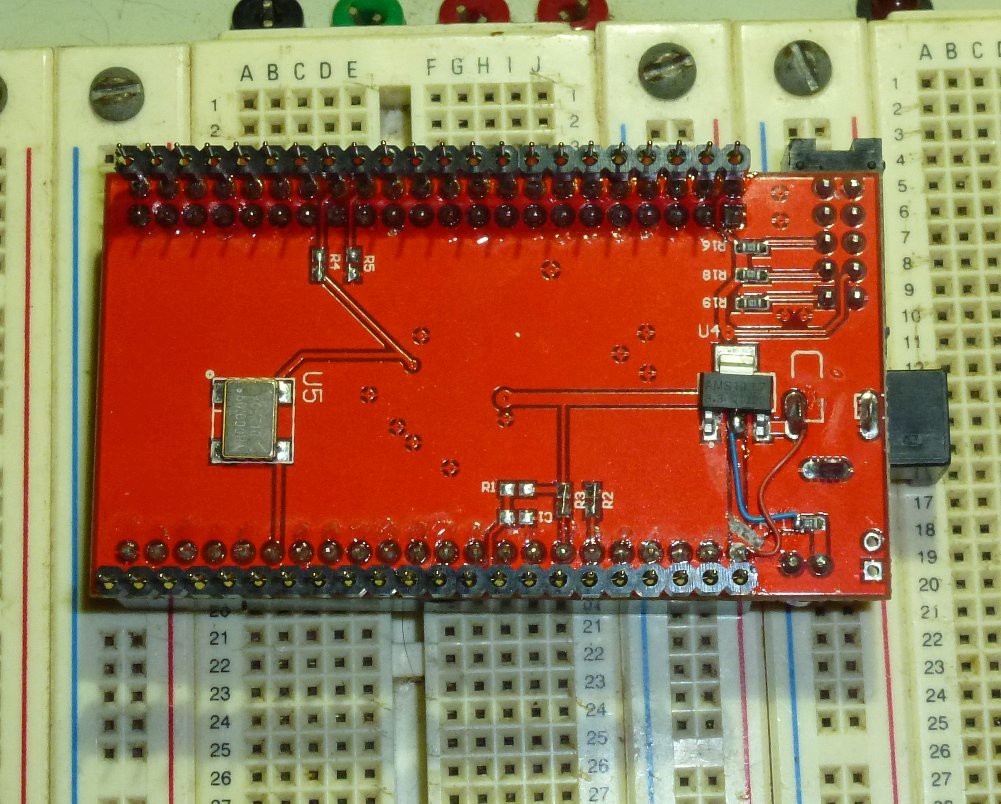

Here is what the development board looks like now - the Z80 isn't wired yet. I am actually using this for two projects as only the VHDL and ROMs are different.

![]()

I am considering switching to PCB modules (single sided with links on the other side) that plug into a backplane so I can do this stage by stage. Wire Wrap is so slow.

-

More timing problems

10/07/2015 at 06:13 • 0 commentsIt'll be easy they said!

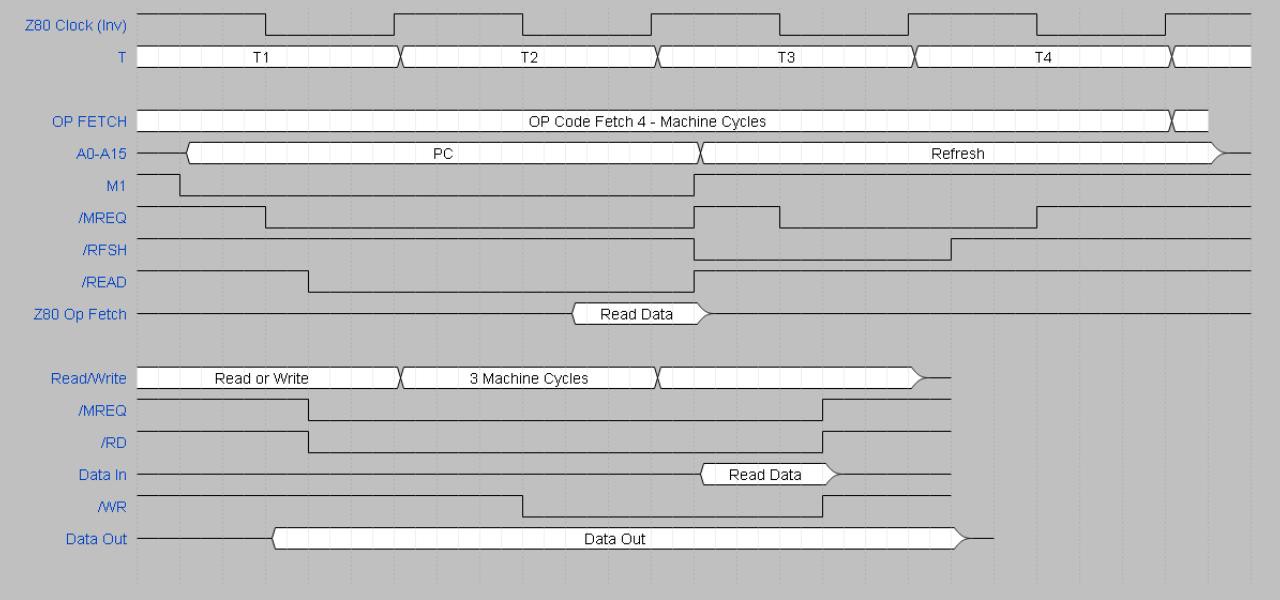

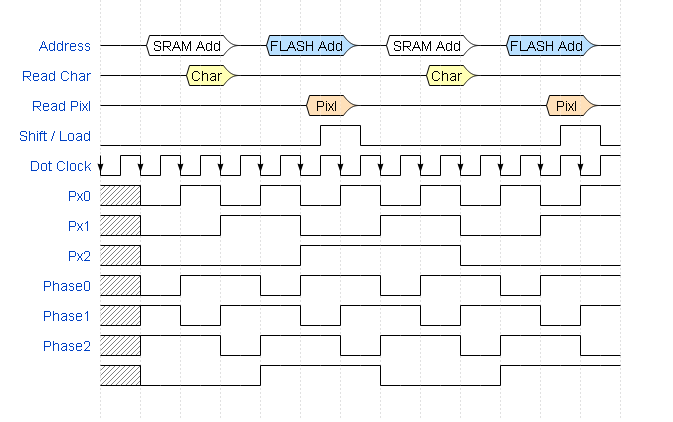

![]()

I spent many hours using WaveDrom as a visualising tool for the timing. At the end of this many hours, I decided to split the diagram into several parts. I discovered that the "Save As" function does not change the default file name so the original file is overwritten when you close WaveDrom!!! Much frustration. I lost everything except the above.

Anyway this CPU is *not* the easiest chip to bus time share with. As you can see from the Op-Code fetch above, it wants the Address bus just about all the time.

It also has two different SRAM Read timings, one for op-code fetch and another for normal access.

One other notable feature is the very wide data out write window.

There is also one other 'problem': I want to be able to write to the FLASH (ROM) from the CPU. I will mention what is a problem with that later.

Here's what I came up with and they're just thoughts now that I have lost the diagrams that I made.

Because of the two different read cycles and data in windows, I will buffer reads to a local register (in the CPLD) so the CPU can grab the data when it is ready. Even though the read data-in windows are completely different, the control signals /MREQ /RD start off almost exactly the same way. Each T cycle will be divided up into 3,4 or 6 sections and the read will happen the earliest and read later by the CPU when it is ready.

A Write (to RAM or FLASH) won't need buffering as the data out window is so long. There is one problem though. The write control window is longer than one T cycle. This means a second write to the same location may occur. If this were to happen then the CPU couldn't write to FLASH as it has 'write protection' that requires a specific sequence if write to effect one byte update.

So in total - there should be at least 4 time slots -

1) CPU Read - RAM or FLASH

2) Graphics Read - RAM (Character ASCII number)

3) Graphics READ - FLASH (Character Pixel map - one line)

4) CPU Write - RAM or FLASH

There will be 6 CPU T cycles to one screen character.

The screen dot clock will run at 25 MHz

The CPU clock will be 2.083 MHz

Now I have to make sub timing diagrams for these processes and then I can write it to HDL.

These timing windows won't actually fit together so I will also buffer the data for pixels and have it one character late so they transfer at the very start of the next T cycle. This will mean I have to adjust the Graphics timing to pre-compensate for this.

OK, next step is to go and redo and finish the timing diagrams that I lost.

One drawback that is likely from all of this is that each unit will most probably have to be programmed specificity for the video standard it uses: PAL, NTSC, VGA, because all of these standards are not going to fit in a CPLD together.

-

A Wire-Wrap test bed.

10/03/2015 at 05:54 • 0 commentsOK, this log will take a couple of days to get through.

I have work out the timing which is complex. The original TRS-80 had separate Character ROM and separate Video RAM.

I intend to use only one ROM (FLASH) chip and one (S)RAM chip. So the FLASH will have both the system ROM and the character pixels and needs to be accessed by both the video generator and the Z80. Like wise the RAM will have both the system RAM and the Video RAM and needs to be access but both the Z80 and Video generator.

To further complicate the matter the Video generator need to first access RAM to get the character number and then access the ROM to get the pixel arrangement that has to go to the screen.

And if that all isn't enough ... in the original TRS-80, the Z80 had access priority and this caused some screen flicker with video access. As this build will have only one RAM chip then this flicker would happen whenever ANY RAM is accessed ie not just Video RAM. On top of that the same would happen with conflicts of access to the ROM for both the CPU and the Video characters.

So I have to solve this by timing it out so that access to both RAM and ROM doesn't clash which will be hard to do with Video clocking out pixels at 25MHz (HSVGA) and a CPU running an irregular access pattern at a base clock about 2MHz.

For a test bed for this part of the project I have decided to go with Wire-Wrap after someone mentioned that Wire-Wrap will fit normal pin headers. I order a wire-wrap tool for about $35. I still had wire-wrap wire as I use that for repairing PCBs.

Finding wire-wrap sockets is too hard now and I have a lot of breakout boards that wont fit standard sockets anyway so I decide to use ZIF sockets as they're as cheap as wire-wrap sockets anyway.

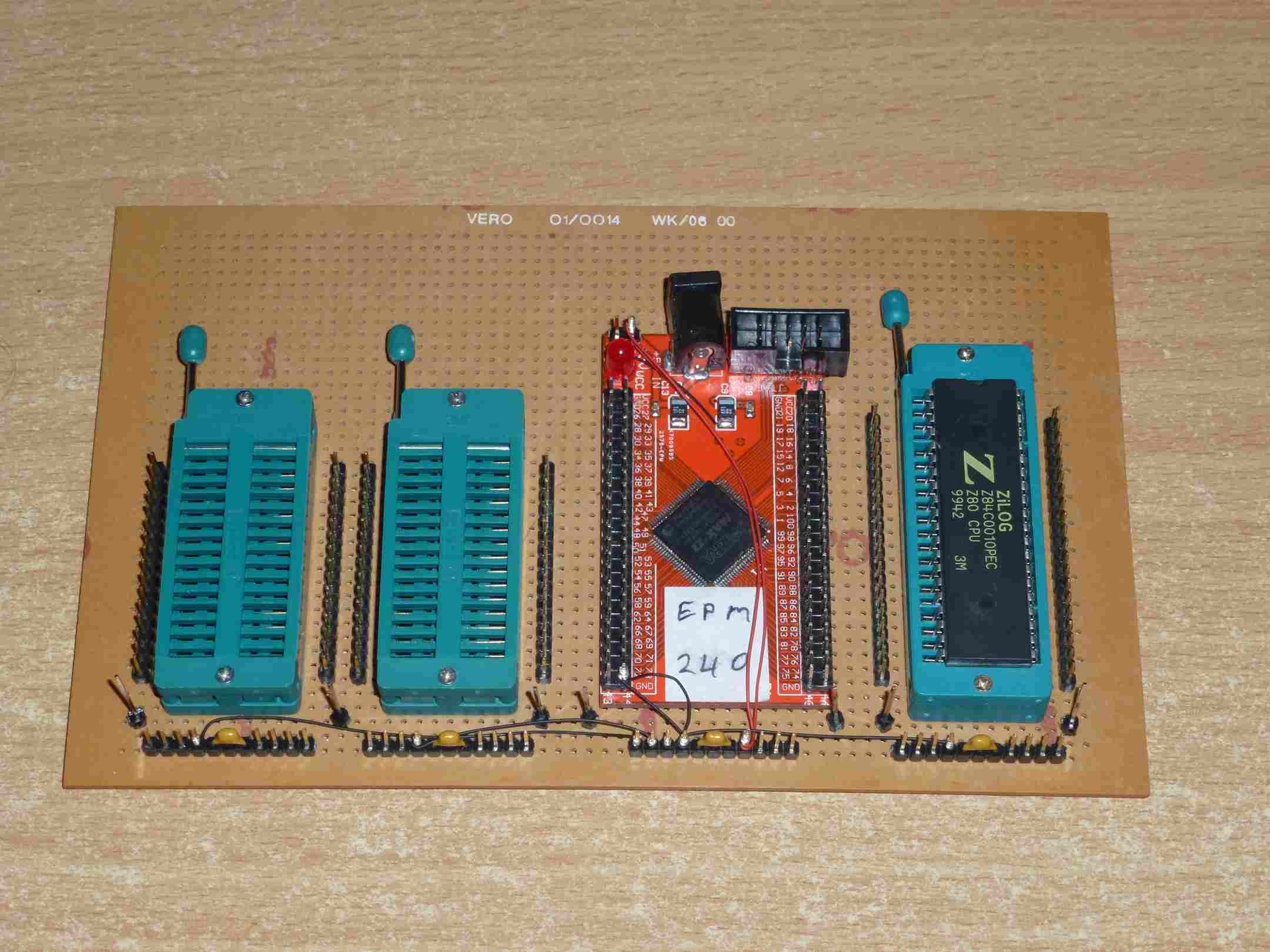

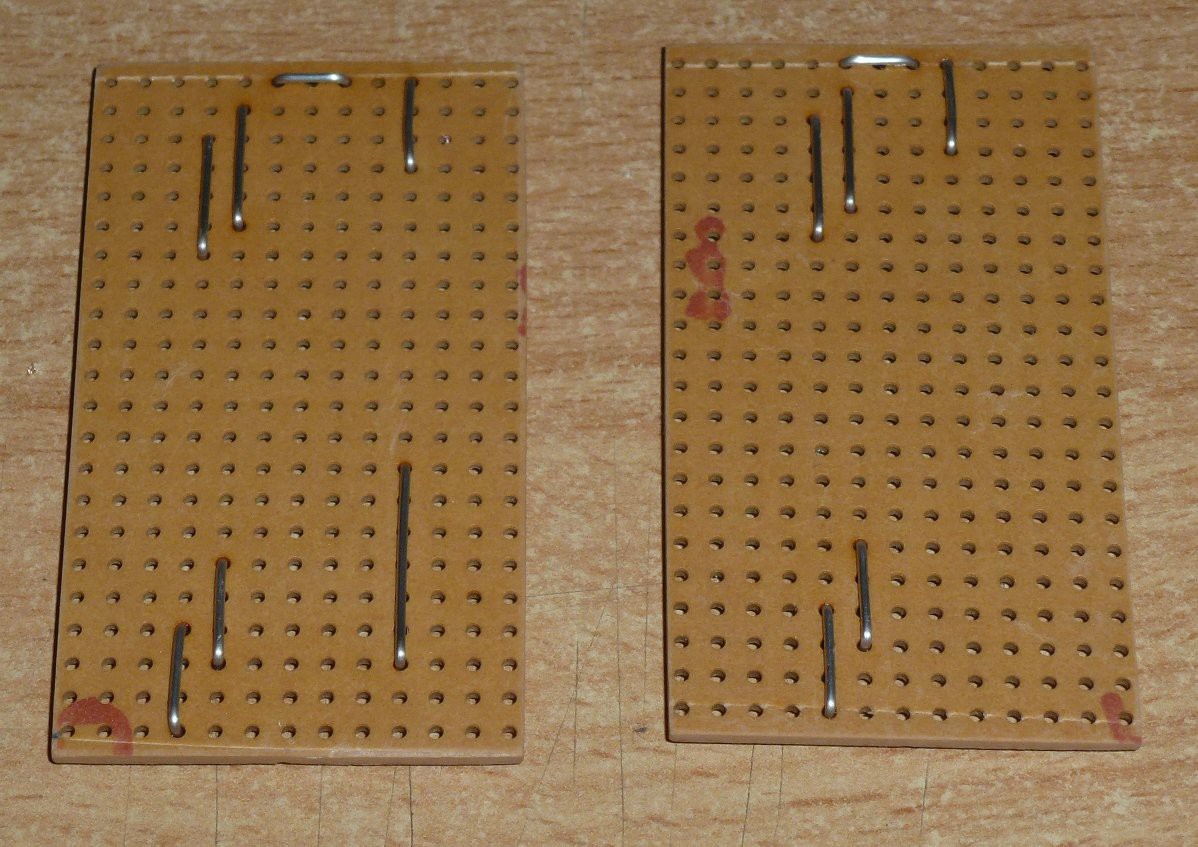

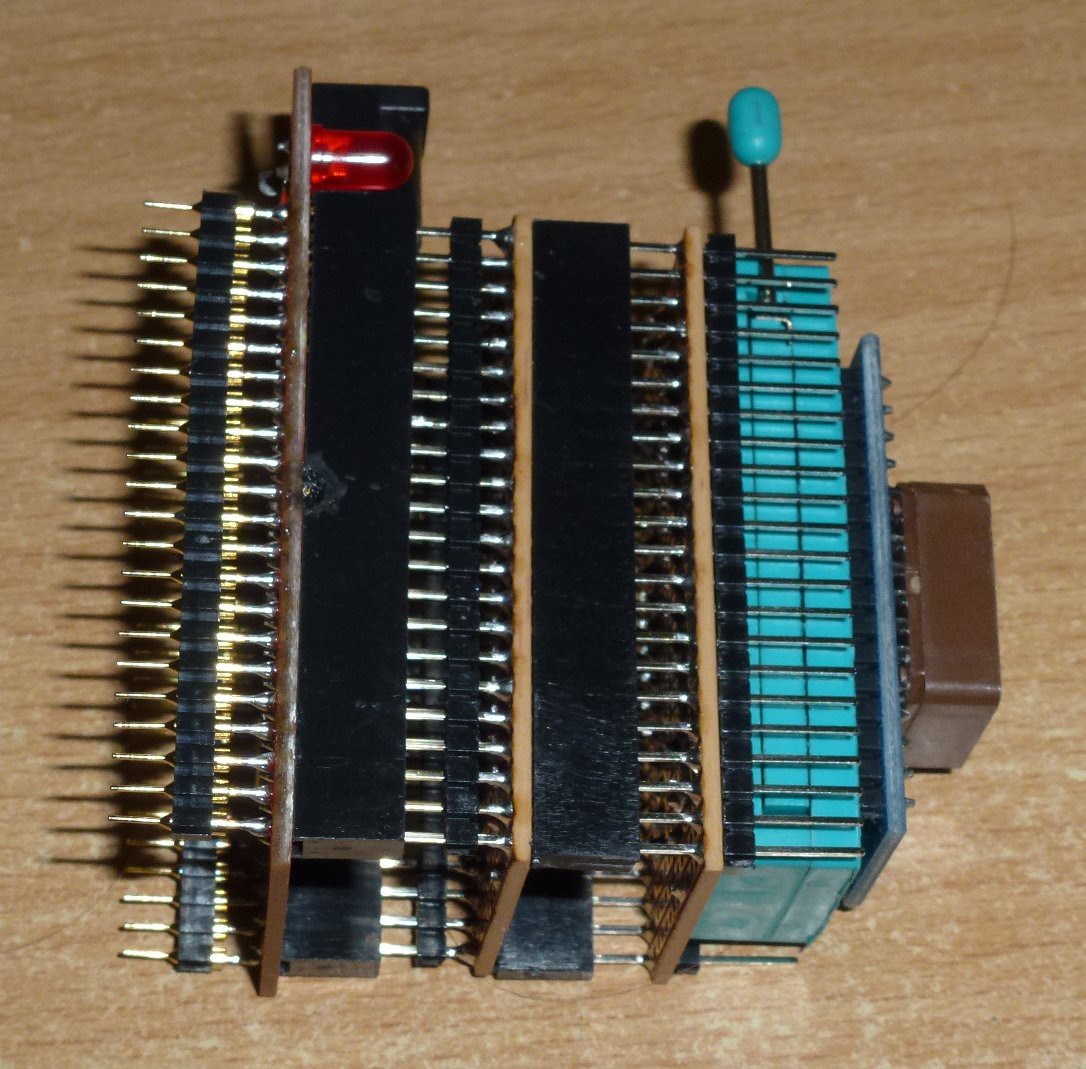

Here is what I have put together so far -

Top

![]()

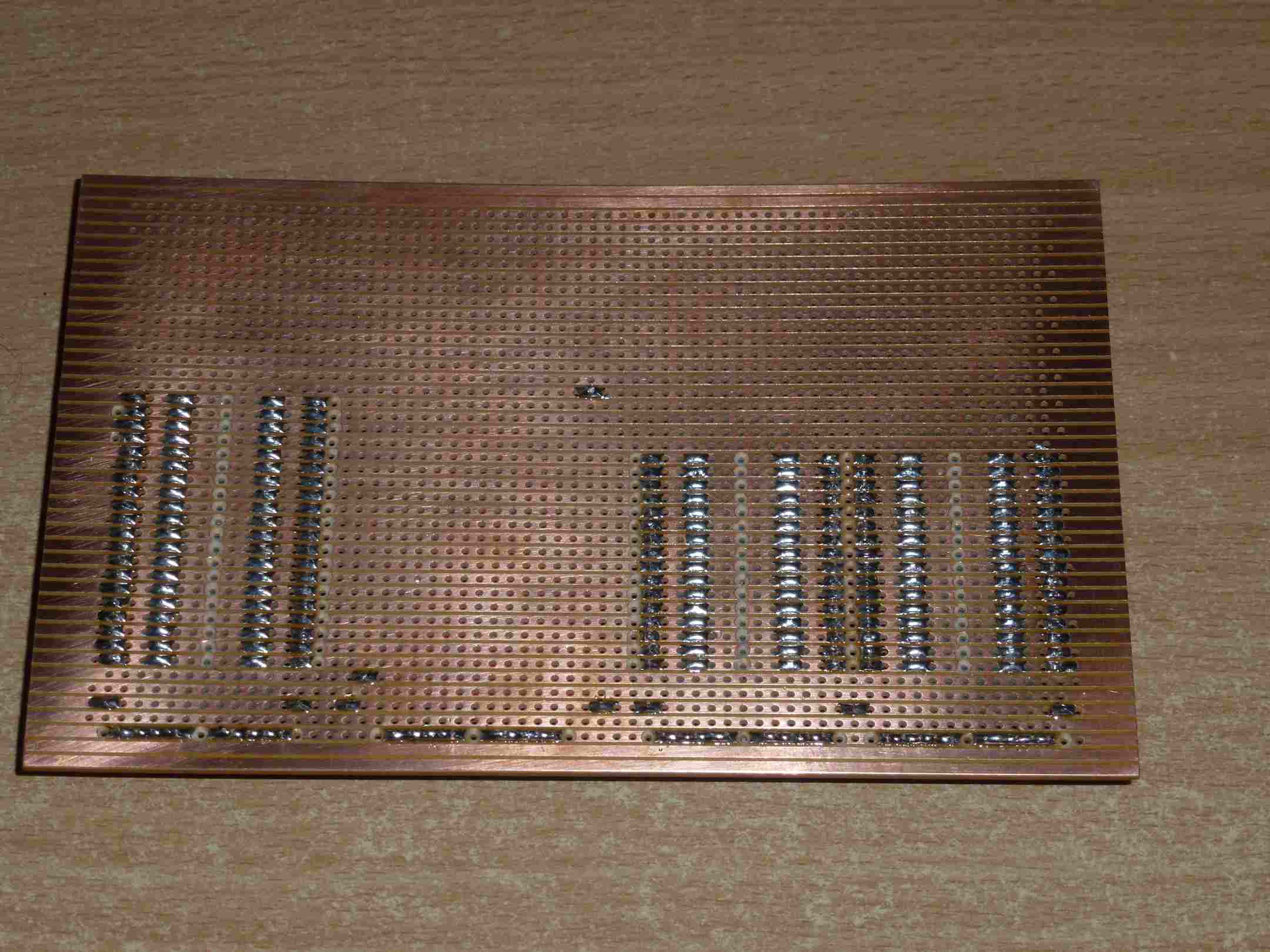

Bottom

![]()

I started some wire-wrapping and it seems to go ok.

The Z80 pictured is a fake from China (ebay) you can tell by the color and brightness of the printing on top. It marked as a 10MHz chip but it's probably just a Z80, Z80A or Z80B. It will probably work fine at ~ 2MHz.

I decided to use a EPM240 CPLD as it has enough logic for this part easily. Problem is that it only has 80 IO. So roughly 40 IO for the Z80, 35 IO for the RAM/ROM and 3 or so for VGA.

That means that there is basically no IO pins left for the expansion port keyboard cassette etc. So I make have to tack another board on to the right of this one later.

OK ... I am off to some VHDL and hope to be back in a couple of days.

-

Started VHLD Module for Video

06/10/2015 at 09:07 • 0 commentsI have been spending some time with a timing rendering Application (WaveDrom).

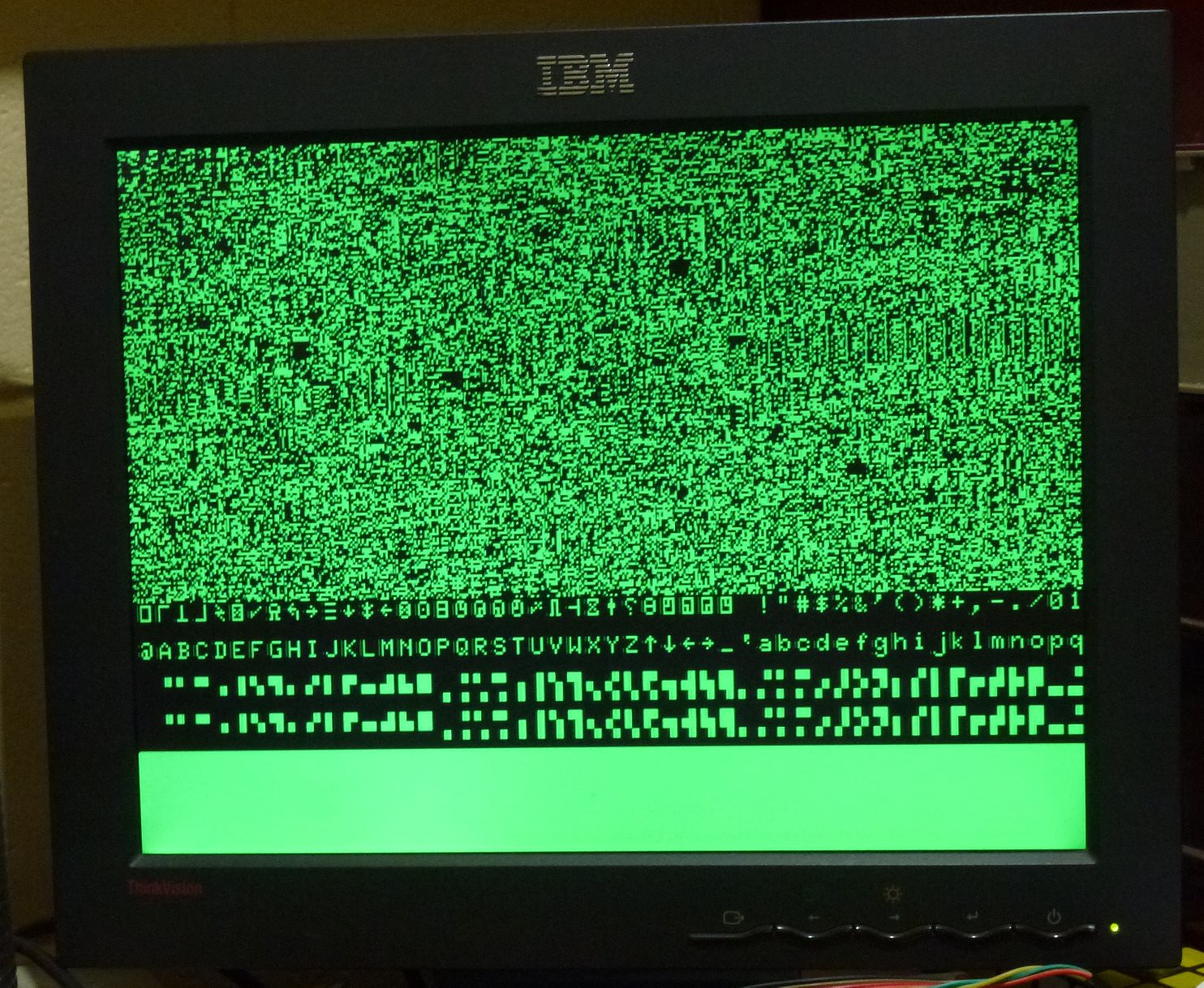

Here is a basic idea of the timing of the pixel renderer -

![]()

It is not very accurate as I can't seem to get it to do what I want yet but it does give a basic idea of where I am heading.

It looks like the memory access time will be over 80nS which is great as the FLASH is 70nS.

I am trying to separate the dot rendering part of the VHDL from the timing part so that I can use jumpers to select the output format: NTSC, PAL or VGA.

This approach will waste some registers for timing but there should be more than enough in the chip I am using.

-

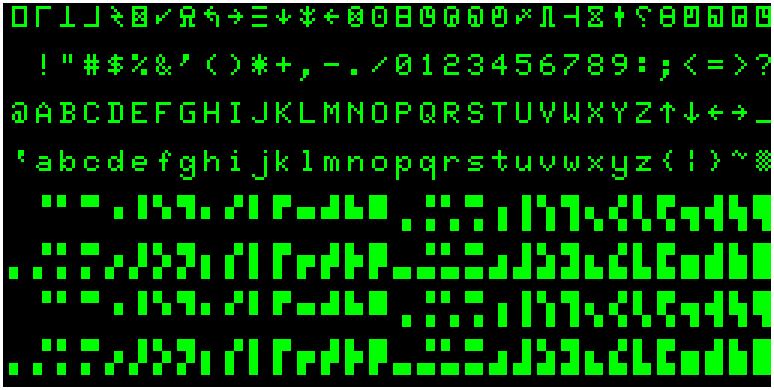

VHDL Started

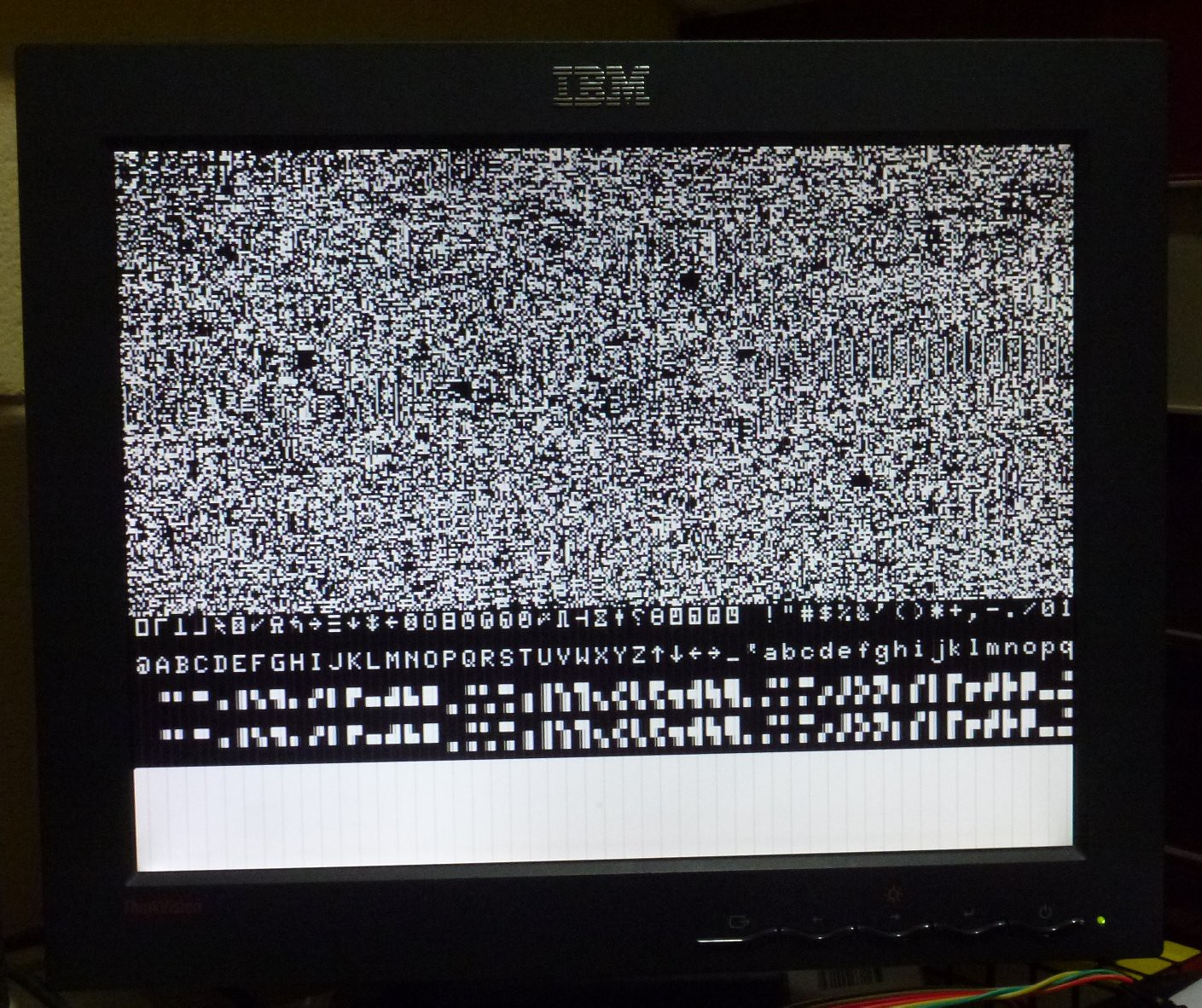

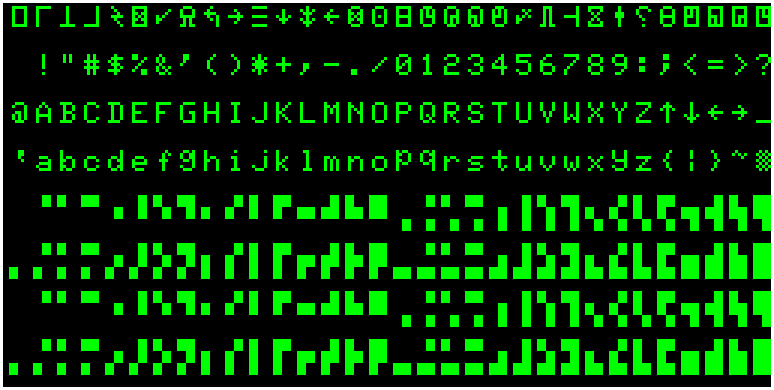

06/02/2015 at 10:06 • 2 comments![]()

Or do you prefer Green?

![]()

This is a direct dump from ROM to the screen. Most of the image is the TRS-80 BASIC ROMs.

Then there are the characters. The characters sit in 8x16 memory cells so not all of them fit on the screen because they need to go into a 6x12 cell for on-screen.

The bright area after the characters is blank ROM (FLASH).

The BASIC ROMs are occupying 12kB and after that the character ROM occupies 4kB so they fit neatly together into a 16kB block.

There is some ghosting because of timing issues. The VHDL is just something quick and dirty so that I can see roughly what it will look like. All the issues will be fixed when I properly time out (synchronise) the code.

So tomorrow I will completely re-write the VHDL. At the moment it doesn't even have a shift register. It is doing a full 128 ROM reads per character. ie reading each byte 8 times to put out a single dot each time.

Some curious things - the 70nS FLASH works fine even down to 40nS access times but gives up the ghost at 20nS (not surprisingly). The 25nS SRAM works fine at 20nS. I couldn't test it any faster because the source clock is 50MHz.

Oh yes, one other thing. The descenders ... well ... descend! Have a look.

-

Finally I Have a Character ROM Code

05/31/2015 at 12:10 • 1 commentHere's what it looks like -

The above is what it will look like on a standard 4:3 screen. The character are double spaced both horizontally and vertically.

I modified the characters so that the descenders drop further -

Below is a render of what it looks like in ROM (when it gets there).

And the code - Javascript format as I used Javascript to render it.

0x00,0x1F,0x11,0x11,0x11,0x11,0x11,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x10,0x10,0x10,0x10,0x10,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x04,0x04,0x04,0x04,0x04,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x01,0x01,0x01,0x01,0x01,0x01,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x08,0x04,0x02,0x0F,0x04,0x02,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x11,0x1B,0x15,0x1B,0x11,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x01,0x02,0x14,0x18,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x1F,0x0A,0x0A,0x1B,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x08,0x1E,0x09,0x05,0x01,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x04,0x02,0x1F,0x02,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x00,0x00,0x1F,0x00,0x00,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x04,0x04,0x15,0x0E,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x15,0x0E,0x04,0x15,0x0E,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x04,0x08,0x1F,0x08,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x1B,0x15,0x1B,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x15,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x11,0x11,0x1F,0x11,0x11,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x15,0x15,0x17,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x17,0x15,0x15,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x1D,0x15,0x15,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x15,0x15,0x1D,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x05,0x02,0x15,0x18,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x0A,0x0A,0x0A,0x0A,0x0A,0x1B,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x01,0x01,0x01,0x1F,0x01,0x01,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x11,0x0A,0x04,0x0A,0x11,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x04,0x0E,0x0E,0x04,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x10,0x08,0x04,0x00,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x1F,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x15,0x15,0x1D,0x11,0x11,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x11,0x11,0x1D,0x15,0x15,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x11,0x11,0x17,0x15,0x15,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x15,0x15,0x17,0x11,0x11,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x04,0x04,0x04,0x04,0x00,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0A,0x0A,0x0A,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0A,0x0A,0x1F,0x0A,0x1F,0x0A,0x0A,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x0F,0x14,0x0E,0x05,0x1E,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x18,0x19,0x02,0x04,0x08,0x13,0x03,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x08,0x14,0x14,0x08,0x15,0x12,0x0D,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0C,0x0C,0x08,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x02,0x04,0x08,0x08,0x08,0x04,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x08,0x04,0x02,0x02,0x02,0x04,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x15,0x0E,0x1F,0x0E,0x15,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x04,0x04,0x1F,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x0C,0x0C,0x08,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x0C,0x0C,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x01,0x02,0x04,0x08,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x13,0x15,0x19,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x0C,0x04,0x04,0x04,0x04,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x01,0x0E,0x10,0x10,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x01,0x06,0x01,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x02,0x06,0x0A,0x12,0x1F,0x02,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x10,0x1E,0x01,0x01,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x06,0x08,0x10,0x1E,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x01,0x02,0x04,0x08,0x10,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x0E,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x0F,0x01,0x02,0x0C,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x0C,0x0C,0x00,0x0C,0x0C,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0C,0x0C,0x00,0x0C,0x0C,0x08,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x02,0x04,0x08,0x10,0x08,0x04,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x1F,0x00,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x08,0x04,0x02,0x01,0x02,0x04,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x01,0x02,0x04,0x00,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x01,0x0D,0x15,0x15,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x0A,0x11,0x11,0x1F,0x11,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1E,0x09,0x09,0x0E,0x09,0x09,0x1E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x10,0x10,0x10,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1E,0x09,0x09,0x09,0x09,0x09,0x1E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x10,0x10,0x1C,0x10,0x10,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x10,0x10,0x1C,0x10,0x10,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0F,0x10,0x10,0x13,0x11,0x11,0x0F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x11,0x11,0x1F,0x11,0x11,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x04,0x04,0x04,0x04,0x04,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x01,0x01,0x01,0x01,0x01,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x12,0x14,0x18,0x14,0x12,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x10,0x10,0x10,0x10,0x10,0x10,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x1B,0x15,0x15,0x11,0x11,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x19,0x15,0x13,0x11,0x11,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x11,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1E,0x11,0x11,0x1E,0x10,0x10,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x11,0x11,0x15,0x12,0x0D,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1E,0x11,0x11,0x1E,0x14,0x12,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0E,0x11,0x10,0x0E,0x01,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x04,0x04,0x04,0x04,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x11,0x11,0x11,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x11,0x11,0x0A,0x0A,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x11,0x11,0x11,0x15,0x1B,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x11,0x0A,0x04,0x0A,0x11,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x11,0x0A,0x04,0x04,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x1F,0x01,0x02,0x04,0x08,0x10,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x0E,0x15,0x04,0x04,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x04,0x04,0x04,0x15,0x0E,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x04,0x08,0x1F,0x08,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x04,0x02,0x1F,0x02,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x06,0x06,0x04,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x0E,0x01,0x0F,0x11,0x0F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x10,0x10,0x16,0x19,0x11,0x19,0x16,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x0E,0x11,0x10,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x01,0x01,0x0D,0x13,0x11,0x13,0x0D,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x0E,0x11,0x1F,0x10,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x02,0x05,0x04,0x0E,0x04,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0D,0x13,0x13,0x0D,0x01,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x10,0x10,0x16,0x19,0x11,0x11,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x00,0x0C,0x04,0x04,0x04,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x01,0x00,0x01,0x01,0x01,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x10,0x10,0x12,0x14,0x18,0x14,0x12,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0C,0x04,0x04,0x04,0x04,0x04,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x1A,0x15,0x15,0x15,0x15,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x16,0x19,0x11,0x11,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x0E,0x11,0x11,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x16,0x19,0x11,0x19,0x16,0x10,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0D,0x13,0x11,0x13,0x0D,0x01,0x01,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x16,0x19,0x10,0x10,0x10,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x0F,0x10,0x0E,0x01,0x1E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x04,0x1F,0x04,0x04,0x05,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x11,0x11,0x11,0x13,0x0D,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x11,0x11,0x11,0x0A,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x11,0x11,0x15,0x15,0x0A,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x11,0x0A,0x04,0x0A,0x11,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x11,0x11,0x11,0x0F,0x01,0x11,0x0E,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x1F,0x02,0x04,0x08,0x1F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x02,0x04,0x04,0x08,0x04,0x04,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x04,0x04,0x04,0x00,0x04,0x04,0x04,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x08,0x04,0x04,0x02,0x04,0x04,0x08,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x08,0x15,0x02,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x0A,0x15,0x0A,0x15,0x0A,0x15,0x0A,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x00,0x00,0x00,0x00,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x07,0x07,0x07,0x07,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x38,0x38,0x38,0x38,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00, 0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x3F,0x00,0x00,0x00,0x00

That's it for today!

-

One Day Nothing Achieved

05/31/2015 at 08:04 • 1 commentWell today has been a day of frustration.

I started by picking up the Xilinx board to use as a FLASH programmer. I did have it working at one stage and then started to upgrade the Arduino code to add features.

I couldn't get the code to work no matter what I tried. I then checked the VHDL, the connections between the Arduino and the FPGA and the constraints but no good.

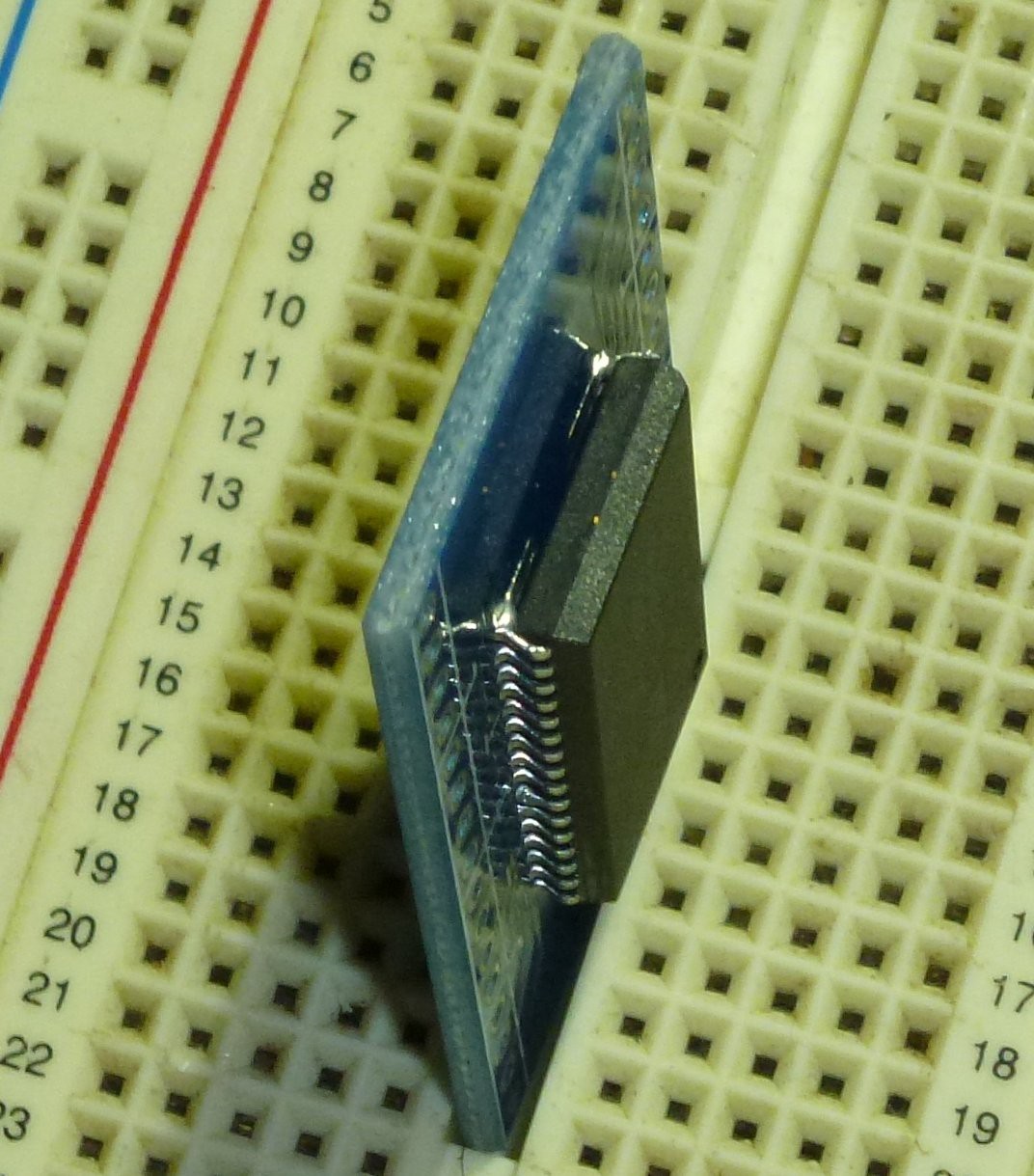

It turned out that the cheap ZIF socket that I got from China was the issue. The pins recede into the housing when you go to plug it into a socket. I soldered pin headers to it - fixed.

Since then (the rest of the day) I have been head down in Hex trying to nut out a character ROM.

I have a ROM (that doesn't include graphics) but it doesn't have the proper descenders on lower case. It is also in a 7 x 8 matrix when it should be 5x7. The actual char cell is 5x7 character in a 6x12 cell. I can add graphics easily so that is not an issue.

I spent hours searching the net for a character ROM image. I found heaps of 8x8 and 8x12 fonts made for a modern systems like windows but not the original. I downloaded several emulators but they all use an 8x12 font and not 6x12.

In reality I can just make the cells 8x8 or 8x12 in hardware but I want to stay with the original specs.

I want to make the cells 6x12 just like the original with 5x8 or 5x9 characters (with descenders) and 6x12 graphics. I also want to just put the graphics in ROM with the characters rather than worry about different timings for ROM characters and combinational logic for graphics.

The solution is to get the facts from the source so I need to know the part number of the chip that generated the characters with descenders and just look up the spec sheet! But dammit, I don't even know the part number.

Now rolling head on keyboard ...klklklklklklklklklklklkliopreeee b,kero

-

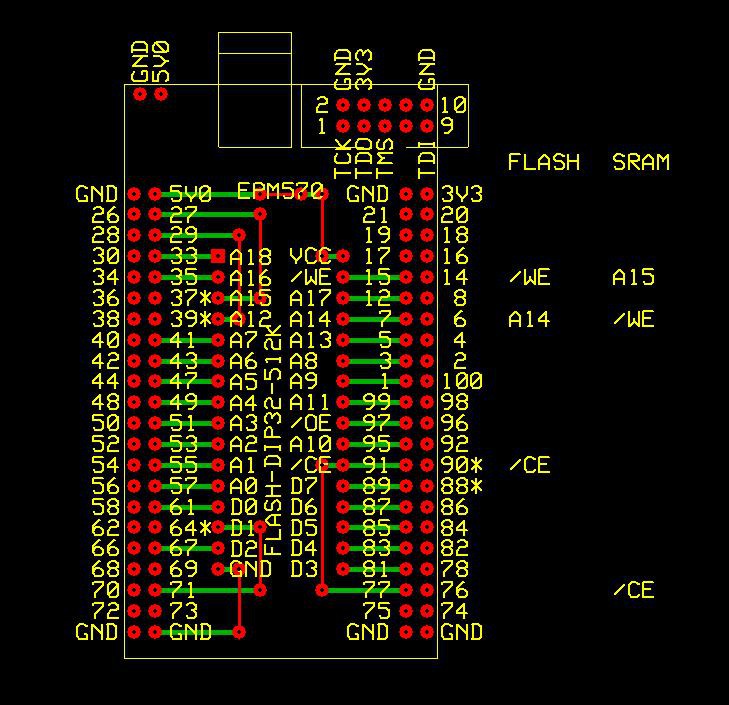

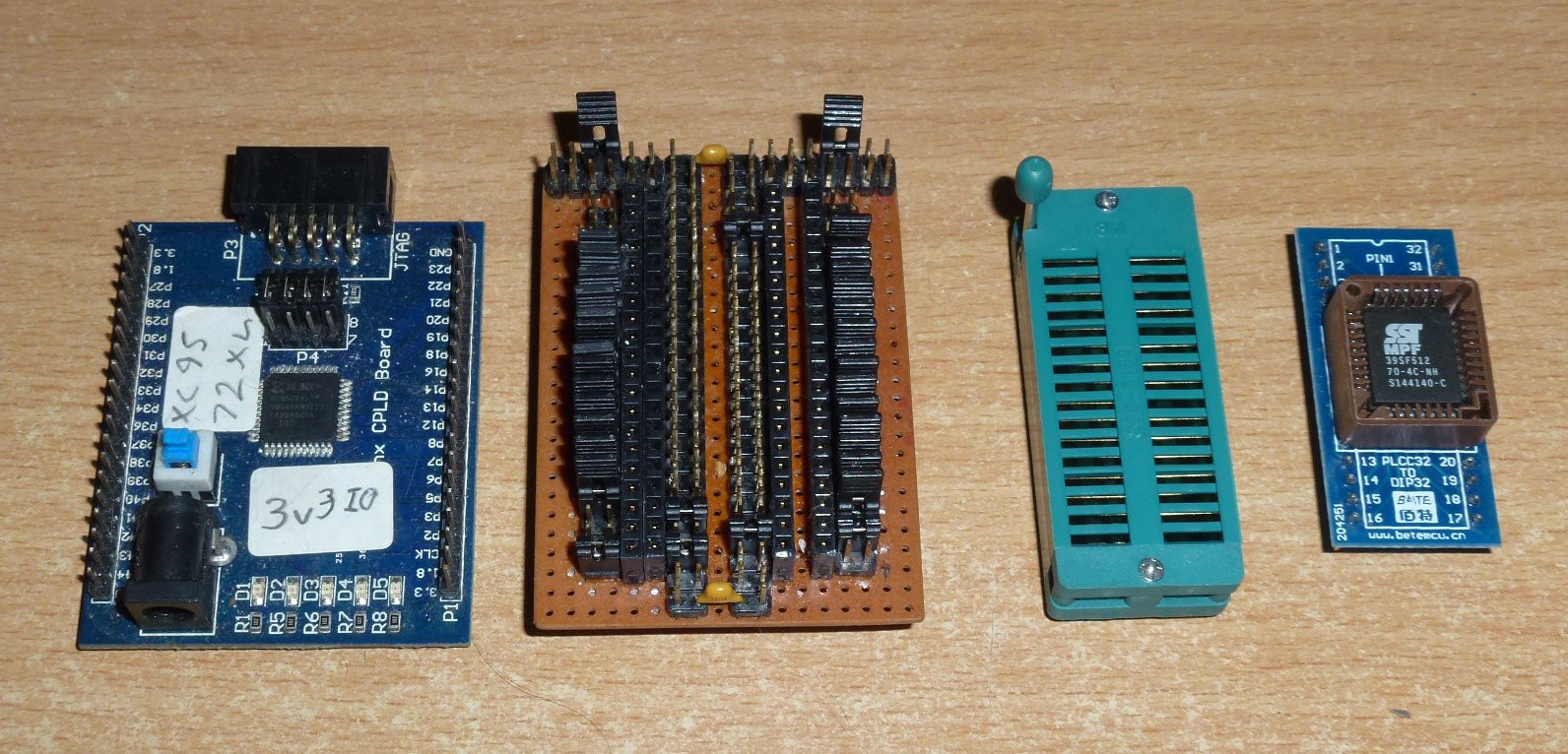

Adding FLASH and SRAM

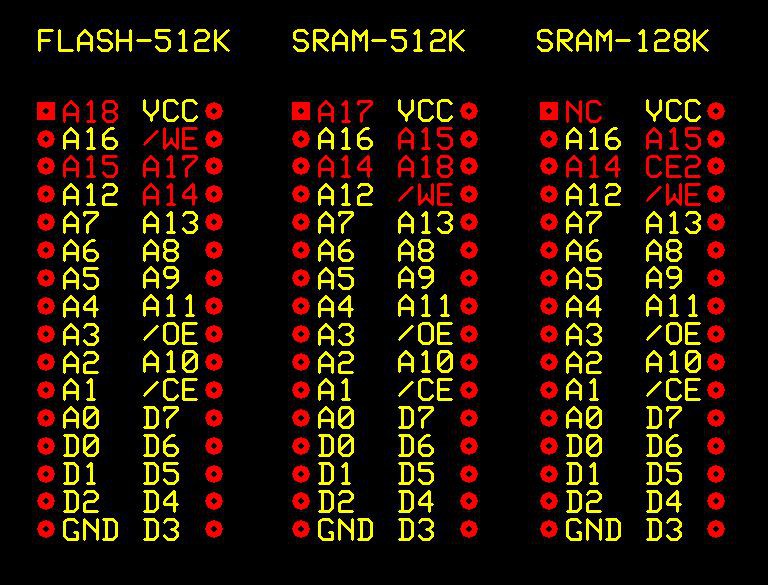

05/28/2015 at 22:58 • 2 commentsThere are some slight differences in the layouts of 32 Pin DIP SRAM and FLASH.

Most of the differences are not a problem. For SRAM it doesn't matter if you mix up the Address or Data pins as long as Address and Data pins are grouped separately. ie It doesn't where the data goes as long as it comes back from the same place. So I ignored most of that and just assumed the Address pinout of the FLASH because that does matter.

Apart from that there is the issue of /WE and one address pin being swapped comaring SRAM and FLASH. I could have just swapped these pins on the SRAM board but I left it as an exercise in VHDL to fix it with code.

I decide to connect all the pins except /CE in parallel to save pins on the CPLD.

The SRAM is 512KBytes 25nS and the FLASH is 70nS.

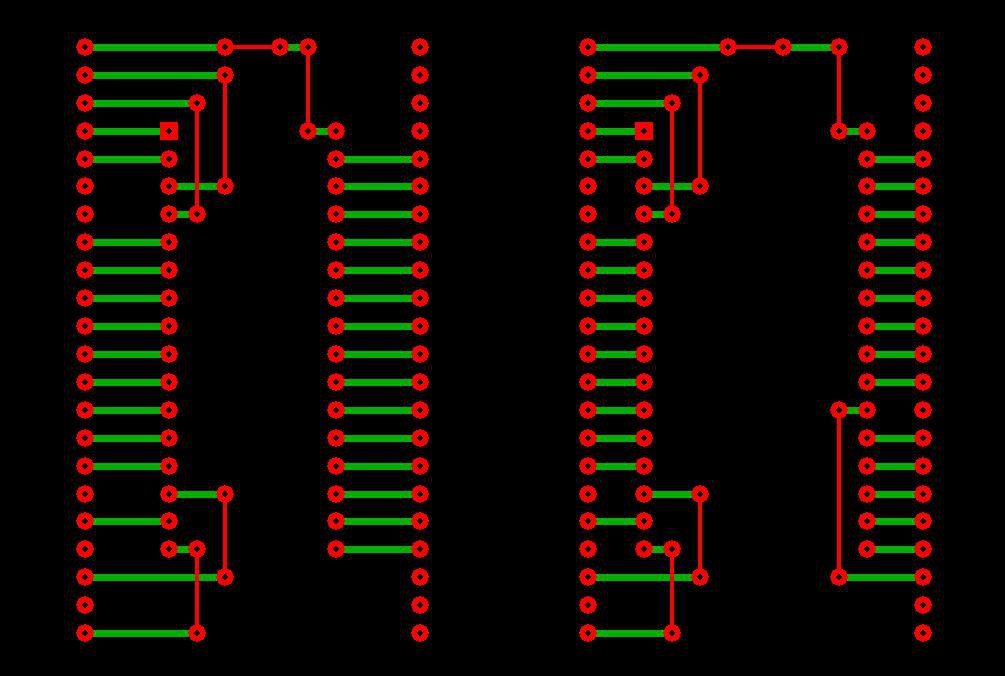

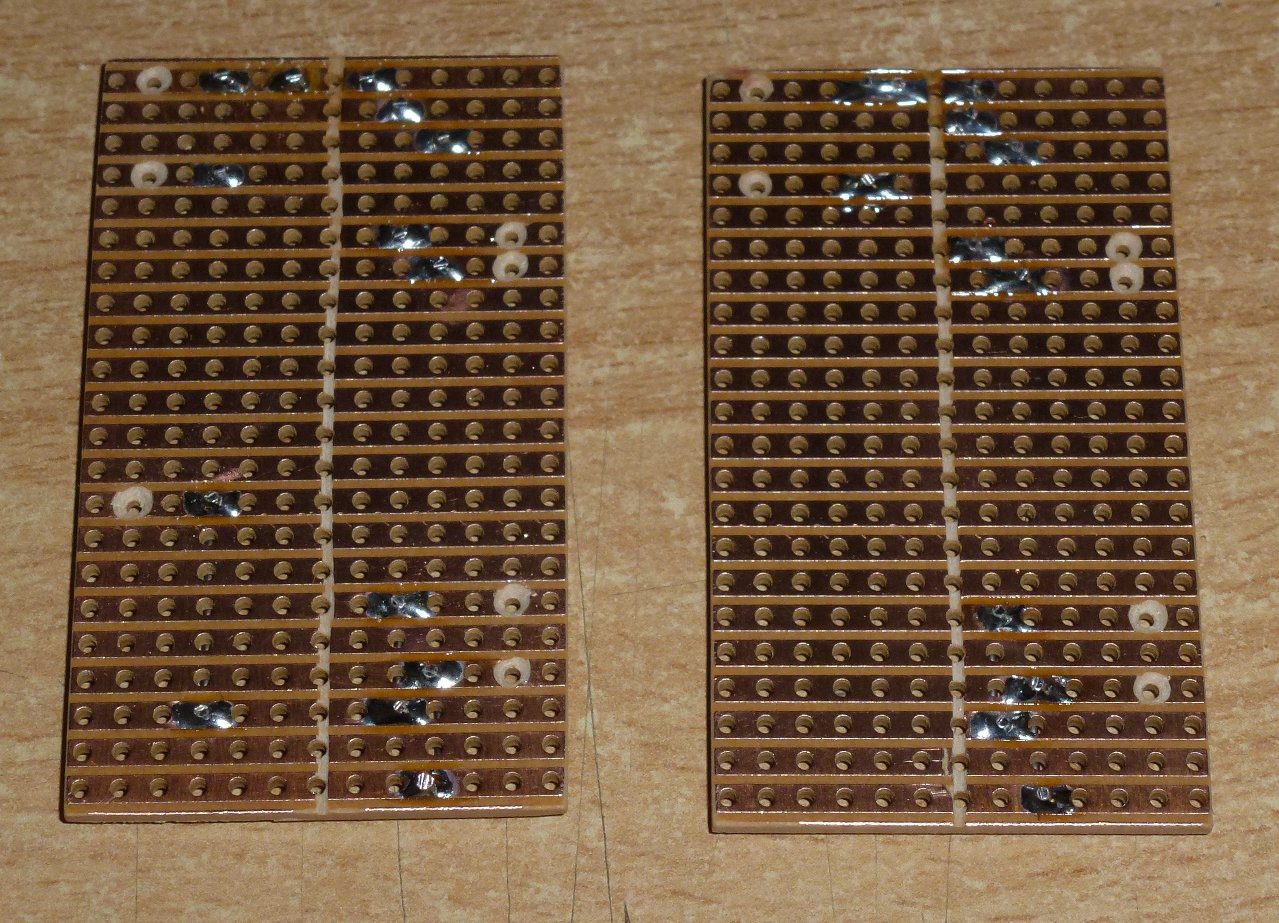

Here are the equivalent PCB layouts (FLASH on left, SRAM on right) -

And dreaded Vero layout (SRAM on left, FLASH on right) -

![]()

![]()

They all connect together this way -

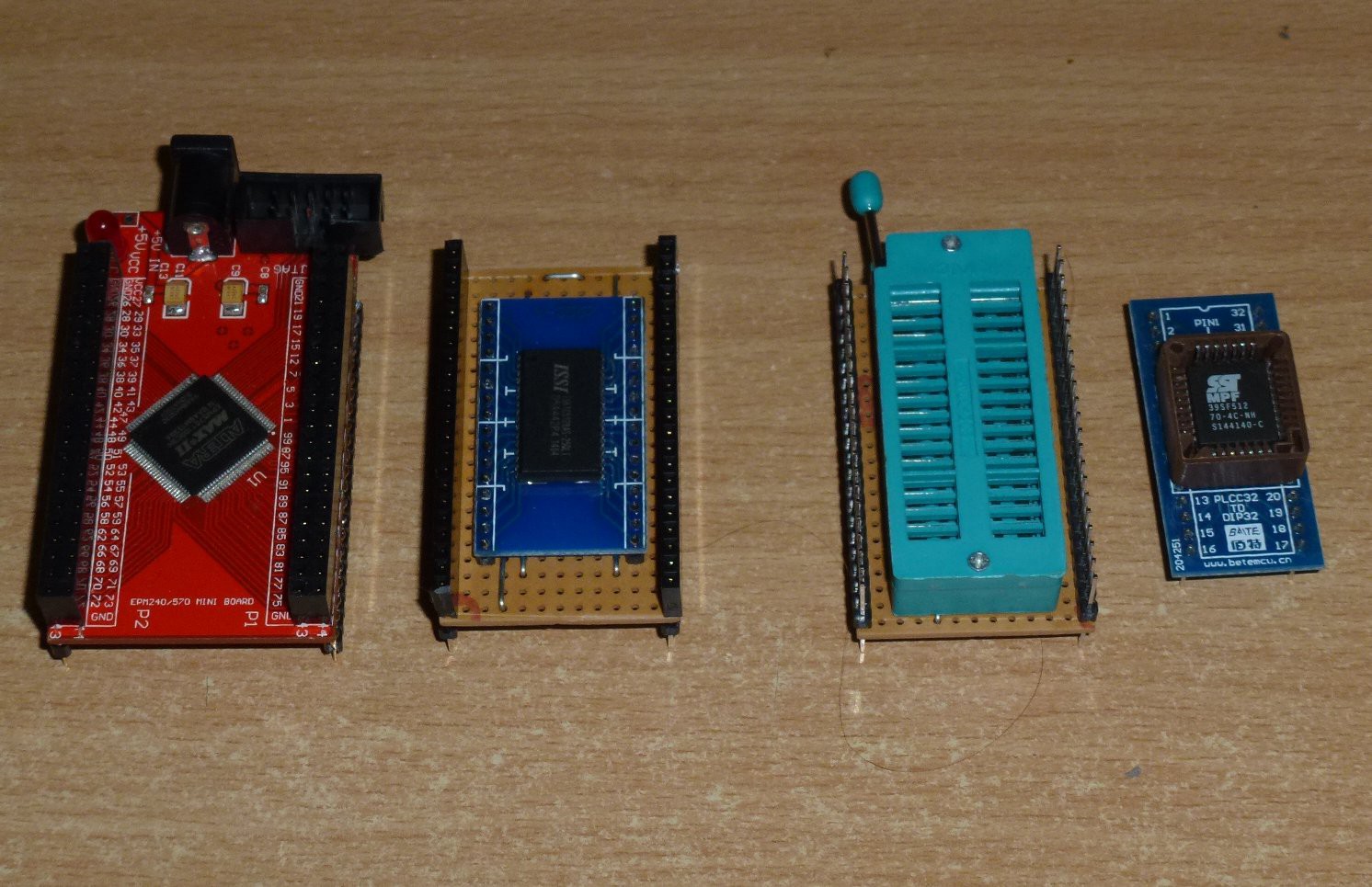

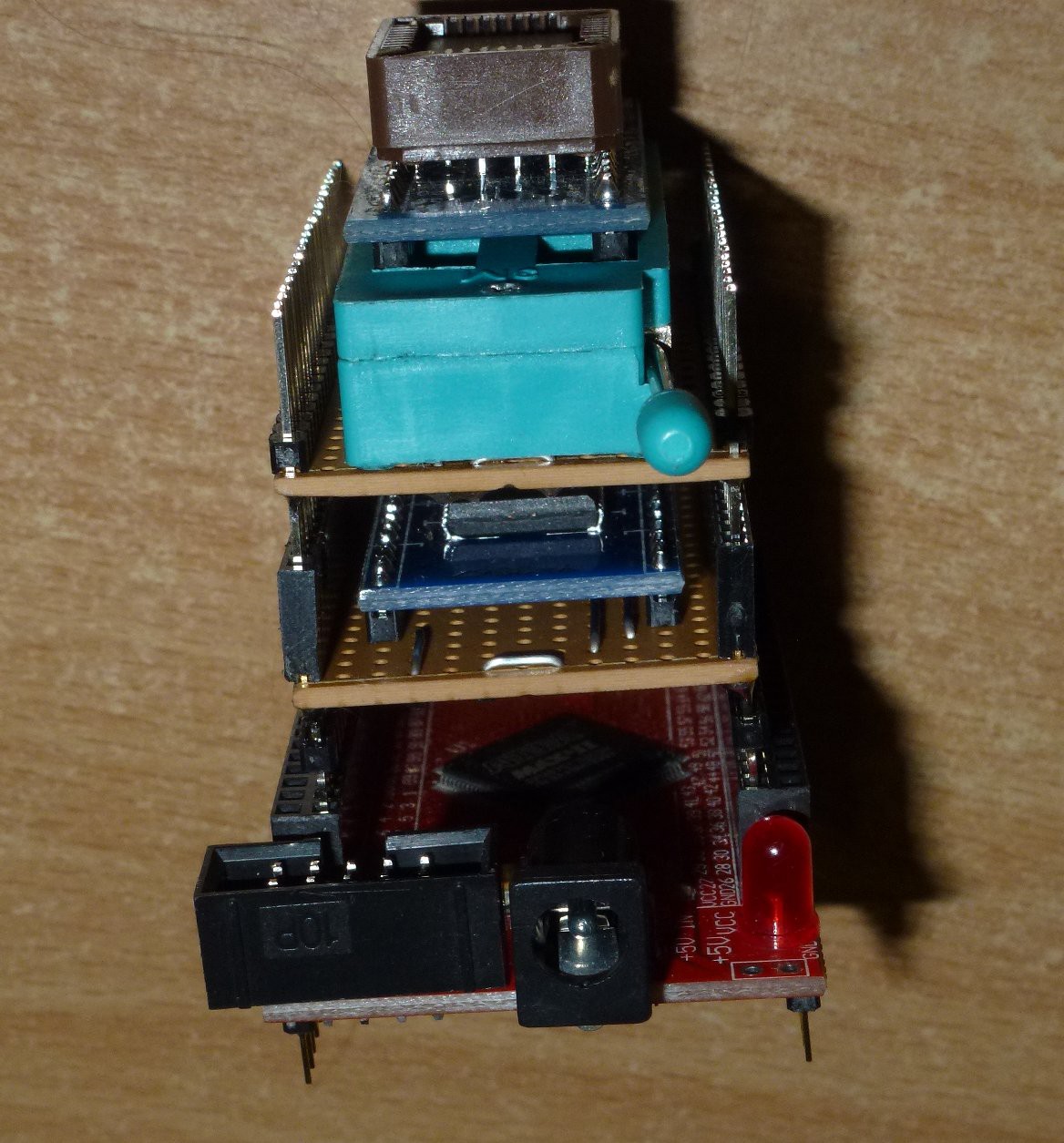

Assembling the bits -

![]()

![]()

![]()

![]()

To program the FLASH I will be using a stack made in a similar way. It connects to an Arduino.

![]()

![]()

The programmer was made for a 64KB FLASH so I have to go and rewrite the Arduino code and VHDL (It's a Xilinx chip) so that it can program larger FLASH - up to 512KB.

Then I have to write the VHDL for the Altera development board - I haven't even started this yet.

Next steps are - Write VHDL for VGA output. Dual port the FLASH and SRAM with the CPU bus having priority (like it was in the TRS80). Add the CPU and see the 'READY>' prompt (milestone 1 - Level Up).

Then convert to time division bus multiplexing. After that I can start to worry about I/O such as keyboard and the dreaded pin count. Will it fit in a 100 Pin CPLD???

OK, I am off to do what I enjoy more and play with some code.

-

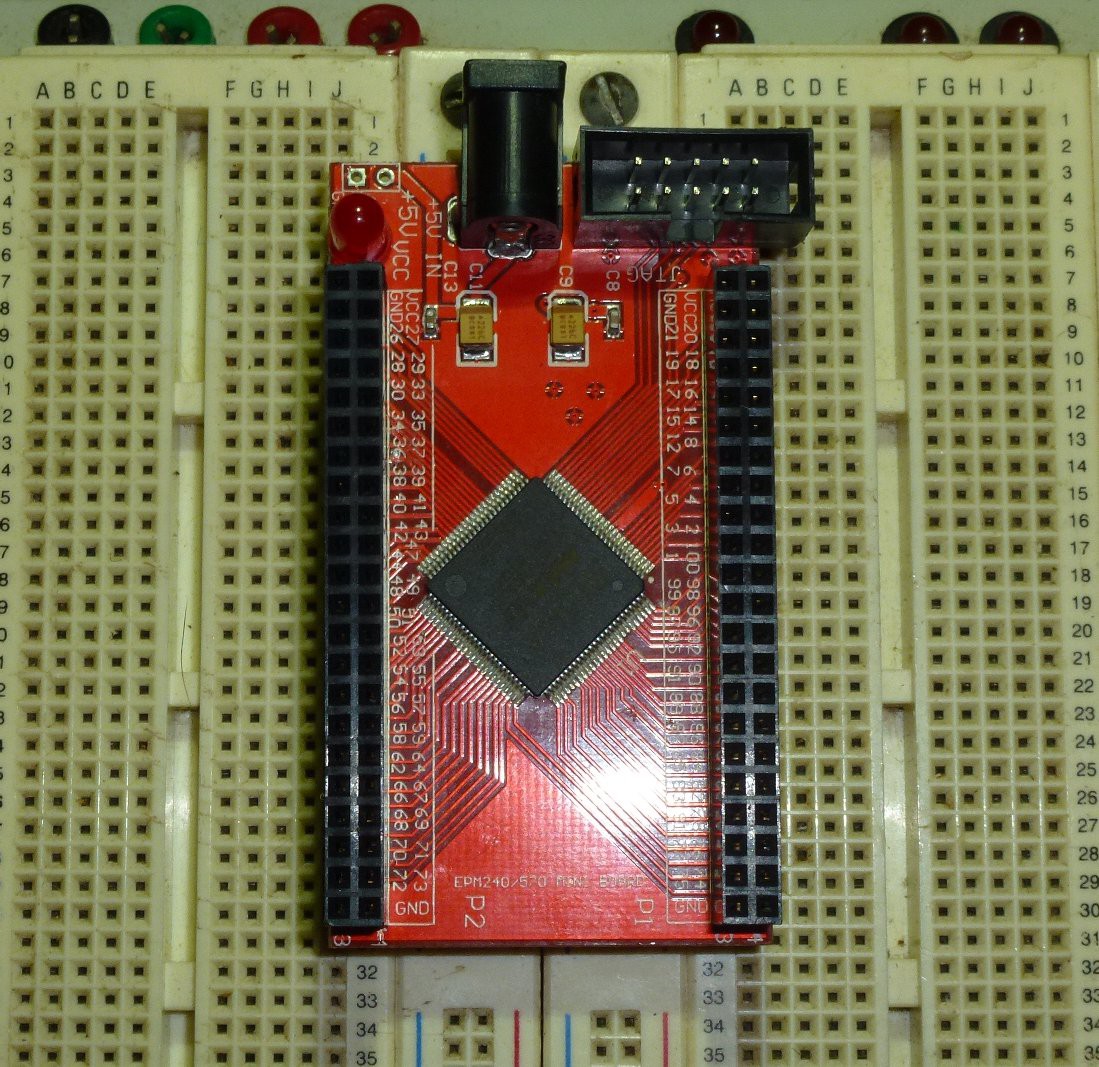

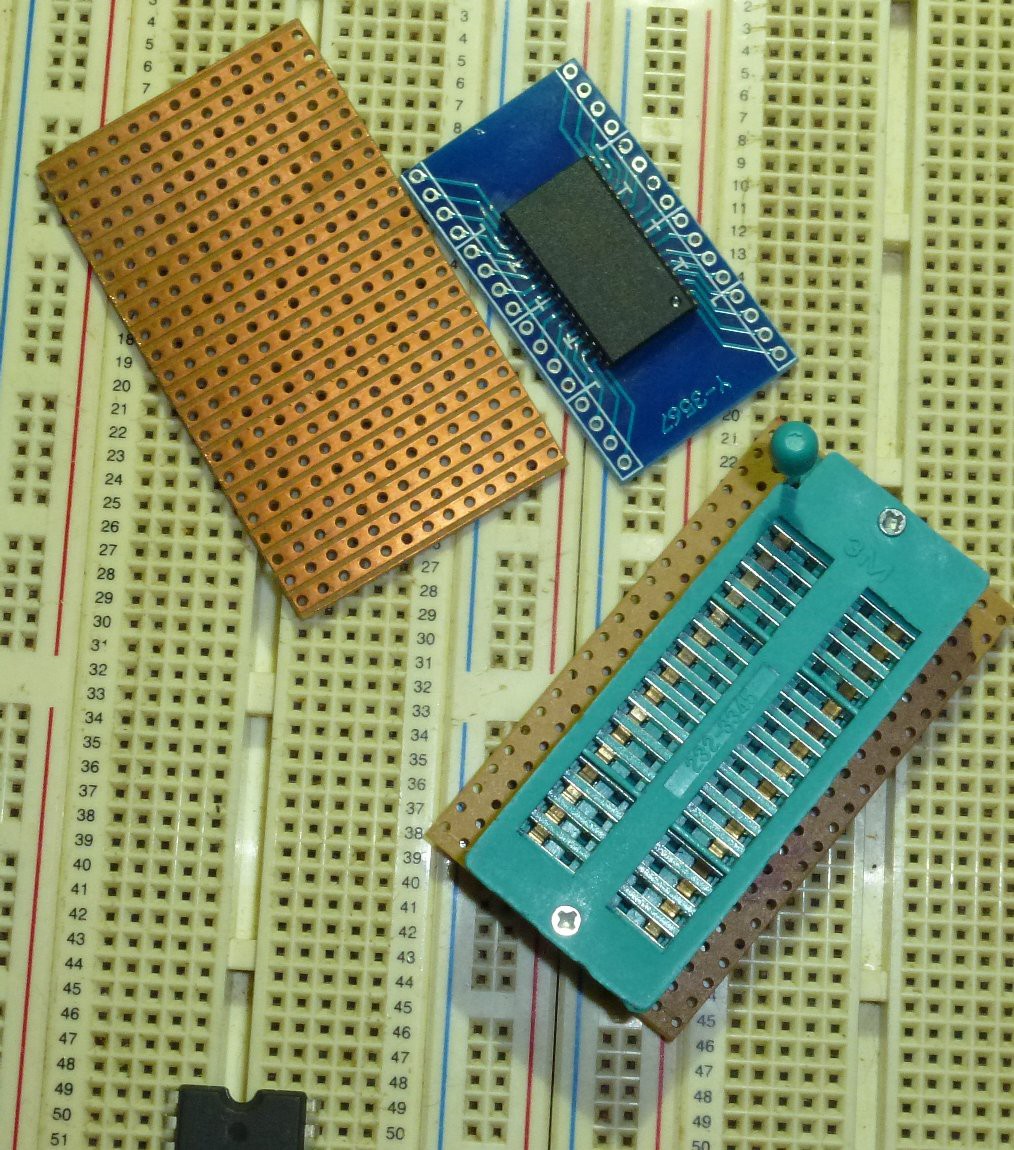

Preparing for Breadboarding

05/27/2015 at 09:30 • 0 commentsI decided to make another 'stack' with 'duino like plugin shield boards because I want to use this same prototyping platform for anther project as well and that project requires SRAM access up to 50MHz.

The general idea is to have half the CPLD boards pins go to the breadboard for slow bus speeds and the other half stack on top for the faster buses. I'm not confident at all the the higher speed buses will work on a breadboard.

So here is the start - the CPLD plugged into a breadboard.

![]()

Here's the bottom of the board -

![]()

I have put dual row pin header sockets on the top and a single rows of pins on the bottom for the breadboard. I also modified it to send 5V to the plugin boards instead if 3V3.

After I test that it works, I will swap the 50MHz oscillator over for a 100MHz oscillator.

I don't have any DIP SRAM so I bent the pins of a SOP chip in, to fit it on a TSOP to DIP adaptor -

![]()

Next I have to put SRAM and FLASH onto some boards made from Vero that plug into the top of the CPLD board.

![]()

The SRAM is 128KB.

I have to dual port both the SRAM and FLASH. The SRAM needs dual porting because it has the video RAM in it and the the FLASH need dual porting because it has the character ROM in it ... to save chip count. This is going to be a challenge for me as I am a beginner at VHDL and the Z80 is non-synchronous.

Hacker404

Hacker404