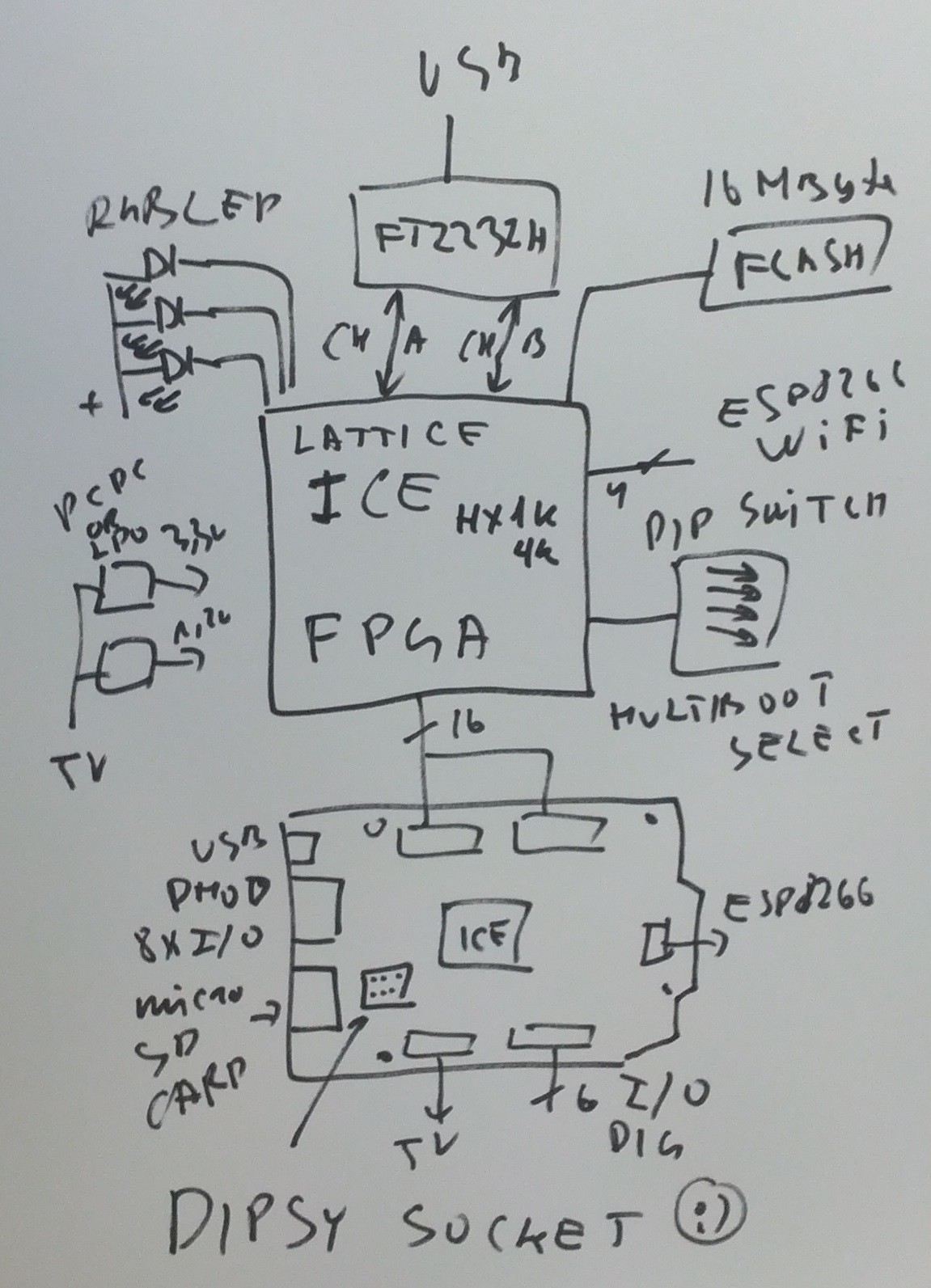

System Diagram

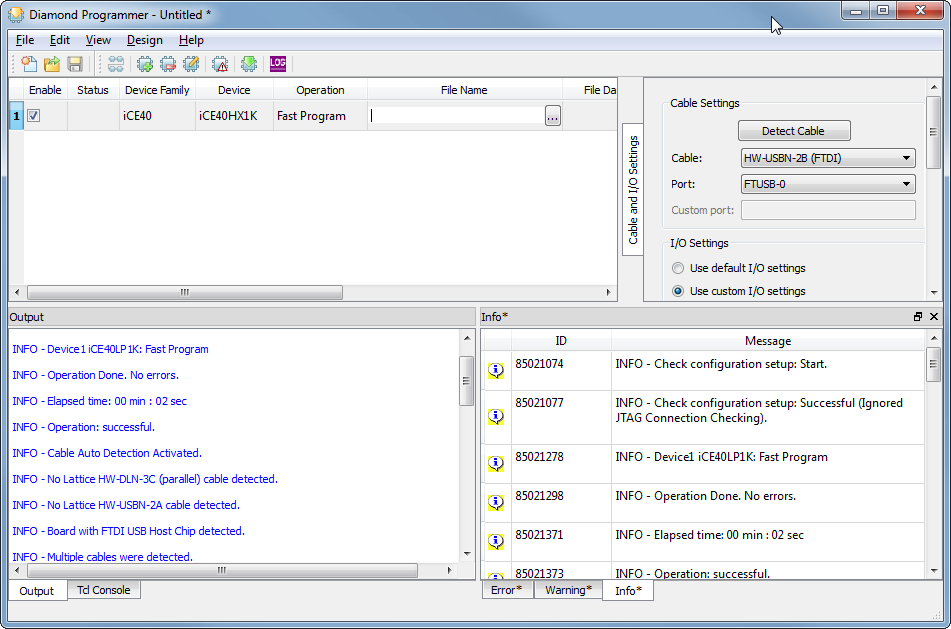

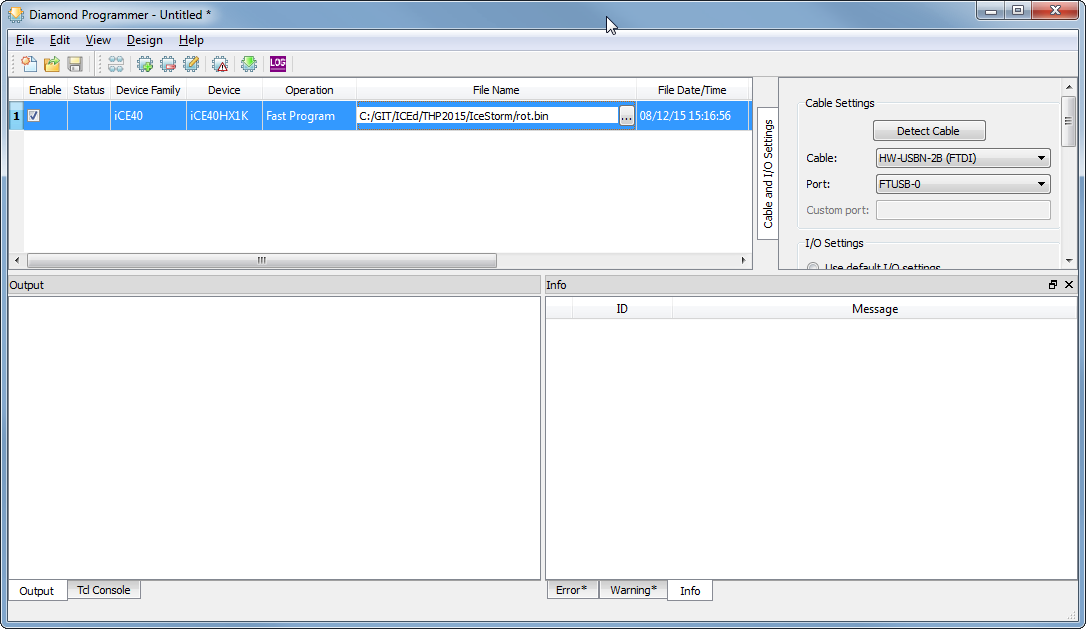

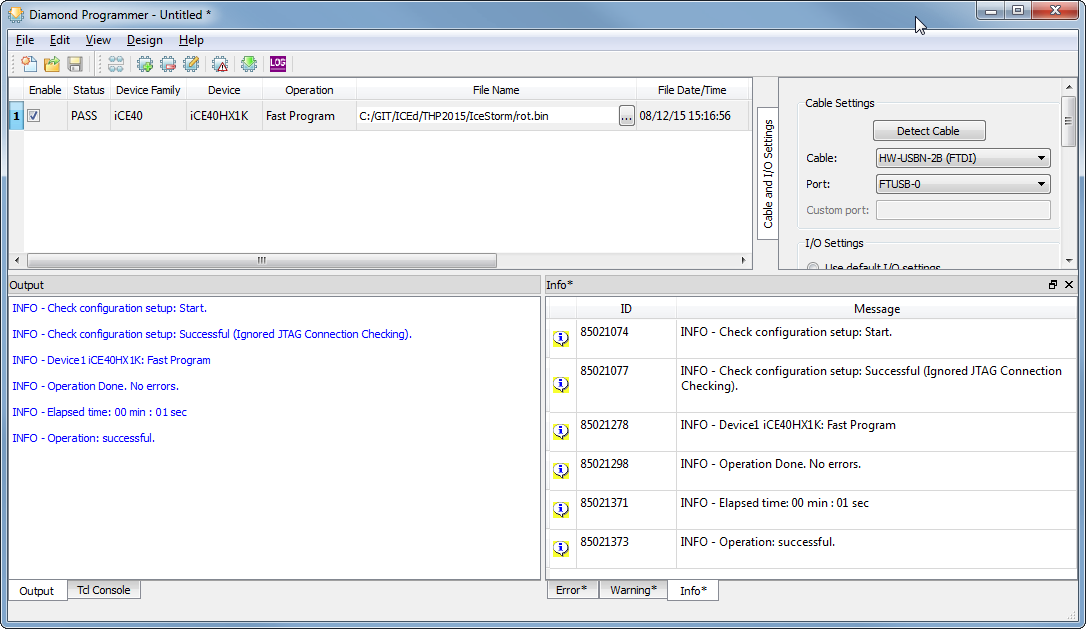

- Directly supported by Lattice Development tools

- Supported by open-source FPGA tools, project "icestorm"

- FPGA pinout mostly compatible to Lattice iceStick development board

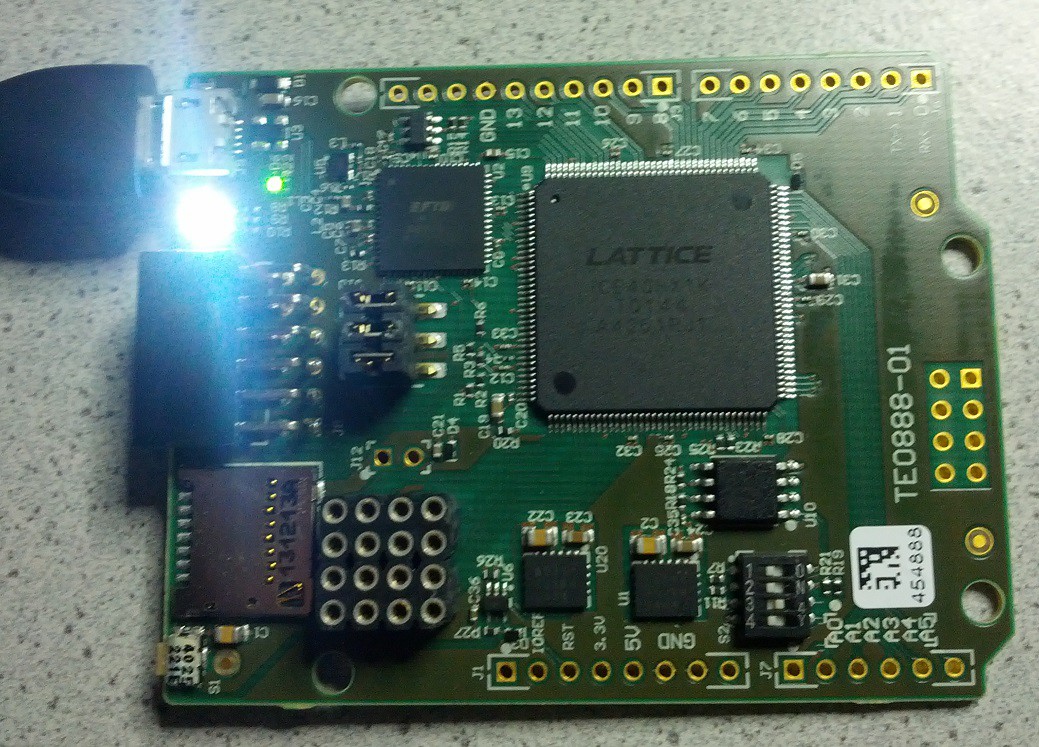

- 1 Digilent Pmod(tm) slot

- micro SD Card socket

- 16MByte SPI NOR Flash

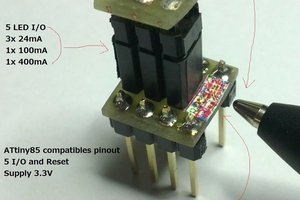

- DIPSY Socket for programming custom DIPSY's

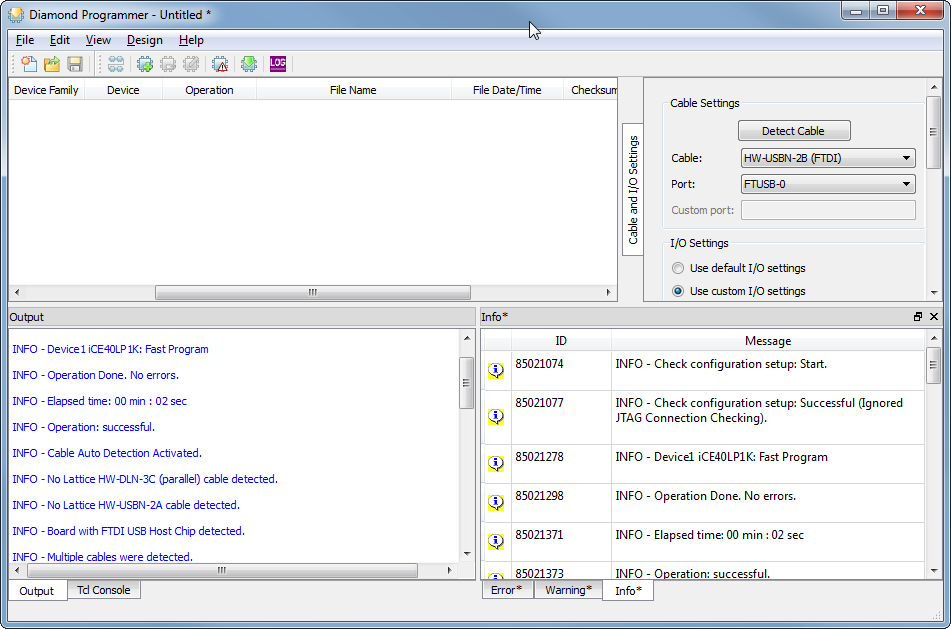

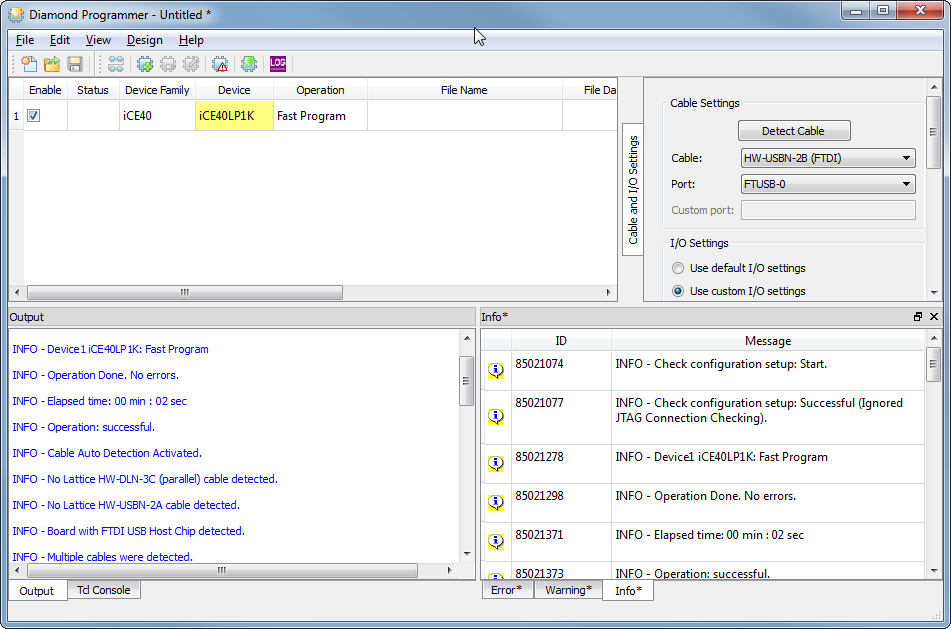

- FT2232H, use for Flash Programming or FPGA download to RAM

- USB UART on FTDI Channel B

- Optionally powered from USB

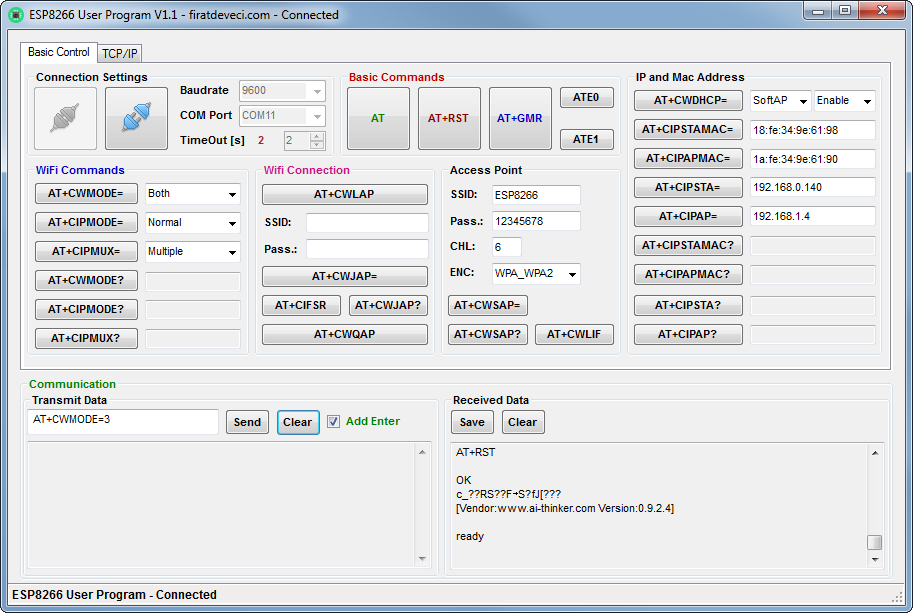

- 8 pin Header for ESP8266 WiFi Module

Licenses

- CERN OHL

- Hardware design

Additional licenses for open-source FPGA toolchain (if used):

Antti Lukats

Antti Lukats

Paula

Paula

bobricius

bobricius

adesh manhar ramkissoon

adesh manhar ramkissoon

I need 3 for my project, when and how much will it cost?